当前位置:网站首页>Clock switching with multiple relationship

Clock switching with multiple relationship

2022-07-05 15:41:00 【Don't want to have PE class】

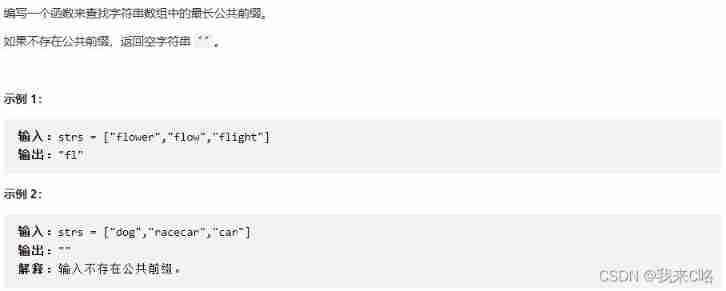

Title Description :

There are two synchronized frequency doubling clocks clk0 clk1, It is known that clk0 yes clk1 Second harmonic generation of , Now we need to design a switching circuit ,sel Choose when to switch , No burrs are required .

Explain :

The circuit diagram of switching the clock directly using the selection logic is shown below .

Suppose the clock selects the signal sel_clk1 It is asynchronous with both clocks , Then the clock switching time is arbitrary . Suppose the clock consists of clk1 Switch to clk2, And the switching time is clk1 When the output level is high , At this time, switching the clock immediately will cause burrs in the output clock (glitch). The waveform diagram is as follows :

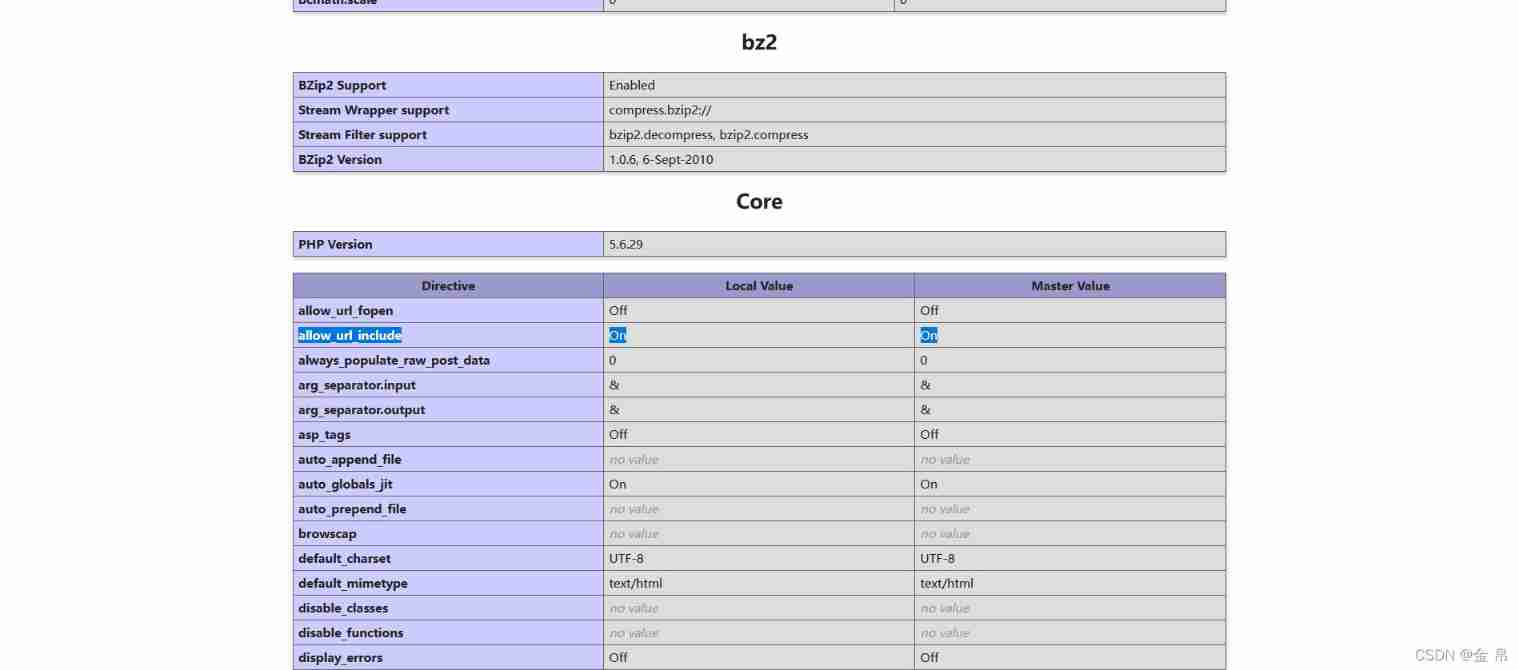

The following figure shows the solution to prevent burrs in the clock switch output of the multiple of the source clock . Insert a negative edge trigger in the selected path of each clock source D trigger . Sampling selection control at the falling edge of the clock (SELECT), And enable the selection only after disabling the other clocks first (SELECT), Can provide excellent output protection :

The following is a simple explanation of this circuit :

When SELECT by 0 when , obvious CLK1 That part of the path to the output is invalid , Just look at the lower half of the circuit , stay CLK0 Falling edge sampling SELECT( After reverse ) The signal , And CLK0 Output after phase and ; When SELECT by 1 when , Similarly, the upper half of the circuit is effective ;

What needs to be analyzed is when SELECT When switching at any time , Whether there will be burrs in the output ?

First SELECT by 0, That is to say CLK0 The falling edge of the sampling register SELECT( After reverse ) Signals and CLK0 Meet each other , Output clock is CLK0;

When in the picture SELECT Change from low level to high level , It's not time for CLK0 The falling edge of , The output of the register will always be high (SELECT For before 0, Take instead 1), When they arrive in CLK0 The falling edge of the moment , Sample to SELECT High level , that !SELECT by 0, That is, the lower half of the circuit is invalid , The upper half of the circuit is effective , You need to wait until CLK1 Falling edge sampling SELECT value , Before that , Output not yet CLK0, arrive CLK1 After the falling edge of , The output becomes CLK1 and SELECT Of and , That is to say CLK1. The figure is visible , The output clock switches perfectly , There is no chopper signal or burr .

Register the selection signal on the falling edge of the clock (SELECT) It can ensure that the output terminal will not change when any clock is at high level , Clock output to prevent chopping ( It means falling edge deposit , It can ensure that the output remains unchanged before the falling edge comes , This will not cut off the current clock ). The feedback from the selection of one clock to another enables the switch to wait for the current clock to be deselected before starting to propagate the next clock , To avoid any burrs ( It means even now SELECT Suddenly changed , You must also wait until the falling edge of the current clock arrives to invalidate the current clock , During this period of time, burrs are avoided (glitch));

There are three timing paths in the circuit that need special consideration

1、 SELECT The control signal triggers either of the two negative edges ;

2、DFF0 Output to DFF1 The input of ;

3、DFF1 Of output to DFF0 The input of .

If the signal on any of the three paths changes simultaneously with the capture edge of the target trigger clock , Then the output of the register is likely to become metastable , This means that it may enter the ideal 0 and 1 The state between the two .

The above understanding draws on the experience of two big men , I just cleaned up , It is integrated with my understanding :

1.( Numbers IC Design )5.4 Clock switching - You know (zhihu.com)

2. Burrs in clock switching (glitch)_dxz44444 The blog of -CSDN Blog _ Clock burr

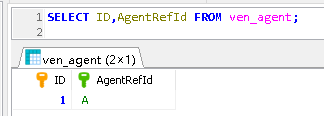

The complete code is as follows :

In this code , Pay attention to which clock is used ;

`timescale 1ns/1ns

module huawei6(

input wire clk0 ,

input wire clk1 ,

input wire rst ,

input wire sel ,

output reg clk_out

);

//*************code***********//

reg q0;

reg q1;

[email protected](negedge clk0 or negedge rst)

if(rst == 1'b0)

q0 <= 1'b0;

else

q0 <= ~sel & ~q1;

[email protected](negedge clk1 or negedge rst)

if(rst == 1'b0)

q1 <= 1'b0;

else

q1 <= sel & ~q0;

[email protected](*)

if(rst == 1'b0)

clk_out <= 1'b0;

else

clk_out <= (q0 & clk0)|(q1 & clk1);

//*************code***********//

endmodule边栏推荐

- wyt 。。

- Lesson 4 knowledge summary

- 21.[STM32]I2C协议弄不懂,深挖时序图带你编写底层驱动

- MySQL5.7的JSON基本操作

- Optional parameters in the for loop

- Data communication foundation - Ethernet port mirroring and link aggregation

- Nine hours, nine people, nine doors problem solving Report

- go学习 ------jwt的相关知识

- Ctfshow web entry explosion

- The computer is busy, and the update is a little slow

猜你喜欢

Common redis data types and application scenarios

No one consults when doing research and does not communicate with students. UNC assistant professor has a two-year history of teaching struggle

Number protection AXB function! (essence)

Optional parameters in the for loop

Ctfshow web entry information collection

Common PHP interview questions (1) (written PHP interview questions)

I include of spring and Autumn

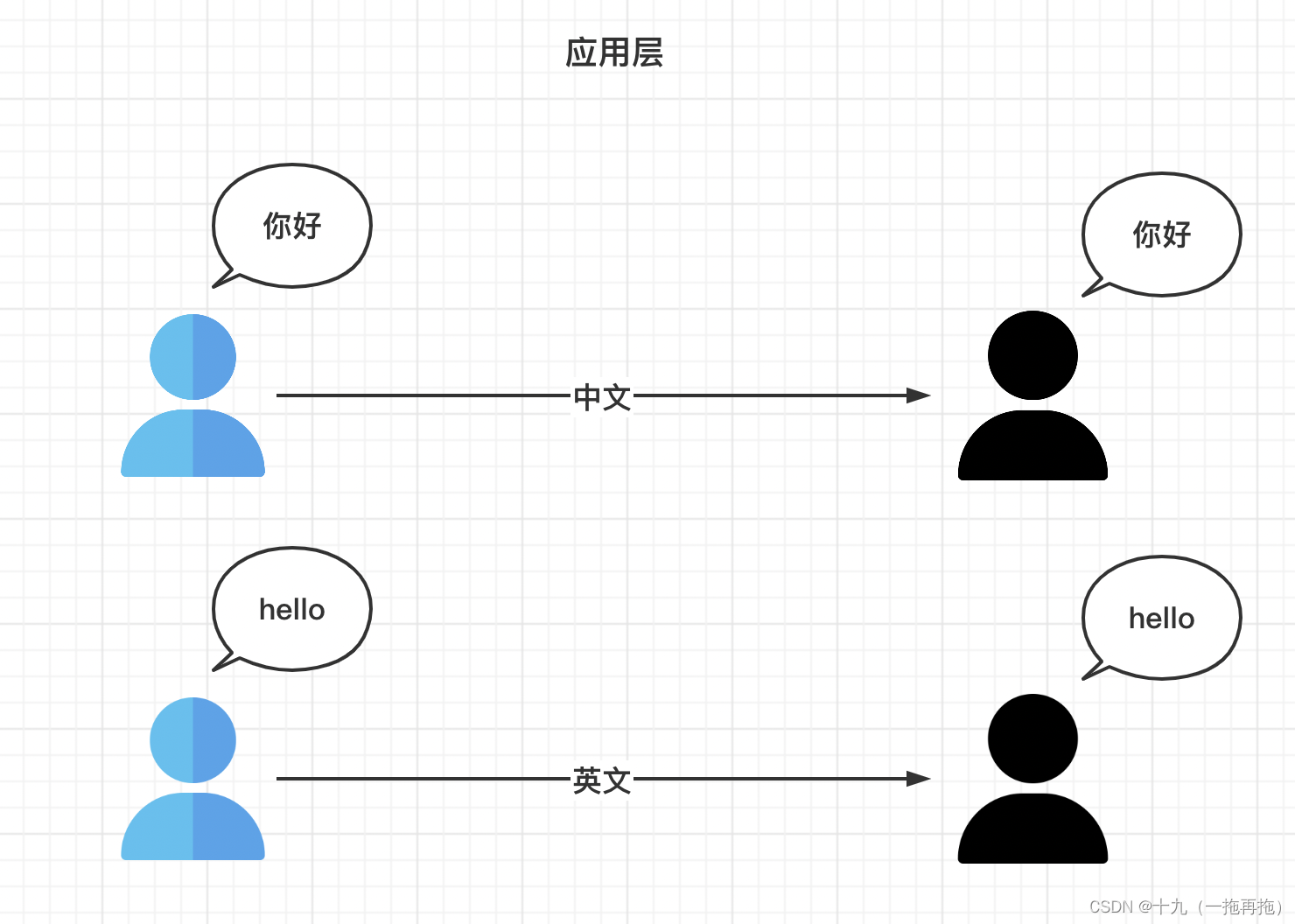

OSI seven layer model

MySQL giant pit: update updates should be judged with caution by affecting the number of rows!!!

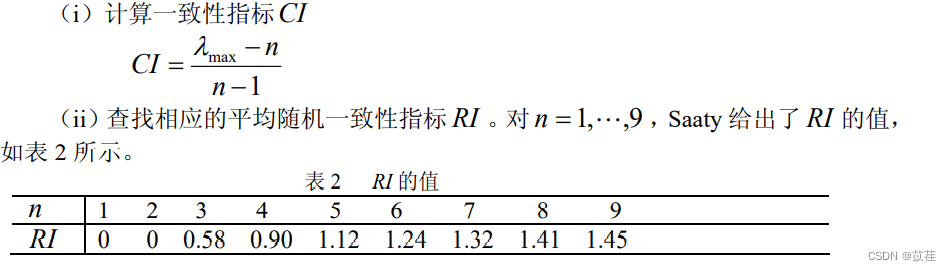

Analytic hierarchy process of mathematical modeling (including Matlab code)

随机推荐

21.[STM32]I2C协议弄不懂,深挖时序图带你编写底层驱动

wxml2canvas

Bugku's eyes are not real

Write a go program with vscode in one article

Where is the operation of convertible bond renewal? Is it safer and more reliable to open an account

Information collection of penetration test

CSRF, XSS science popularization and defense

ionic cordova项目修改插件

swiper. JS to achieve barrage effect

Basic JSON operations of MySQL 5.7

六种常用事务解决方案,你方唱罢,我登场(没有最好只有更好)

具有倍数关系的时钟切换

Install PHP extension spoole

go语言编程规范梳理总结

Reproduce ThinkPHP 2 X Arbitrary Code Execution Vulnerability

Optional parameters in the for loop

JS knowledge points-01

The difference between SQL Server char nchar varchar and nvarchar

lv_ font_ Conv offline conversion

Analytic hierarchy process of mathematical modeling (including Matlab code)