当前位置:网站首页>verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第七章)

verilog学习|《Verilog数字系统设计教程》夏宇闻 第三版思考题答案(第七章)

2022-08-02 14:02:00 【驚蟄_】

《Verilog数字系统设计教程》夏宇闻 第三版思考题

答案合集 : Verilog学习系列 第三部分

1.为什么在多模块调试的情况下$ monitor需要配合$ monitoron和 $monitoroff来工作?

$ monitoron和 $ monitoroff 任务的作用是通过打开和关闭监控标志来控制监控任务$ monitor的启动和停止,这样使得程序员可以很容易地控制$ monitor何时发生。$ monitoron则用于打开监控标志,启动监控任务$ monitor 。通常在通过调用$ monitoron来启动$ monitor时不管$ monitor参数列表中的值是否发生改变,总是立刻输出显示当前时刻参数列表中的值,这用于在监控的初始时刻设定初始比较值。在默认情况下,控制标志在仿真的起始时刻就已经打开了。在多模式调试的情况下,许多模块中都调用了$ monitor, 因为任何时刻只能用一个$ monitor起作用,因此需配合$ monitoron与$ monitoroff使用,把需要监视的模块用$ monitor打开,在监视完毕后及时用$ monitoroff关闭,以便把$monitor 让给其他模块使用。.

2.请用$random配合求模运算编写:

(1)用于测试的跳变沿抖动为周期1/10的时钟波形。

(2)随机出现的脉宽随机的窄脉冲。

module random_pulse(dout);

output [9:0] dout;

reg [9:0] dout;

integer delay;

initial

begin

#10 dout = 0;

for(k=0;k<100;K=K+1)

begin

delay = {

$random}%10;

#delay dout = 1;

#delay dout = 0;

end

end

endmodule

3.Verilog的编译预处理与C语言的编译预处理有什么不同?

Verilog的编译预处理,在编译处理命令之前要以 ‘ ` ’ 开头

4. 请仔细阐述 `timescale编译预处理的作用?

`timescale命令用来说明跟在该命令后的模块的时间单位和时间精度。使用 'timescale命令可以在同一个设计里包含采用了不同的时间单位的模块。

5.不同`timescale定义的多模块仿真测试时需要注意什么?

如果在同一个设计里,多个模块中用到的时间单位和时间精度单位不同,需要用到以下的时间结构:

(1)用`timescale命令来声明本模块中所用到的时间单位和时间精度;

(2)用系统任务$printtimcscale来输出显示一个模块的时间单位和时间精度;

(3)用系统函数 $tirme 和 $realtime及%t 格式声明来输出显示 EDA工具记录的时间信息。

6.为什么说系统任务$readmem可以用来产生用于算法验证的极其复杂的测试用数据流?

在 Verilog HDL程序中有两个系统任务$readmemb 和 $readmemh,并用来从文件中读取数据到存储器中,这两个系统任务可以在仿真的任何时刻被执行使用。复杂数据可以用C语言产生,存在文件中,用 $readmem 取出存入存储器,在按节拍输出,这在验证算法逻辑电路时特别看用。

7.为什么说熟练地使用条件编译命令可以使源代码有更大的灵活性,可以适用于不同的实现对象﹐如不同工艺的ASIC或速度规模不同的FPGA或CPLD,从而为软核的商品化创造条件?

合理的使用条件编译和条件执行预处理可以使测试程序适应不同的编译环境,也可以把不同的测试过程编写到一个统一的测试程序中去,可以简化测试的过程,对于复杂设计的验证模块的编写很有实用价值。

边栏推荐

- Flask-SQLAlchemy

- 线代:已知一个特征向量快速求另外两个与之正交的特征向量

- Unit 4 Routing Layer

- [ROS] (05) ROS Communication - Node, Nodes & Master

- Deep learning framework pytorch rapid development and actual combat chapter3

- 瑞吉外卖笔记——第08讲读写分离

- yolov5 improvement (1) Add attention focus mechanism

- 海明校验码纠错设计原理

- Sentinel源码(五)FlowSlot以及限流控制器源码分析

- Flask框架

猜你喜欢

![[ROS] (01) Create ROS workspace](/img/2a/11e5023ef6d052d98b4090d2eea017.png)

[ROS] (01) Create ROS workspace

deal!It's July 30th!

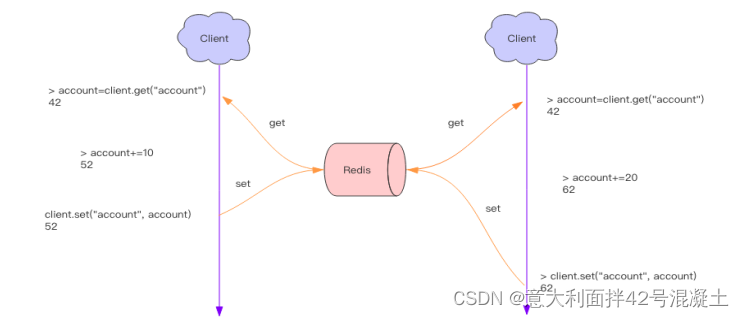

redis分布式锁和看门狗的实现

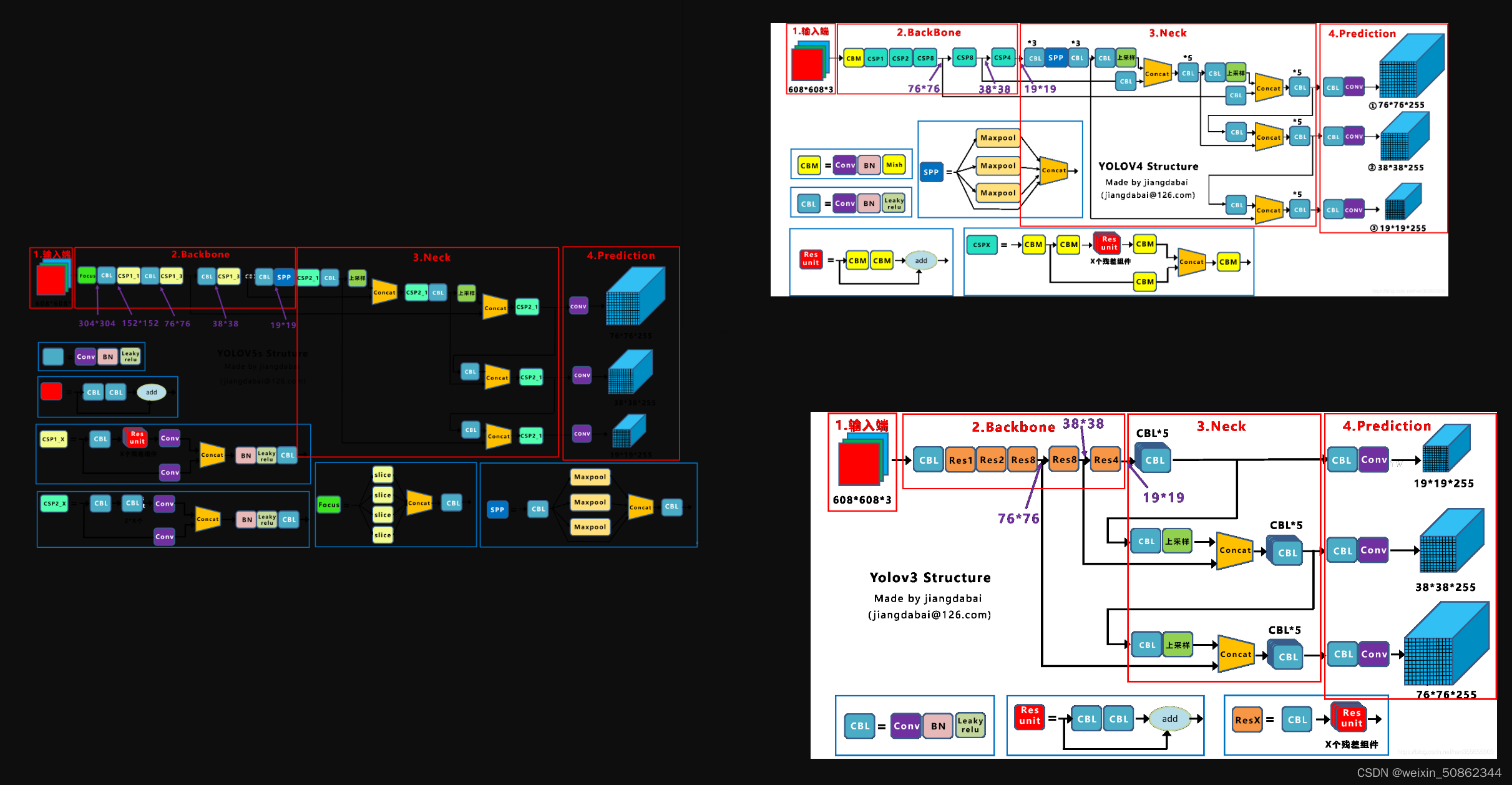

yolov5,yolov4,yolov3乱七八糟的

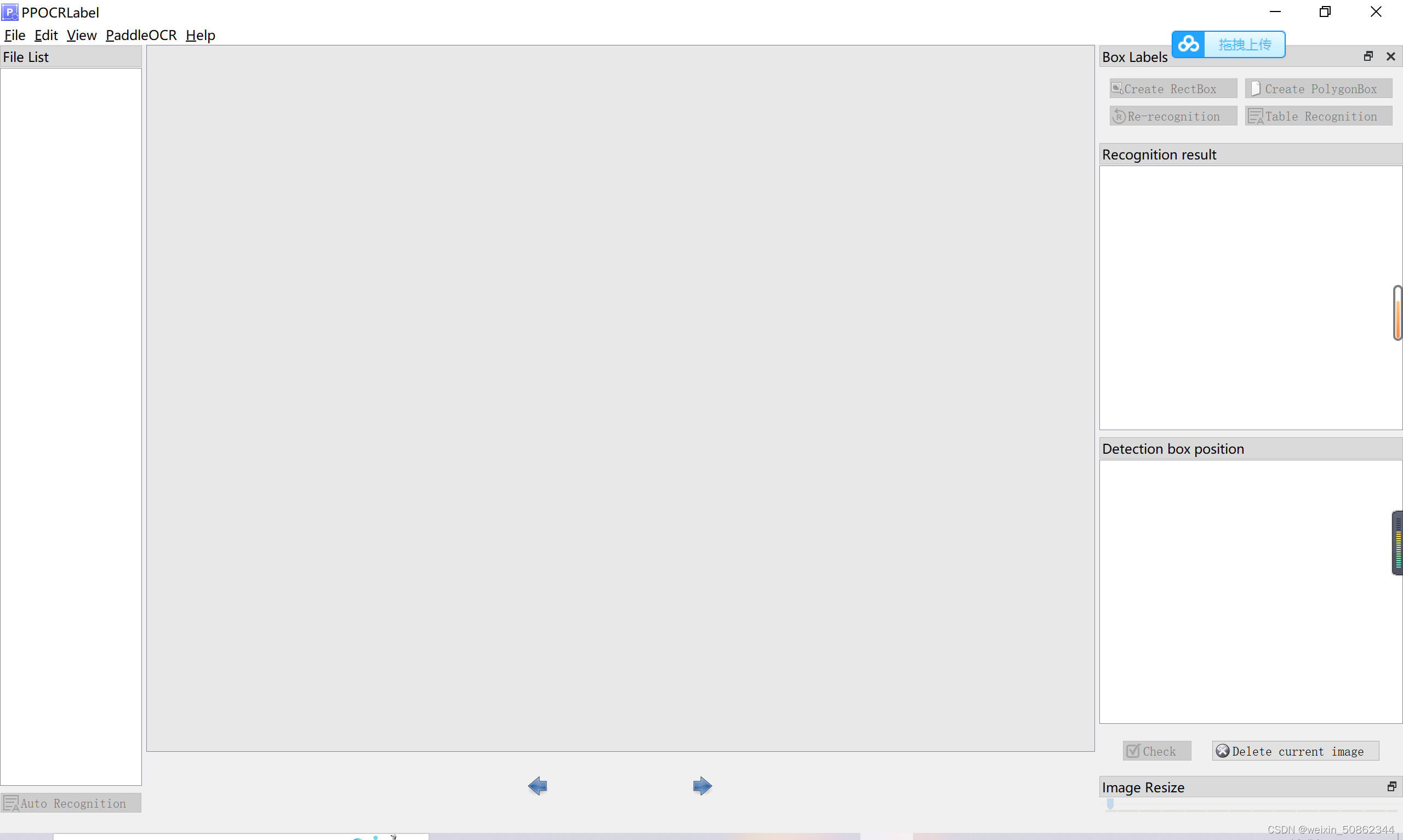

Briefly write about the use and experience of PPOCRLabel

Interview | with questions to learn, Apache DolphinScheduler Wang Fuzheng

Unit 15 Paging, Filtering

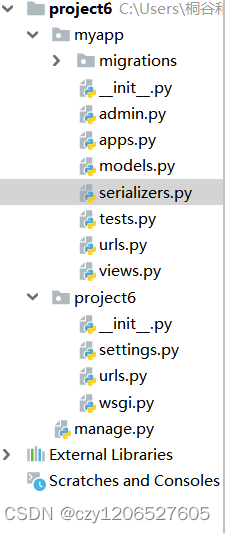

第十一单元 序列化器

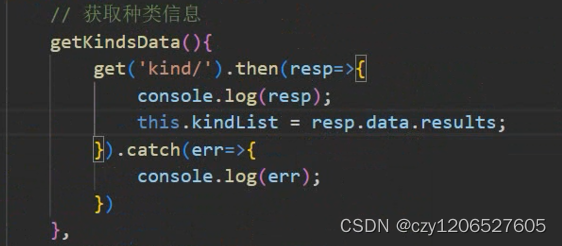

第十单元 前后连调

Some impressions of the 519 plummet 2021-05-21

随机推荐

【ROS】工控机的软件包不编译

The bad policy has no long-term impact on the market, and the bull market will continue 2021-05-19

Hands-on OCR (1)

Building and getting started with the Flask framework

Paddle window10 environment using conda installation

ping命令的使用及代码_通过命令查看ping路径

MobileNet ShuffleNet & yolov5替换backbone

8581 线性链表逆置

Steps to connect the virtual machine with xshell_establish a network connection between the host and the vm virtual machine

第六单元 初识ORM

window10 lower semi-automatic labeling

Verilog Learning Series

Some impressions of the 519 plummet 2021-05-21

【VCU】详解S19文件(S-record)

window10下半自动标注

[ROS]roscd和cd的区别

理解TCP长连接(Keepalive)

The IDEA of packaged jar package

第十二单元 关联序列化处理

Flask项目的完整创建 七牛云与容联云