当前位置:网站首页>Literacy Ethernet MII interface types Daquan MII, RMII, smii, gmii, rgmii, sgmii, XGMII, XAUI, rxaui

Literacy Ethernet MII interface types Daquan MII, RMII, smii, gmii, rgmii, sgmii, XGMII, XAUI, rxaui

2022-07-05 06:53:00 【Enlaihe】

One 、 brief introduction

MII It's English Medium Independent Interface Abbreviation , Translated into Chinese “ Media independent interface ”, This interface is generally used in Ethernet hardware platform MAC Layer and the PHY Between layers ,MII There are many types of interfaces , Commonly used MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI etc. . Let's introduce them one by one .

Two 、MII Interface type

1、MII Interface

TX_ER(Transmit Error): Send data error signal , Synchronize on TX_CLK, High active , Express TX_ER Invalid data transmitted during the validity period . about 10Mbps At a rate ,TX_ER It doesn't work ;

TX_EN(Transmit Enable): Send enable signal , Only in TX_EN The data transferred within the validity period is valid ;

TX_CLK: Send reference clock ,100Mbps At a rate , The clock frequency is 25MHz,10Mbps At a rate , The clock frequency is 2.5MHz. Be careful ,TX_CLK The direction of the clock is from PHY Side pointing MAC On the side , So this clock is made up of PHY Provided .

TXD(Transmit Data)[3:0]: Data transmission signals , common 4 A signal line ;

RX_ER(Receive Error): Receive data error signal , Synchronize on RX_CLK, High active , Express RX_ER Invalid data transmitted during the validity period . about 10Mbps At a rate ,RX_ER It doesn't work ;

RX_DV(Reveive Data Valid): Receive data valid signal , The action type depends on TX_EN;

RXD(Receive Data)[3:0]: Data reception signal , common 4 A signal line ;

RX_CLK: Receive data reference clock ,100Mbps At a rate , The clock frequency is 25MHz,10Mbps At a rate , The clock frequency is 2.5MHz.RX_CLK Also by PHY It's on the side .

CRS:Carrier Sense, Carrier detection signal , No need to synchronize with the reference clock , As long as there's data transmission ,CRS It works , in addition ,CRS Only PHY Effective in half duplex mode ;

COL:Collision Detectd, Collision detection signal , No need to synchronize with the reference clock , Only PHY Effective in half duplex mode .

MII The interface has 16 Root line .

2、RMII Interface

RMII namely Reduced MII, yes MII Simplified board , The number of connections is determined by MII Of 16 The root is reduced to 8 root .

TXD[1:0]: Data transmission signal line , The data bit width is 2, yes MII Half of the interface ;

RXD[1:0]: Data receiving signal line , The data bit width is 2, yes MII Half of the interface ;

TX_EN(Transmit Enable): Data transmission enable signal , And MII The function of the signal line in the interface is the same ;

RX_ER(Receive Error): Data receiving error prompt signal , And MII The function of the signal line in the interface is the same ;

CLK_REF: It is provided by an external clock source 50MHz Reference clock , And MII The interface is different ,MII The receiving clock and the sending clock in the interface are separate , And it's all from PHY The chip provides MAC Chip . What needs to be noted here is , Because the data receiving clock is provided by the external crystal oscillator rather than extracted by the carrier signal , So in PHY The data receiving part in the layer chip needs to design a FIFO, Used to coordinate two different clocks , Provide buffer when sending received data .PHY The sending part of the layer chip is not required FIFO, It directly sends the received data to MAC That's all right. .

CRS_DV: This signal is caused by MII Interface RX_DV and CRS The two signals are combined . When the media is not idle ,CRS_DV and RE_CLK Different steps are given . When CRS Than RX_DV At the end of the morning ( That is, when the carrier disappears and there is still data to be transmitted in the queue ), Will appear CRS_DV At the boundary of a half byte, use 25MHz/2.5MHz The frequency is 0、1 Switch back and forth between . therefore ,MAC Can from CRS_DV The exact recovery of RX_DV and CRS.

stay 100Mbps At rate ,TX/RX Sample one data per clock cycle ; stay 10Mbps At rate ,TX/RX every other 10 Sample one data every period , thus TX/RX Data needs to be retained on the data line 10 A cycle , Equivalent to a data transmission 10 Time .

When PHY After the layer chip receives the effective carrier signal ,CRS_DV The signal becomes valid , If at this time FIFO There's no data in , Then it will send out all 0 Data for MAC, Then when FIFO Fill in valid data frames , The beginning of the data frame is “101010—” Crossed preamble , When... Appears in the data “01” Bit hour , Represents the beginning of formal data transmission ,MAC The chip detects this change , To start receiving data .

When the external carrier signal disappears ,CRS_DV Will become invalid , But if FIFO When there is data to be sent in ,CRS_DV It will become effective again in the next cycle , Then invalid and effective , until FIFO Until the data is sent . In the process of receiving, if there is invalid carrier signal or invalid data coding , be RX_ER Will become effective , Indicates that the physical layer chip receives an error .

3、SMII Interface

SMII namely Serial MII, Serial MII It means , Follow RMII comparison , The connection is further reduced to 4 root ;

TXD: Send a data signal , The seat width is 1;

RXD: Receiving data signals , The seat width is 1;

SYNC: Send and receive data synchronization signals , Every time 10 Clock cycles set 1 Secondary high level , Indicates synchronization .

CLK_REF: A reference clock shared by all ports , The frequency is 125MHz, Why? 100Mbps The speed should be 125MHz The clock ? Because in every 8 Bit data will be inserted 2 Bit control signal , Please see the following introduction .

TXD/RXD With 10 Bits are a set of , With SYNC Indicates the beginning of a set of data for high level , stay SYNC After getting higher 10 In clock cycles ,TXD The data output in turn is :TXD[7:0]、TX_EN、TX_ER, The meaning of control signal is similar to MII The same in the interface ;RXD The data output in turn is :RXD[7:0]、RX_DV、CRS,RXD[7:0] Meaning and RX_DV of , When RX_DV When is valid ( High level ),RXD[7:0] What is transmitted on the is the data received by the physical layer . When RX_DV When it is invalid ( Low level ),RXD[7:0] The status information data of the physical layer is transmitted on . See the table below :

When the rate is 10Mbps when , Each set of data should be repeated 10 Time ,MAC/PHY Chip per 10 Take a sample once per cycle .MAC/PHY The chip will string after receiving the data / And convert .

4、SSMII Interface

SSMII namely Serial Sync MII, It is called serial synchronous interface , Follow SMII The interface is very similar , Just send and receive with independent reference clock and synchronous clock , No longer like SMII That way, the transceiver shares the reference clock and the synchronization clock , Transmission distance ratio SMII further .

5、SSSMII Interface

SSSMII namely Source Sync Serial MII, It is called source synchronous serial MII Interface ,SSSMII And SSMII The difference lies in the direction of the reference clock and the synchronous clock ,SSMII Of TX/RX Both the reference clock and the synchronization clock are controlled by PHY Chip provides , and SSSMII Of TX The reference clock and the synchronization clock are composed of MAC Chip provides ,RX The reference clock and the synchronization clock are composed of PHY Chip provides , So as the name suggests, it is called source synchronous serial .

6、GMII Interface

And MII Interface comparison ,GMII The data width of is determined by 4 A into 8 position ,GMII The control signals in the interface are as follows TX_ER、TX_EN、RX_ER、RX_DV、CRS and COL The effect is the same as MII The same as in the interface , Send reference clock GTX_CLK And receive the reference clock RX_CLK The frequencies of the two are 125MHz(1000Mbps/8=125MHz).

Here's a special point to make , That's sending the reference clock GTX_CLK, It and MII Interface TX_CLK Is different ,MII Interface TX_CLK By PHY The chip provides MAC Chip , and GMII Interface GTX_CLK By MAC The chip provides PHY Chip . They're not in the same direction .

in application , most GMII The interfaces are all compatible MII Interface , therefore , General GMII Each interface has two transmit reference clocks :TX_CLK and GTX_CLK( The directions of the two are different , I've already said that ), In use as MII Mode time , Use TX_CLK and 8 In the root cable 4 root .

6、RGMII Interface

RGMII namely Reduced GMII, yes RGMII Simplified version of , Change the number of interface signal lines from 24 The root is reduced to 14 root (COL/CRS Port status indication signal , It's not drawn here ), The clock frequency is still 125MHz,TX/RX Data width from 8 To become 4 position , In order to maintain 1000Mbps The transmission rate remains unchanged ,RGMII The interface samples data on both the rising and falling edges of the clock . Send at the rising edge of the reference clock GMII Interface TXD[3:0]/RXD[3:0], Send on the falling edge of the reference clock GMII Interface TXD[7:4]/RXD[7:4].RGMI It's also compatible with 100Mbps and 10Mbps Two rates , At this time, the reference clock rates are 25MHz and 2.5MHz.

TX_EN Signal line transmission TX_EN and TX_ER Two kinds of information , stay TX_CLK The rising edge of sends TX_EN, The falling edge sends TX_ER; alike ,RX_DV The signal line also transmits RX_DV and RX_ER Two kinds of information , stay RX_CLK The rising edge of sends RX_DV, The falling edge sends RX_ER.

7、SGMII Interface

SGMII namely Serial GMII, Serial GMII, Send and receive a pair of differential signal lines , clock frequency 625MHz, Samples are taken at both the rising and falling edges of the clock signal , Reference clock RX_CLK from PHY Provide , It's optional , It is mainly used for MAC When there is no clock on the side , In general ,RX_CLK Don't use . Sending and receiving can recover the clock from the data .

stay TXD Serial data sent , Every time 8 Bit data will be inserted TX_EN/TX_ER Two bit control information , Again , stay RXD Receiving data , Every time 8 Bit data will be inserted RX_DV/RX_ER Two bit control information , So the total data rate is 1.25Gbps=625Mbps*2.

Actually , majority MAC Chip SGMII Interfaces can be configured to SerDes Interface ( Physically fully compatible , Just configure the register ), Direct external optical module , Without the need for PHY Layer chip , At this time, the clock rate is still 625MHz, But at this time SGMII The interface is different ,SGMII The interface speed is increased to 1.25Gbps Because the control information is inserted , and SerDes The port rate is increased because 8B/10B Transformation , Originally 8B/10B The transformation is PHY Chip work , stay SerDes Interface , Because there's no answer outside PHY chip , here 8B/10B Change in MAC In the chip .8B/10B The main function of transformation is scrambling code , So that there is no too long connection in the signal “0” Helian “1” situation , Affect the extraction of clock information , About 8B/10B Transform knowledge , I will introduce it separately later .

8、TBI Interface

TBI namely Ten Bit Interface It means , The interface data bit width consists of GMII Interface 8 Bit increase to 10 position , Actually ,TBI Interface with GMII The difference between interfaces is not very big , Extra 2 Bit data is mainly due to TBI Under the interface ,MAC The chip is sending data to PHY Before the chip 8B/10B Transformation (8B/10B The transformation is in PHY Completed in the chip , I've already said that ), in addition ,RX_CLK+/- It is a half frequency clock recovered from the received data , The frequency is 62.5MHz,RX_CLK+/- It's not a differential signal , But two independent signals , There is a gap between the two 180 The phase difference of degrees , Data is sampled on the rising edge of both clocks .RX_CLK+/- Also called Pseudo differential signal . In addition to the above , The rest of the signals follow GMII The same in the interface .

Most chips TBI Interface and GMII Interface compatibility . In use as TBI Interface ,CRS and COL Generally do not use .

9、RTBI Interface

RTBI namely Reduced TBI, Simplified edition TBI, The interface data bit width is 5bit, The clock frequency is 125MHz, Data is sampled on both the rising and falling edges of the clock , Same as RGMII As the interface ,TX_EN Online transmission TX_EN and TX_ER Two kinds of information , On the rising edge of the clock TX_EN, Falling edge transmission TX_ER;RX_DV Online transmission RX_DV and RX_ER Two kinds of information , stay RX_CLK The rising edge passes RX_DV, Falling edge transmission RX_ER.

The port rate of 10 Gigabit Ethernet interface is 10Gbps, There are mainly XGMII and XAUI Two kinds of , And then there is HIGIG, however HIGIG yes Broadcom Private standards of the company , I will not introduce .

10、XGMII Interface

TXD[31:0]: Send data channel ,32 Bit parallel data .

RXD[31:0]: Data receiving channel ,32 Bit parallel data .

TXC[3:0]: Send channel control signal ,TXC=0 when , Express TXD Data is transmitted on ;TXC=1 when , Express TXD Control characters are transmitted on .TXC[3:0] They correspond to each other TXD[31:24], TXD[23:16], TXD[15:8], TXD[7:0].

RXC[3:0]: Receive channel control signal ,RXC=0 when , Express RXD Data is transmitted on ;RXC=1 when , Express RXD Control characters are transmitted on .RXC[3:0] They correspond to each other RXD[31:24], RXD[23:16], RXD[15:8], RXD[7:0].

TX_CLK:TXD and TXC The reference clock of , clock frequency 156.25MHz, Data is sampled on both the rising and falling edges of the clock signal .156.25MHz * 2 * 32 = 10Gbps .

RX_CLK:RXD and RXC The reference clock of , clock frequency 156.25MHz, Data is sampled on both the rising and falling edges of the clock signal .

XGMII Interface total 74 Root connection , Single ended signal , use HSTL/SSTL_2 Logic , Port voltage 1.5V/2.5V, because SSTL_2 The port voltage of is high , High power consumption , Now it is seldom used .HSTL namely High Speed Transceiver Logic, The meaning of high-speed sending logic .SSTL, namely Stub Series Terminated Logic, Short circuit termination logic , Mainly used for high-speed memory interface ,SSTL There are currently two standards ,SSTL_3 yes 3.3V standard ;SSTL_2 yes 2.5V standard .

10、XAUI Interface

Due to the influence of electrical characteristics ,XGMII Interface PCB The maximum transmission distance of the cable is only 7cm, also XGMII Too many connections on the interface , Bring inconvenience to practical application , therefore , in application ,XGMII Interfaces are usually XAUI Interface instead of ,XAUI namely 10 Gigabit attachment unit interface,10G Auxiliary unit interface ,XAUI stay XGMII On the basis of this, we have realized XGMII Physical distance extension of the interface , take PCB The transmission distance of the line is increased to 50cm, Make backplane routing possible .

Source end XGMII Send and receive 32 The bit width data stream is divided into 4 Independent lane passageway , Every lane The channel corresponds to a byte , the XGXS(XGMII Extender Sublayer) complete 8B/10B After the coding , take 4 individual lane They correspond to each other XAUI Of 4 A separate channel ,XAUI The port rate is :2.5Gbps * 1.25 * 4=12.5Gbps.

At the sending end XGXS Module , take TXD[31:0]/ RXD[31:0],TXC[3:0]/ RXC[3:0], TX_CLK/ RX_CLK Convert to serial data from TX Lane[3:0]/ RX Lane[3:0] Send it out , At the receiving end XGXS Module , Serial data is converted into parallel , And clock recovery and compensation , Finish shaking the clock , after 5B/4B After decoding , Regroup into XGMII.

XAUI The interface adopts differential line , Send and receive four pairs ,CML Logic ,AC Coupling mode , The coupling capacitance is 10nF~100nF Between .

XAUI The interface can be directly connected to the optical module , Such as XENPAK/X2 etc. . It can also be converted into one way 10G The signal XFI, Pick up XFP/SFP+ etc. .

Some chips do not support XAUI Interface , Only support XGMII Interface , At this time, special chips can be used XGMII - XAUI Interface conversion , Such as BCM8011 etc. .

3、 ... and 、SerDes and SGMII

SerDes and SGMII,SGMII Interface is the support 10/100/1000M The adaptive ,SerDes The interface only has 1000Mbps Data transceiver function , Rate adaptation is not supported .

XAUI and SGMII The difference is the former 10G the latter 1G, They are all media independent , It has nothing to do with your use of electricity, light or any type of transmission module .

XAUI Yes 4 individual lane, Every lane go 2.5G Valid data ( the truth is that 3.125G, Because each 8bit Insert 2bits Of csma/cd The control signal of ),RXAUI yes XAUI Of reduce edition , from 4 individual lane become 2 individual ,6.25G per lane.

边栏推荐

- UTC, GPS time and Tai

- The differences and connections among cookies, sessions, JWT, and tokens

- UIO driven framework

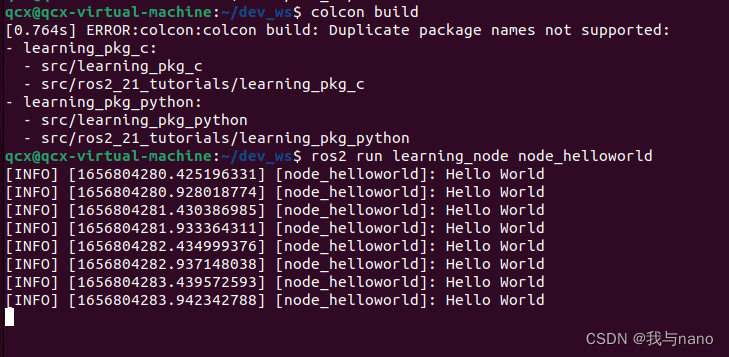

- Ros2 topic (VIII)

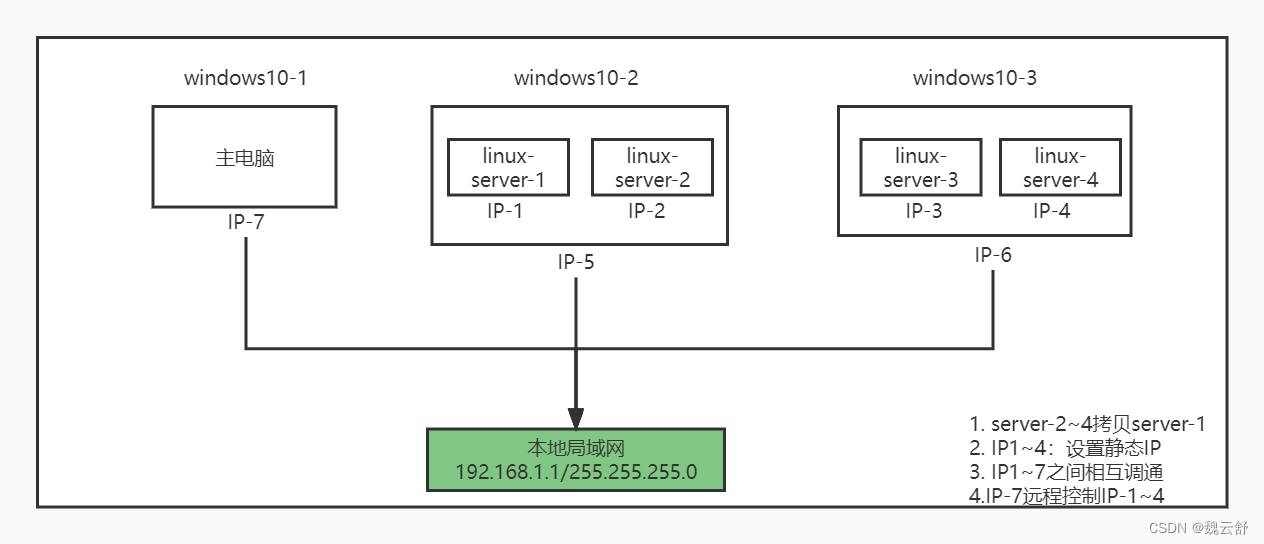

- 在本地搭建一个微服务集群环境,学习自动化部署

- Cookie、Session、JWT、token四者间的区别与联系

- Use ffmpeg to rotate, flip up and down, and flip horizontally

- CGroup CPU group source code analysis

- Build a microservice cluster environment locally and learn to deploy automatically

- Orin 安装CUDA环境

猜你喜欢

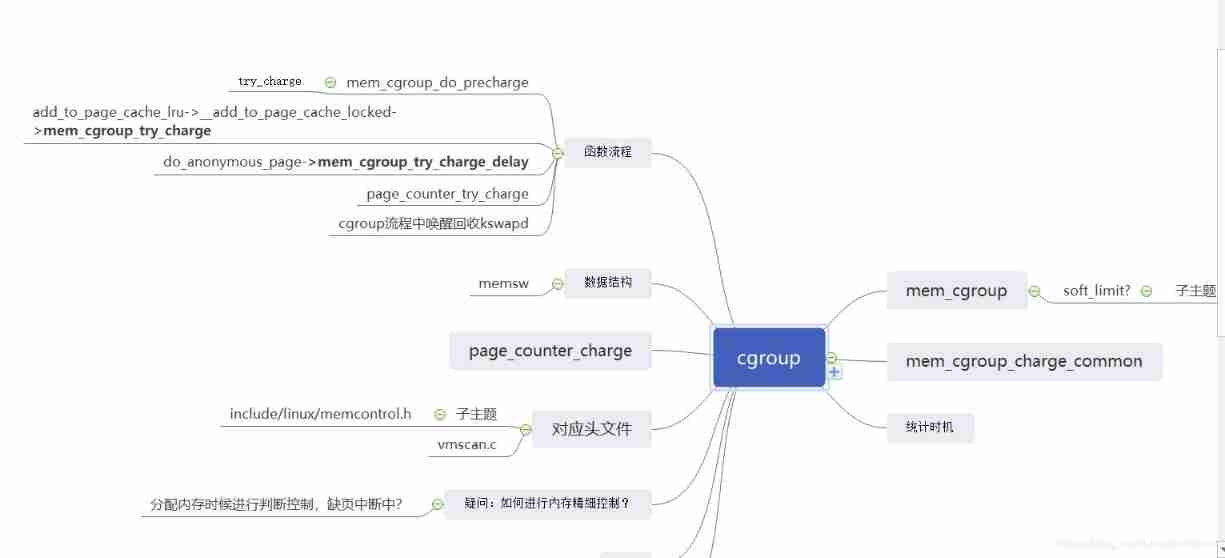

cgroup_ memcg

Vant Weapp SwipeCell設置多個按鈕

你心目中的数据分析 Top 1 选 Pandas 还是选 SQL?

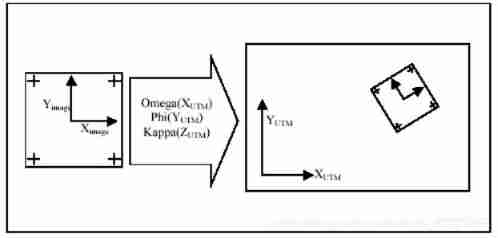

A brief introduction to heading/pitch/roll and omega/phi/kappa

![[algorithm post interview] interview questions of a small factory](/img/62/6e330b1eba38f2dc67b21a10f0e2a8.jpg)

[algorithm post interview] interview questions of a small factory

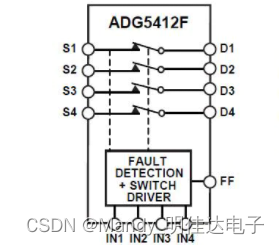

Adg5412fbruz-rl7 applies dual power analog switch and multiplexer IC

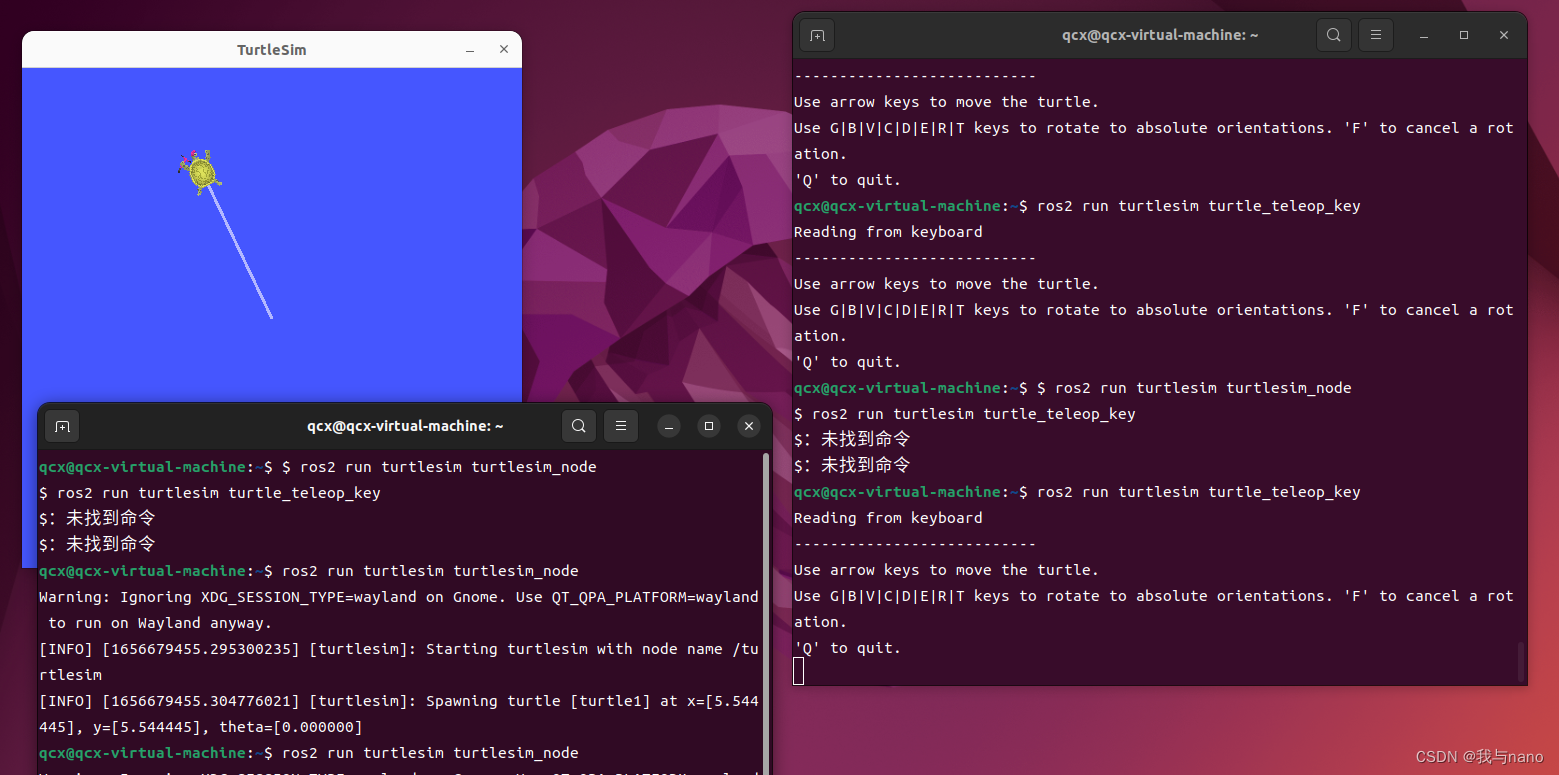

ROS2——node节点(七)

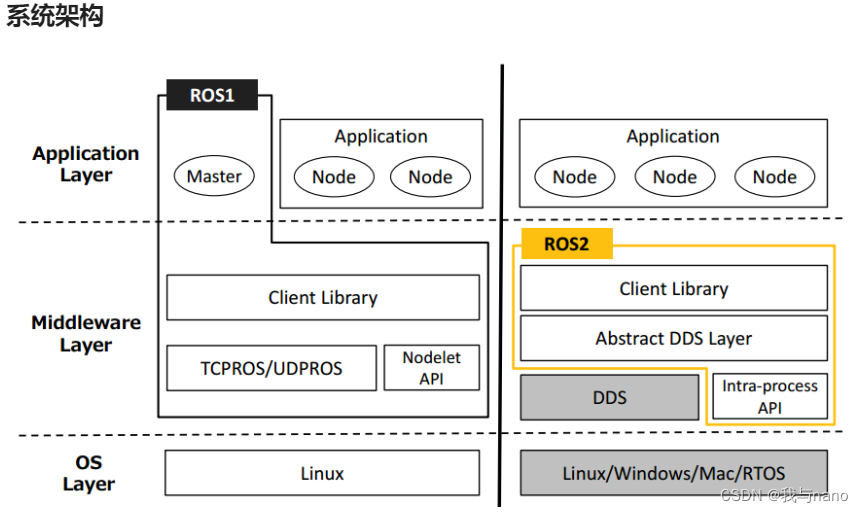

Ros2 - ros2 vs. ros1 (II)

在本地搭建一个微服务集群环境,学习自动化部署

Ros2 - install ros2 (III)

随机推荐

Ros2 - workspace (V)

The differences and connections among cookies, sessions, JWT, and tokens

Empire help

Huawei bracelet, how to add medicine reminder?

Edge calculation data sorting

ROS2——Service服务(九)

Rehabilitation type force deduction brush question notes D2

现在有html文件,和用vs制作的mvc(连接了数据库),怎么两个相连?

MySQL setting trigger problem

2. Addition and management of Oracle data files

Marvell 88e1515 PHY loopback mode test

cgroup_ memcg

Instruction execution time

Time is fast, please do more meaningful things

SOC_SD_CMD_FSM

逻辑结构与物理结构

Ros2 - ros2 vs. ros1 (II)

ROS2——初识ROS2(一)

LSA Type Explanation - lsa-5 (type 5 LSA - autonomous system external LSA) and lsa-4 (type 4 LSA - ASBR summary LSA) explanation

使用paping工具进行tcp端口连通性检测