当前位置:网站首页>#systemverilog# 可綜合模型的結構總結

#systemverilog# 可綜合模型的結構總結

2022-07-06 07:08:00 【那麼菜】

一、可綜合模型的結構

如果程序只用於仿真,那麼幾乎所有的語法和編程語句都可以使用。但如果程序是用於硬件實現,那麼我們就必須保證程序的可綜合性,即所編寫的程序能被綜合器 轉化為相應的電路結構。不可綜合的HDL語句在用綜合工具綜合時將被忽略或者報錯。作為設計者,應該對可綜合模型的結構有所了解。

雖然不同的綜合工具對Verilog HDL語法結構的支持不盡相同,但Verilog HDL中某些典型的結構是很明確地被所有綜合工具支持或不支持的。

(1)所有綜合工具都支持的結 構:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有綜合工具都不支持的結構:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)有些工具支持有些工具不支持的結構:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

因此,要編寫出可綜合的模型,應盡量采用所有綜合工具都支持的結構來描述,這樣才能保證設計的正確性和縮短設計周期。

二、建立可綜合模型的原則

要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點:

(1)不使用初始化語句。

(2)不使用帶有延時的描述。

(3)不使用循環次數不確定的循環語句,如forever、while等。

(4)不使用用戶自定義原語(UDP元件)。

(5)盡量使用同步方式設計電路。

(6)除非是關鍵路徑的設計,一般不采用調用門級元件來描述設計的方法,建議采用行為語句來完成設計。

(7)用always過程塊描述組合邏輯,應在敏感信號列錶中列出所有的輸入信號。

(8)所有的內部寄存器都應該能够被複比特,在使用FPGA實現設計時,應盡量使用器件的全局複比特端作為系統總的複比特。

(9)對時序邏輯描述和建模,應盡量使用非阻塞賦值方式。對組合邏輯描述和建模,既可以用阻塞賦值,也可以用非阻塞賦值。但在同一個過程塊中,最好不要同時用阻塞賦值和非阻塞賦值。

(10)不能在一個以上的always過程塊中對同一個變量賦值。而對同一個賦值對象不能既使用阻塞式賦值,又使用非阻塞式賦值。

(11)如果不打算把變量推導成鎖存器,那麼必須在if語句或case語句的所有條件分支中都對變量明確地賦值。

(12)避免混合使用上昇沿和下降沿觸發的觸發器。

(13)同一個變量的賦值不能受多個時鐘控制,也不能受兩種不同的時鐘條件(或者不同的時鐘沿)控制。

(14)避免在case語句的分支項中使用x值或z值。

三、阻塞與非阻塞

建議在時序邏輯建模時使用非阻塞式賦值。因為對於阻塞式賦值來說,賦值語句的順序對最後的綜合結果有著直接的影響,設計者稍不留意就會使綜合結果與設計本 意大相徑庭。而如果采用非阻塞式賦值,則可以不考慮賦值語句的排列順序,只需將其連接關系描述清楚即可。如下面的模型:

always @ (posedge clkA) //Label AwA

… = DataOut; //讀DataOut的值

always @ (posedge clkA) //Label AwB

DataOut <= …; //采用非阻塞式賦值

如果將上述模型改為阻塞式賦值“DataOut = …”,按照程序中的書寫順序模擬這些always語句,在clkA上昇沿處,always語句AwA讀取了DataOut的當前值,然後always語句 AwB再向DataOut賦新值。如果顛倒了這兩條always語句的順序(或仿真器選擇重新排定這兩條always語句的執行順序),那麼先執行 always語句AwB,導致零時間內將新值賦給DataOut,隨後always語句AwA讀取的便是更新後的DataOut值。這看起來是由於 always語句都可以執行時,向DataOut的賦值是在零時間內發生並完成的。因此根據先執行哪一條always語句,AwA中讀取的DataOut 值可能是其原值,也可能是其新值。

使用非阻塞賦值就可以消除這種仿真行為的依賴性,這時,讀取DataOut發生在當前時刻,而在當前仿真周期結束時(即所有的變量讀取都已完成)才將新值 賦給DataOut。這樣上述模型的行為不再受always語句執行順序的影響。因此,在某條always語句內對變量賦值而在該always語句外讀取 變量,那麼賦值語句應是非阻塞式賦值。

边栏推荐

- 漏了监控:Zabbix对Eureka instance状态监控

- Windows Server 2016 standard installing Oracle

- On the world of NDK (2)

- Librosa audio processing tutorial

- leetcode841. Keys and rooms (medium)

- Oracle database 11gr2 uses TDE transparent data encryption to report an error ora28353. If you run to close the wallet, you will report an error ora28365. If you run to open the wallet, you will repor

- UWA pipeline version 2.2.1 update instructions

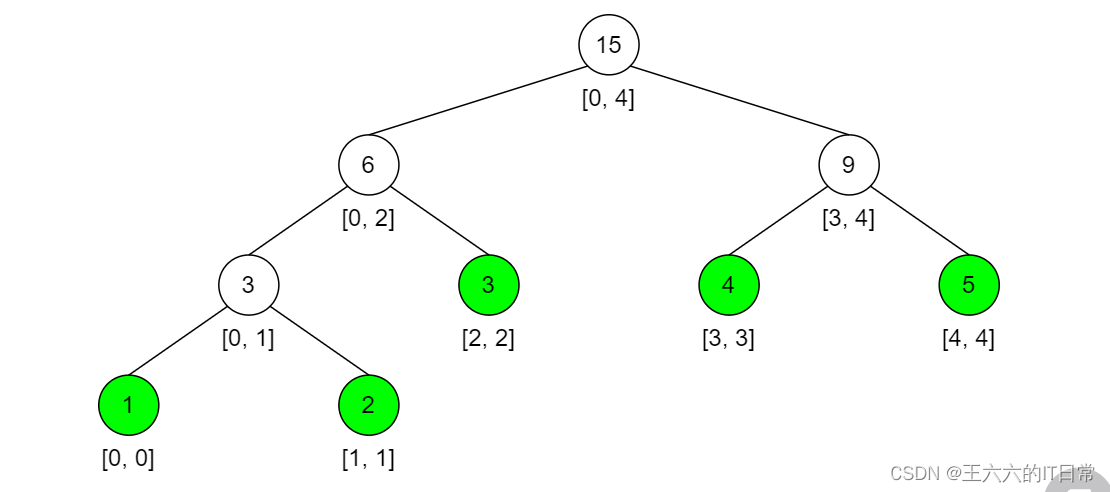

- Prefix and array series

- Uncaught typeerror: cannot red properties of undefined (reading 'beforeeach') solution

- Leetcode 78: subset

猜你喜欢

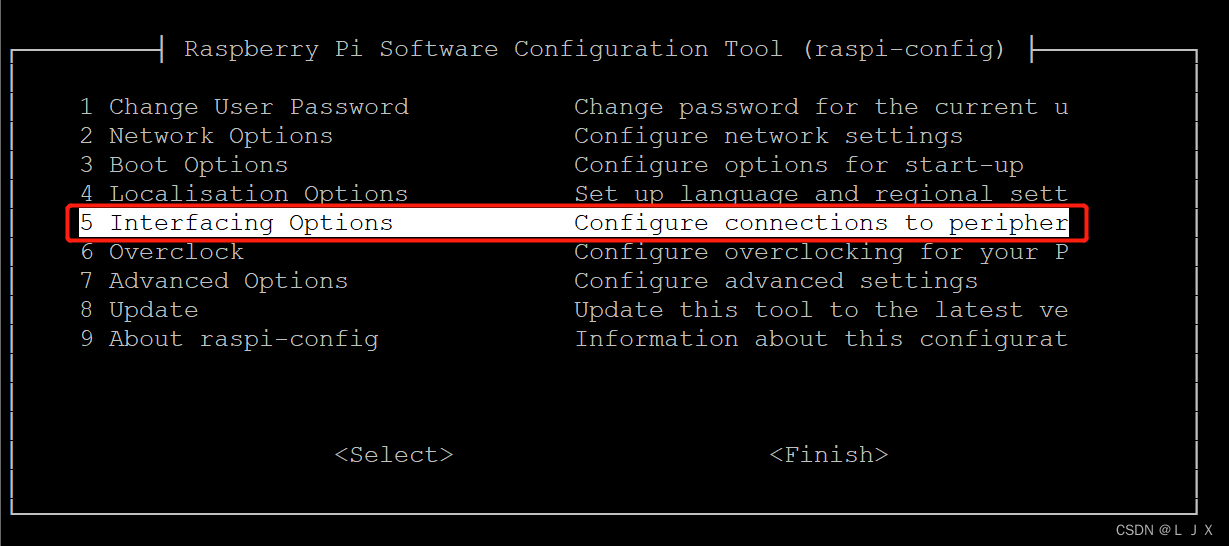

Raspberry pie serial port login and SSH login methods

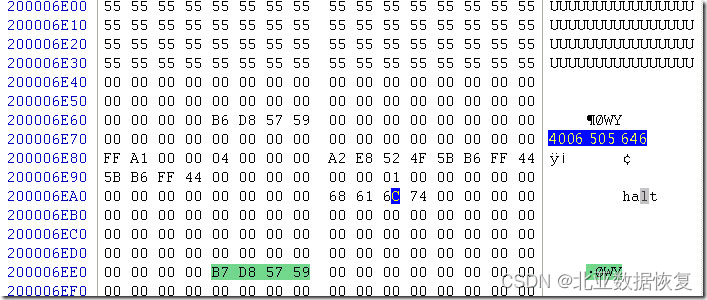

【服务器数据恢复】IBM服务器raid5两块硬盘离线数据恢复案例

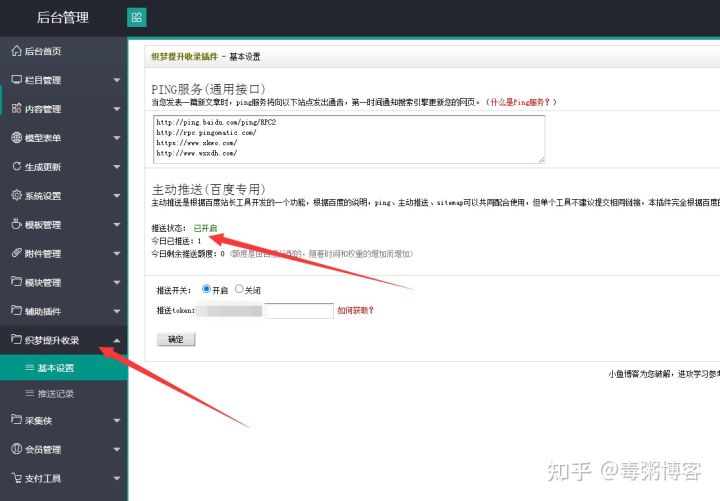

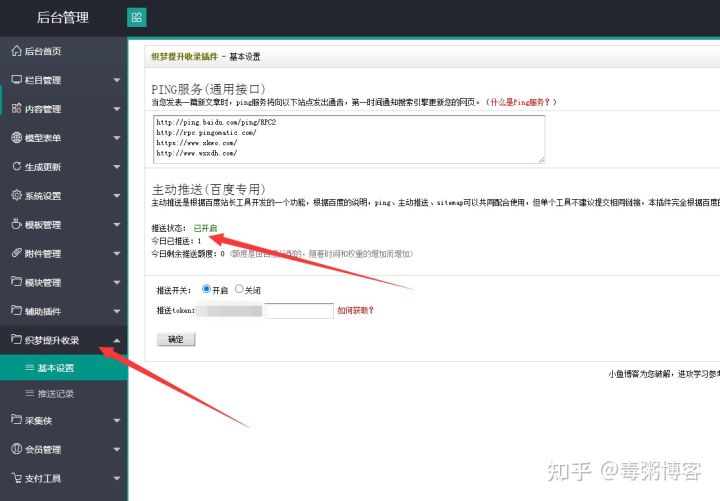

首发织梦百度推送插件全自动收录优化seo收录模块

![[server data recovery] case of offline data recovery of two hard disks of IBM server RAID5](/img/c3/7a147151b7338cf38ffbea24e8bafd.jpg)

[server data recovery] case of offline data recovery of two hard disks of IBM server RAID5

The first Baidu push plug-in of dream weaving fully automatic collection Optimization SEO collection module

First knowledge of OpenGL es learning (1)

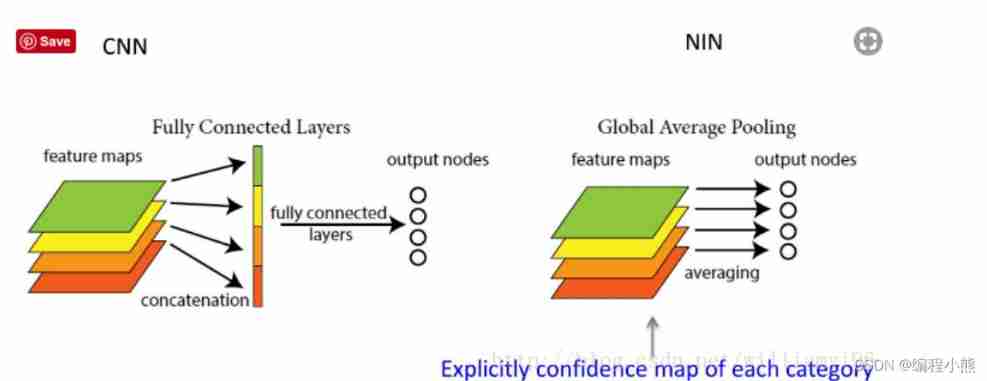

Cif10 actual combat (resnet18)

1091: two or three things in childhood (multi instance test)

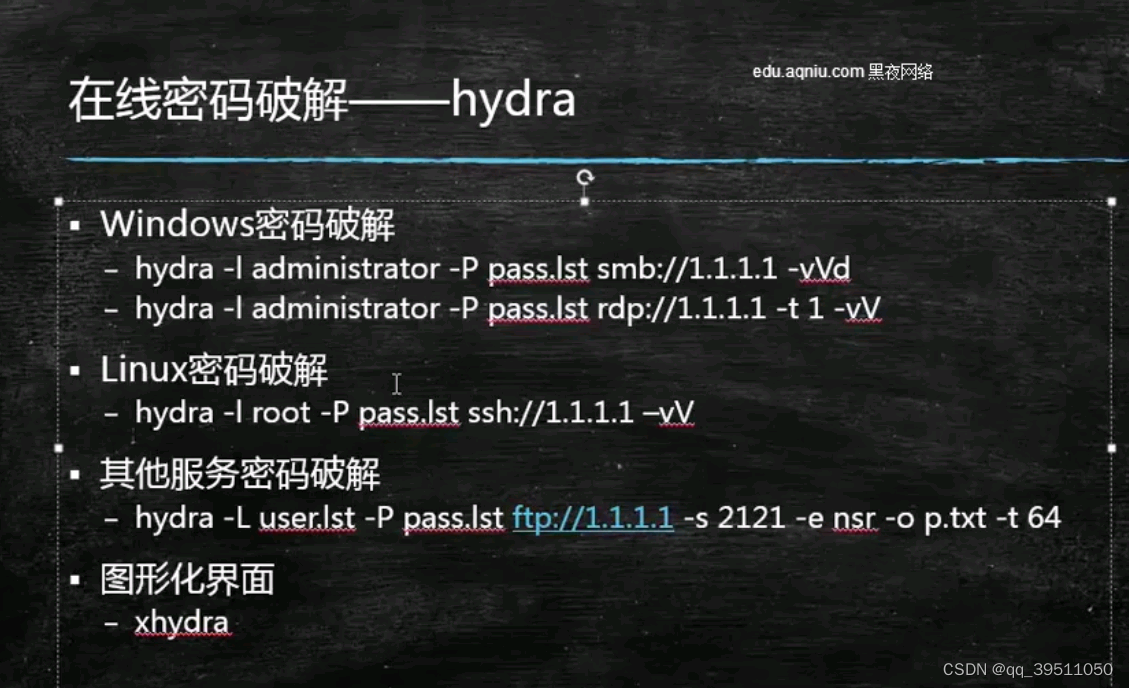

hydra常用命令

【每日一题】729. 我的日程安排表 I

随机推荐

【服务器数据恢复】IBM服务器raid5两块硬盘离线数据恢复案例

MVVM of WPF

The difference between get and post request types

从autojs到冰狐智能辅助的心里历程

leetcode35. 搜索插入位置(简单,找插入位置,不同写法)

Idea console color log

After sharing the clone remote project, NPM install reports an error - CB () never called! This is an error with npm itself.

顶测分享:想转行,这些问题一定要考虑清楚!

TS基础篇

[some special grammars about C]

Supporting title of the book from 0 to 1: ctfer's growth road (Zhou Geng)

UWA pipeline version 2.2.1 update instructions

supervisor 使用文档

Wechat brain competition answer applet_ Support the flow main belt with the latest question bank file

ROS learning_ Basics

这个高颜值的开源第三方网易云音乐播放器你值得拥有

C language_ Double create, pre insert, post insert, traverse, delete

At the age of 26, I changed my career from finance to software testing. After four years of precipitation, I have been a 25K Test Development Engineer

Uncaught typeerror: cannot red properties of undefined (reading 'beforeeach') solution

leetcode1020. 飞地的数量(中等)