当前位置:网站首页>GPIO port bit based on Cortex-M3 and M4 with operation macro definition (can be used for bus input and output, STM32, aducm4050, etc.)

GPIO port bit based on Cortex-M3 and M4 with operation macro definition (can be used for bus input and output, STM32, aducm4050, etc.)

2022-07-05 07:06:00 【Mike Zhou, exclusive musician of Netease】

be based on Cortex-M3、M4 Of GPIO Port with operation macro definition ( Bus input and output , Can be used for STM32、ADuCM4050 etc. )

STM32:

https://blog.csdn.net/weixin_53403301/article/details/121599951

ADuCM4050:

#ifndef __GPIO_H__

#define __GPIO_H__

#include "ADuCM4050.h"

#include "adi_gpio.h"

#define BITBAND(addr, bitnum) ((addr & 0xF0000000)+0x2000000+((addr &0xFFFFF)<<5)+(bitnum<<2))

#define MEM_ADDR(addr) *((volatile unsigned long *)(addr))

#define BIT_ADDR(addr, bitnum) MEM_ADDR(BITBAND(addr, bitnum))

#define GPIO0_ODR_Addr (ADI_GPIO0_BASE+20) //0x40020014

#define GPIO0_IDR_Addr (ADI_GPIO0_BASE+16) //0x40020010

#define GPIO1_ODR_Addr (ADI_GPIO1_BASE+20) //0x40020054

#define GPIO1_IDR_Addr (ADI_GPIO1_BASE+16) //0x40020050

#define GPIO2_ODR_Addr (ADI_GPIO2_BASE+20) //0x40020094

#define GPIO2_IDR_Addr (ADI_GPIO2_BASE+16) //0x40020090

#define GPIO3_ODR_Addr (ADI_GPIO3_BASE+20) //0x400200D4

#define GPIO3_IDR_Addr (ADI_GPIO3_BASE+16) //0x400200D0

#define P0_O(n) BIT_ADDR(GPIO0_ODR_Addr,n) // Output

#define P0_I(n) BIT_ADDR(GPIO0_IDR_Addr,n) // Input

#define P1_O(n) BIT_ADDR(GPIO1_ODR_Addr,n) // Output

#define P1_I(n) BIT_ADDR(GPIO1_IDR_Addr,n) // Input

#define P2_O(n) BIT_ADDR(GPIO2_ODR_Addr,n) // Output

#define P2_I(n) BIT_ADDR(GPIO2_IDR_Addr,n) // Input

#define P3_O(n) BIT_ADDR(GPIO3_ODR_Addr,n) // Output

#define P3_I(n) BIT_ADDR(GPIO3_IDR_Addr,n) // Input

#define Port0 (ADI_GPIO_PORT0)

#define Port1 (ADI_GPIO_PORT1)

#define Port2 (ADI_GPIO_PORT2)

#define Port3 (ADI_GPIO_PORT3)

#define Pin0 (ADI_GPIO_PIN_0)

#define Pin1 (ADI_GPIO_PIN_1)

#define Pin2 (ADI_GPIO_PIN_2)

#define Pin3 (ADI_GPIO_PIN_3)

#define Pin4 (ADI_GPIO_PIN_4)

#define Pin5 (ADI_GPIO_PIN_5)

#define Pin6 (ADI_GPIO_PIN_6)

#define Pin7 (ADI_GPIO_PIN_7)

#define Pin8 (ADI_GPIO_PIN_8)

#define Pin9 (ADI_GPIO_PIN_9)

#define Pin10 (ADI_GPIO_PIN_10)

#define Pin11 (ADI_GPIO_PIN_11)

#define Pin12 (ADI_GPIO_PIN_12)

#define Pin13 (ADI_GPIO_PIN_13)

#define Pin14 (ADI_GPIO_PIN_14)

#define Pin15 (ADI_GPIO_PIN_15)

void GPIO_OUT(unsigned int port,unsigned int pin,unsigned int flag);

void GPIO_BUS_OUT(unsigned int port,unsigned int num);

void P0_BUS_O(unsigned int num);

unsigned int P0_BUS_I(void);

void P1_BUS_O(unsigned int num);

unsigned int P1_BUS_I(void);

void P2_BUS_O(unsigned int num);

unsigned int P2_BUS_I(void);

void P3_BUS_O(unsigned int num);

unsigned int P3_BUS_I(void);

#endif

#include "ADuCM4050.h"

#include "adi_gpio.h"

#include "GPIO.h"

void GPIO_OUT(unsigned int port,unsigned int pin,unsigned int flag)

{

switch(port)

{

case 0:{

switch(pin)

{

case 0:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_0));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_0));};break;

case 1:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_1));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_1));};break;

case 2:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_2));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_2));};break;

case 3:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_3));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_3));};break;

case 4:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_4));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_4));};break;

case 5:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_5));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_5));};break;

case 6:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_6));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_6));};break;

case 7:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_7));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_7));};break;

case 8:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_8));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_8));};break;

case 9:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_9));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_9));};break;

case 10:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_10));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_10));};break;

case 11:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_11));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_11));};break;

case 12:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_12));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_12));};break;

case 13:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_13));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_13));};break;

case 14:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_14));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_14));};break;

case 15:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT0),(ADI_GPIO_PIN_15));}else{

adi_gpio_SetLow((ADI_GPIO_PORT0),(ADI_GPIO_PIN_15));};break;

default:pin=0;break;

}

}break;

case 1:{

switch(pin)

{

case 0:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_0));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_0));};break;

case 1:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_1));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_1));};break;

case 2:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_2));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_2));};break;

case 3:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_3));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_3));};break;

case 4:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_4));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_4));};break;

case 5:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_5));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_5));};break;

case 6:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_6));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_6));};break;

case 7:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_7));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_7));};break;

case 8:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_8));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_8));};break;

case 9:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_9));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_9));};break;

case 10:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_10));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_10));};break;

case 11:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_11));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_11));};break;

case 12:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_12));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_12));};break;

case 13:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_13));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_13));};break;

case 14:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_14));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_14));};break;

case 15:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT1),(ADI_GPIO_PIN_15));}else{

adi_gpio_SetLow((ADI_GPIO_PORT1),(ADI_GPIO_PIN_15));};break;

default:pin=0;break;

}

}break;

case 2:{

switch(pin)

{

case 0:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_0));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_0));};break;

case 1:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_1));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_1));};break;

case 2:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_2));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_2));};break;

case 3:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_3));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_3));};break;

case 4:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_4));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_4));};break;

case 5:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_5));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_5));};break;

case 6:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_6));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_6));};break;

case 7:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_7));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_7));};break;

case 8:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_8));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_8));};break;

case 9:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_9));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_9));};break;

case 10:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_10));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_10));};break;

case 11:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_11));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_11));};break;

case 12:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_12));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_12));};break;

case 13:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_13));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_13));};break;

case 14:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_14));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_14));};break;

case 15:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT2),(ADI_GPIO_PIN_15));}else{

adi_gpio_SetLow((ADI_GPIO_PORT2),(ADI_GPIO_PIN_15));};break;

default:pin=0;break;

}

}break;

case 3:{

switch(pin)

{

case 0:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_0));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_0));};break;

case 1:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_1));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_1));};break;

case 2:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_2));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_2));};break;

case 3:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_3));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_3));};break;

case 4:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_4));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_4));};break;

case 5:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_5));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_5));};break;

case 6:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_6));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_6));};break;

case 7:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_7));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_7));};break;

case 8:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_8));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_8));};break;

case 9:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_9));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_9));};break;

case 10:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_10));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_10));};break;

case 11:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_11));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_11));};break;

case 12:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_12));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_12));};break;

case 13:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_13));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_13));};break;

case 14:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_14));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_14));};break;

case 15:if(flag==1){

adi_gpio_SetHigh((ADI_GPIO_PORT3),(ADI_GPIO_PIN_15));}else{

adi_gpio_SetLow((ADI_GPIO_PORT3),(ADI_GPIO_PIN_15));};break;

default:pin=0;break;

}

}break;

default:port=0;break;

}

}

void GPIO_BUS_OUT(unsigned int port,unsigned int num) //num The maximum is 0xffff

{

int i;

for(i=0;i<16;i++)

{

GPIO_OUT(port,i,(num>>i)&0x0001);

}

}

void P0_BUS_O(unsigned int num) // The input values num The maximum is 0xFFFF

{

int i;

for(i=0;i<16;i++)

{

P0_O(i)=(num>>i)&0x0001;

}

}

unsigned int P0_BUS_I(void) // Output value num The maximum is 0xFFFF

{

unsigned int num;

int i;

for(i=0;i<16;i++)

{

num=num+(P0_I(i)<<i)&0xFFFF;

}

return num;

}

void P1_BUS_O(unsigned int num) // The input values num The maximum is 0xFFFF

{

int i;

for(i=0;i<16;i++)

{

P1_O(i)=(num>>i)&0x0001;

}

}

unsigned int P1_BUS_I(void) // Output value num The maximum is 0xFFFF

{

unsigned int num;

int i;

for(i=0;i<16;i++)

{

num=num+(P1_I(i)<<i)&0xFFFF;

}

return num;

}

void P2_BUS_O(unsigned int num) // The input values num The maximum is 0xFFFF

{

int i;

for(i=0;i<16;i++)

{

P2_O(i)=(num>>i)&0x0001;

}

}

unsigned int P2_BUS_I(void) // Output value num The maximum is 0xFFFF

{

unsigned int num;

int i;

for(i=0;i<16;i++)

{

num=num+(P2_I(i)<<i)&0xFFFF;

}

return num;

}

void P3_BUS_O(unsigned int num) // The input values num The maximum is 0xFFFF

{

int i;

for(i=0;i<16;i++)

{

P3_O(i)=(num>>i)&0x0001;

}

}

unsigned int P3_BUS_I(void) // Output value num The maximum is 0xFFFF

{

unsigned int num;

int i;

for(i=0;i<16;i++)

{

num=num+(P3_I(i)<<i)&0xFFFF;

}

return num;

}

边栏推荐

猜你喜欢

Get class files and attributes by reflection

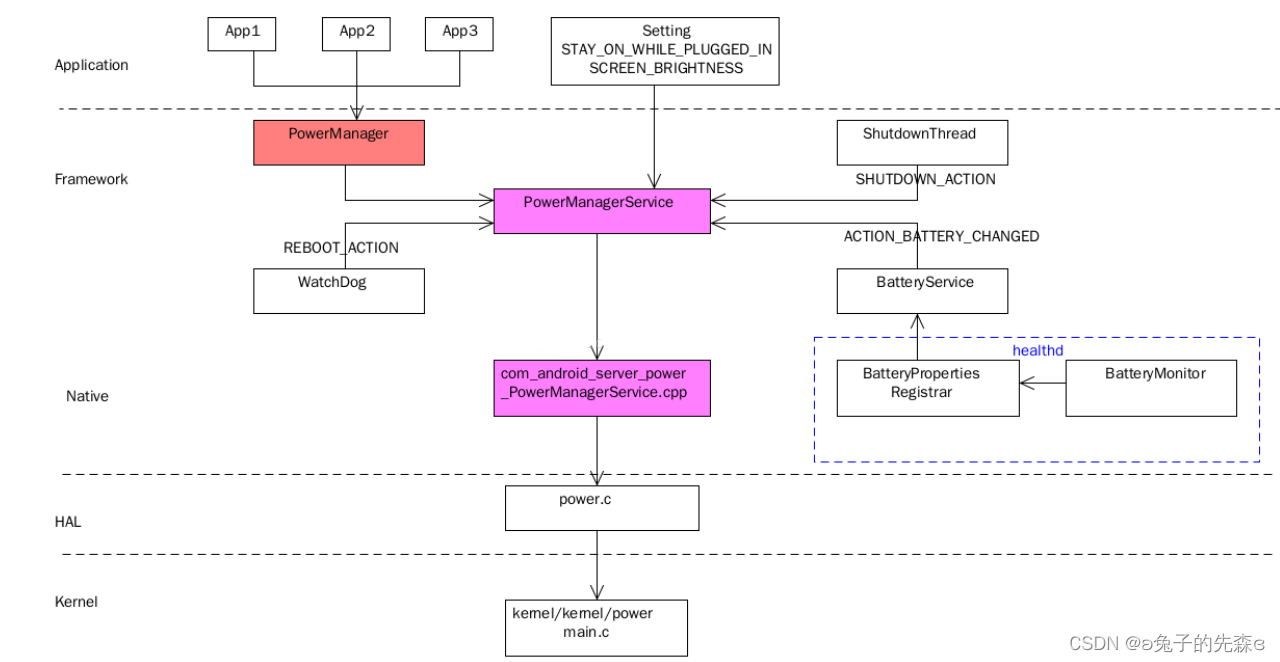

PowerManagerService(一)— 初始化

Pycahrm reports an error: indentation error: unindent does not match any outer indentation

Use ffmpeg to rotate, flip up and down, and flip horizontally

Volcano resource reservation feature

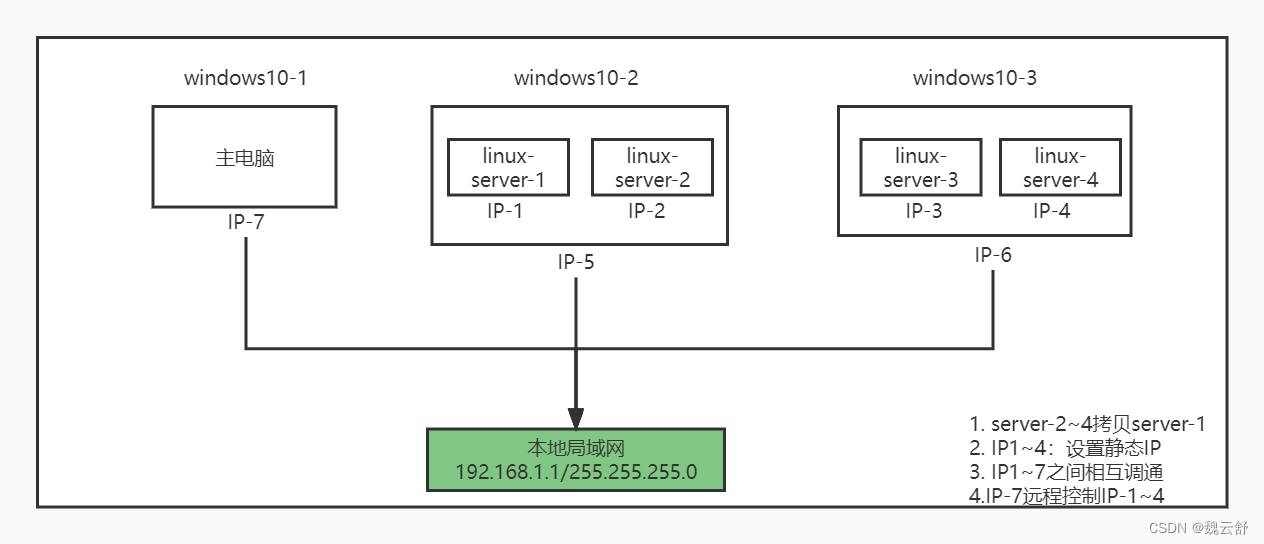

Build a microservice cluster environment locally and learn to deploy automatically

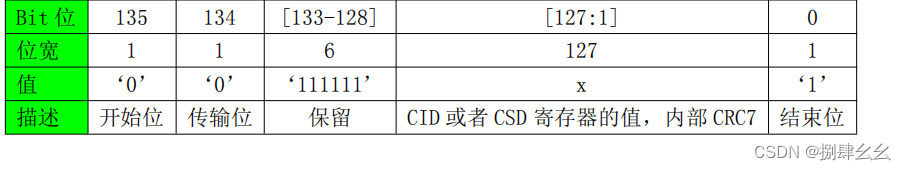

SD_CMD_RECEIVE_SHIFT_REGISTER

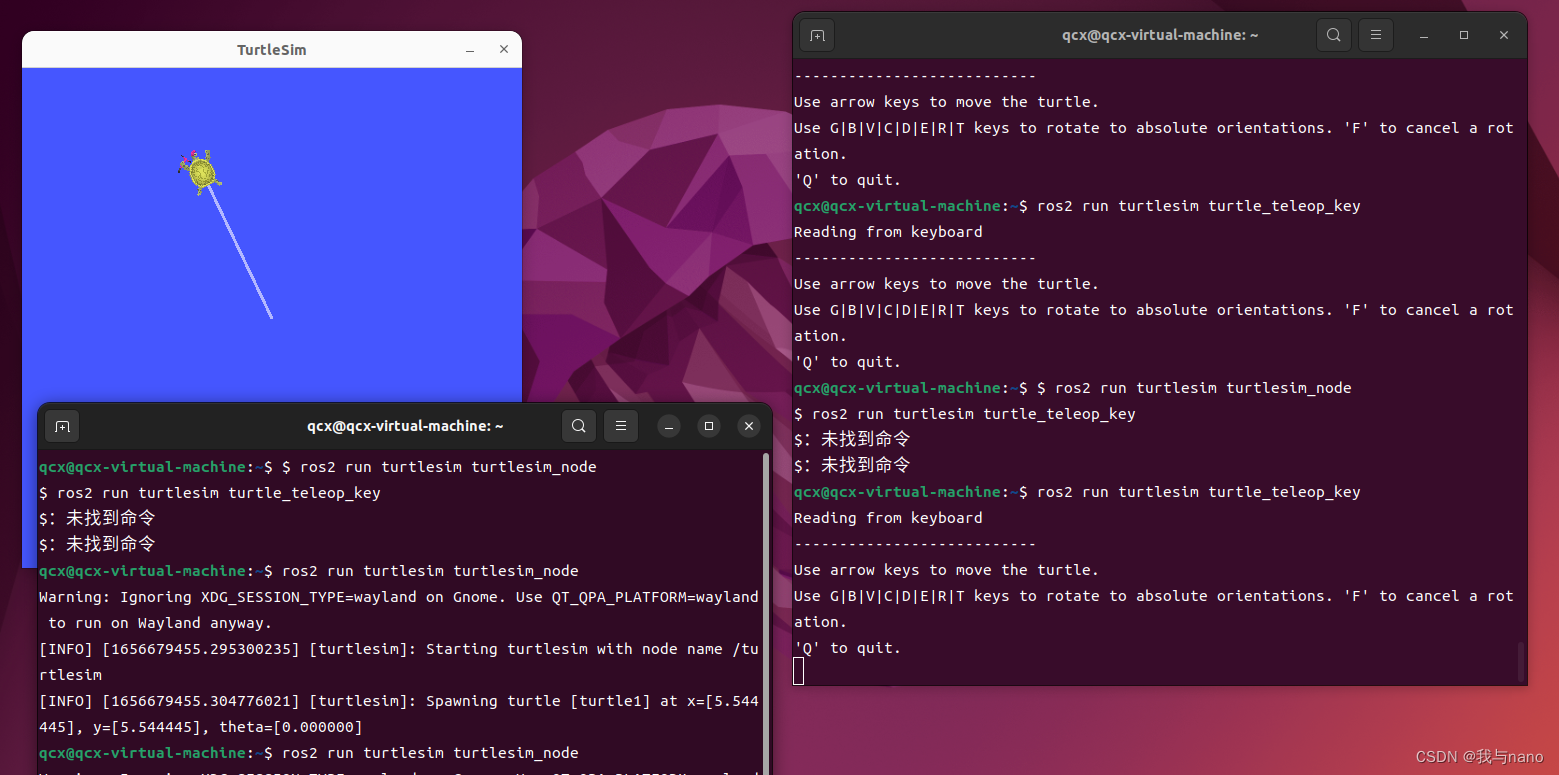

Ros2 - install ros2 (III)

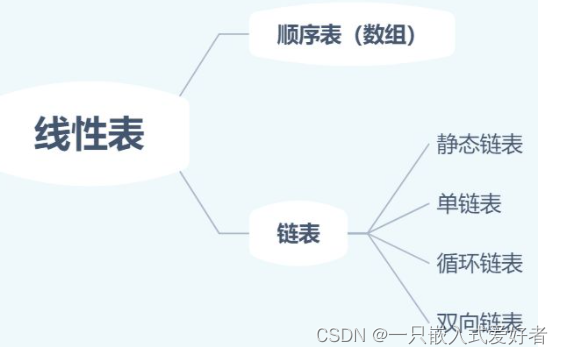

C语言数组专题训练

SOC_SD_DATA_FSM

随机推荐

SOC_SD_DATA_FSM

Instruction execution time

Netease to B, soft outside, hard in

Ros2 - Service Service (IX)

[OBS] x264 Code: "buffer_size“

namespace

Rehabilitation type force deduction brush question notes D3

Ros2 - ros2 vs. ros1 (II)

睿智的目标检测59——Pytorch Focal loss详解与在YoloV4当中的实现

Ros2 - configuration development environment (V)

Pycahrm reports an error: indentation error: unindent does not match any outer indentation

Huawei bracelet, how to add medicine reminder?

[untitled]

*P++, (*p) + +, * (p++) differences

Unity ugui how to match and transform coordinates between different UI panels or uis

Matlab在线性代数中的应用(四):相似矩阵及二次型

Ros2 - workspace (V)

并发编程 — 死锁排查及处理

Database mysql all

cgroup_ memcg