当前位置:网站首页>【数字IC手撕代码】Verilog无毛刺时钟切换电路|题目|原理|设计|仿真

【数字IC手撕代码】Verilog无毛刺时钟切换电路|题目|原理|设计|仿真

2022-07-06 14:21:00 【myhhhhhhhh】

| 芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球 |

|---|

| 四社区联合力荐!近500篇数字IC精品文章收录! |

| 【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 |

Verilog无毛刺时钟切换电路

一、前言

本系列旨在提供100%准确的数字IC设计/验证手撕代码环节的题目,原理,RTL设计,Testbench和参考仿真波形,每篇文章的内容都经过仿真核对。快速导航链接如下:

1.奇数分频

2.偶数分频

3.半整数分批

4.小数/分数分频

5.序列检测器

6.模三检测器

7.饮料机

8.异步复位,同步释放

9.边沿检测(上升沿,下降沿,双边沿)

10.全加器,半加器

11.格雷码转二进制

12.单bit跨时钟域(打两拍,边沿同步,脉冲同步)

13.奇偶校验

14.伪随机数生成器[线性反馈移位寄存器]

15.同步FIFO

16.无毛刺时钟切换电路

应当说,手撕代码环节是面试流程中既重要又简单的一个环节,跟软件类的岗位相比起来,数字IC的手撕代码题目固定,数量有限,属于整个面试中必得分的一个环节,在这个系列以外,笔者同样推荐数字IC求职者使用“HdlBits”进行代码的训练

链接如下

HDLBits — Verilog Practice

二、题目

为了SOC设计的低功耗性,多时钟域的划分是常用手段之一,有两个时钟,A为50Mhz,B为100Mhz,请设计无毛刺时钟切换电路,根据控制信号control,输出所需时钟信号。

三、原理

3.1 有毛刺时钟切换

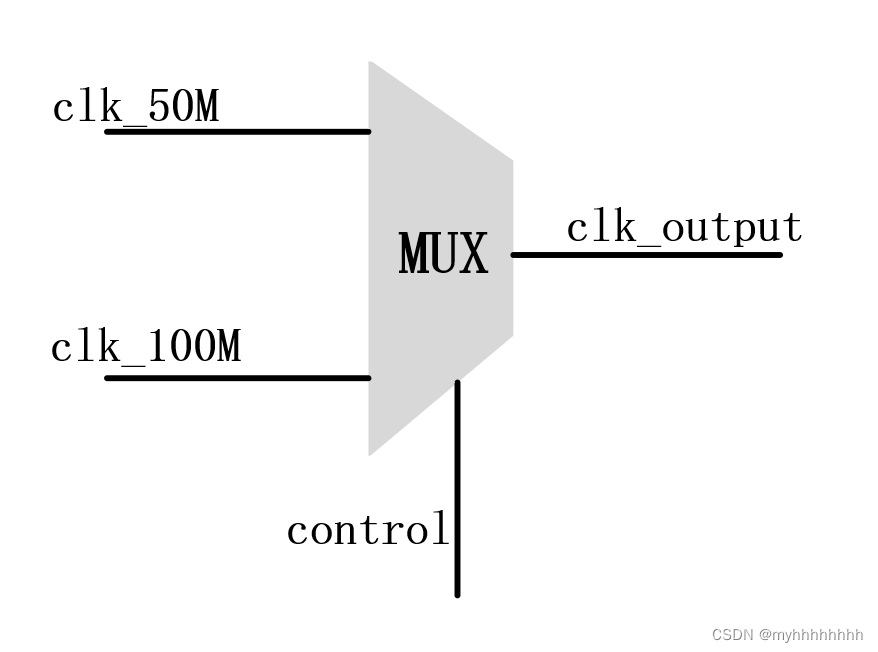

想要切换时钟电路,最简单的方法肯定是使用一个MUX,control作为控制信号

control=1,clk_output = clk_50M,

control=0,clk_output =clk_100M,

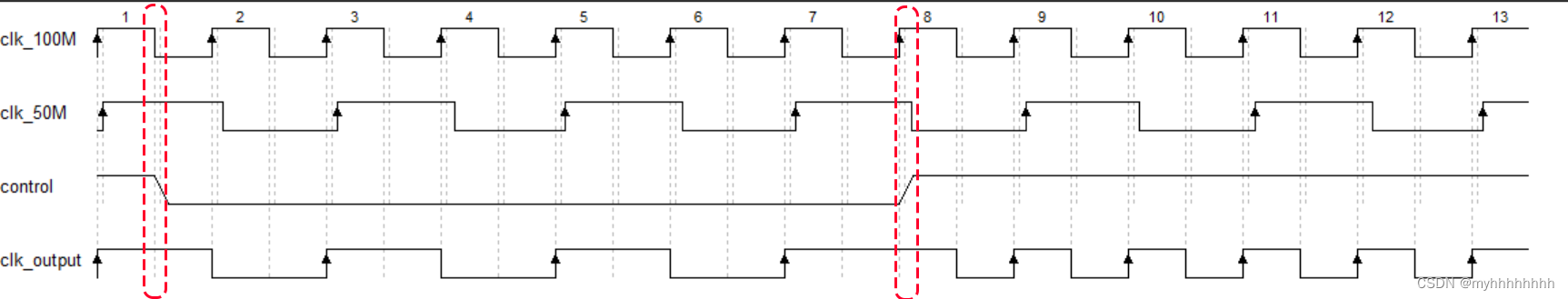

但是这种做法会存在毛刺问题,如图所示,当control信号转换的边缘时,假如clk_50M与clk_100M的边沿没对准,就有可能出现毛刺,影响时钟质量

因此我们需要无毛刺时钟切换电路的帮助,进入下一节

3.2 无毛刺时钟切换

首先我们需要明确的是,毛刺发生的原因

control信号至少对一个时钟信号为异步信号,导致了毛刺的出现,假如control,clk_50M,还是clk_100M都是边沿完全同步的理想信号话,应该是不会出现毛刺的。

所以避免毛刺发生的方法顺理成章地过渡到了“异步信号同步化”这个理论上面,如何做同步呢?

毫无疑问,肯定是需要打拍/采样的方式

上升沿同步还是下降沿同步呢?

这里是上升沿打拍还是下降沿打拍其实是因电路而异的一个问题,我们假如希望最终用与门处理时钟信号和控制信号

即:当control信号为1时,按照时钟输出,control信号为0,输出为0(即相与逻辑)

没有电路会是完全理想的边沿完全同步的信号

假如是上升沿同步control信号,同步的control会比clk的边沿稍微慢一点点,二者相与,肯定会出现毛刺

假如是下降沿同步control有效信号,下降沿到来时,control被同步后为1,clk此时为0,二者相与为0,上升沿到来时,control保持,clk为1,二者相与为1,无毛刺出现,所以用与逻辑的时候,需要采用下降沿去做触发。

只打一拍,够吗?

不够,若control信号的改变恰好在采样边沿,会存在出现亚稳态的风险,所以我们可以打两拍。第一拍可以采用上升沿,第二拍可以采用下降沿。

那只打拍,够吗?

不够,为什么不够呢?

因为只打拍,只能保证各自的控制信号是同步的,无毛刺,但是不能保证切换不产生毛刺,所以我们还需要增加电路来处理切换的过程,假如我们可以在切换的时候排除相邻时钟的影响,是不是就可以完美确保无毛刺的出现了?

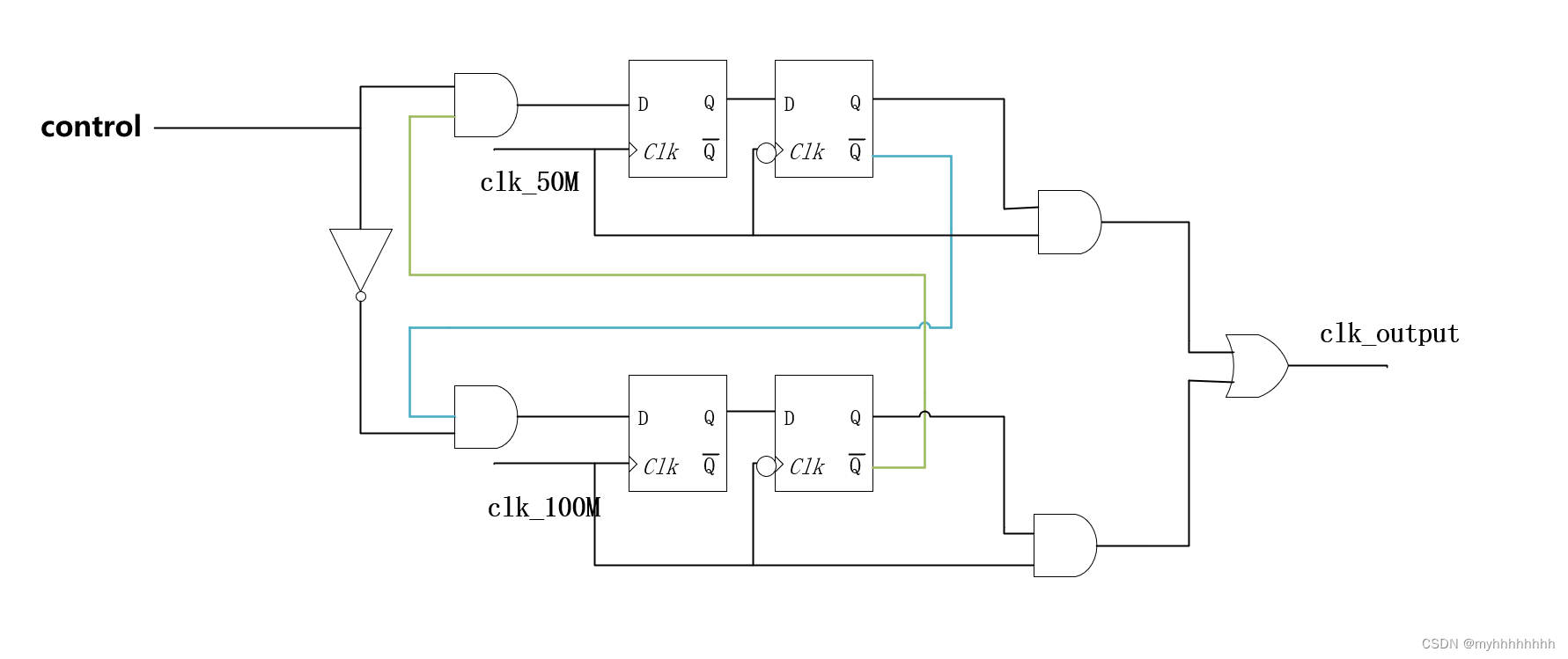

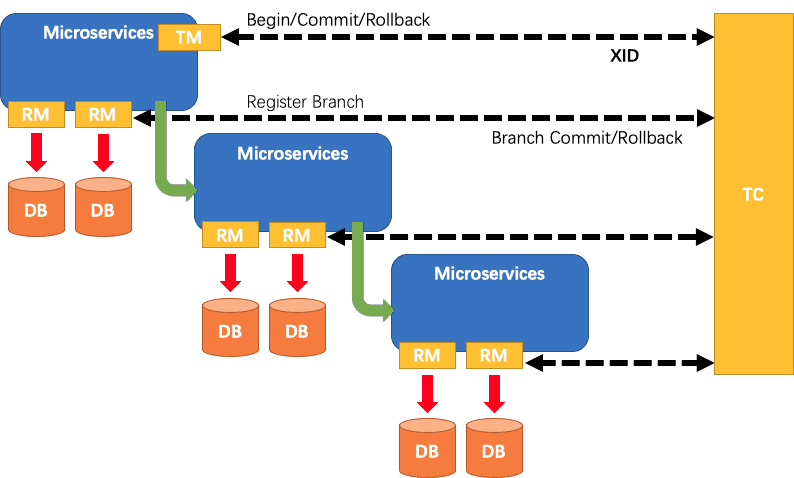

所以以下这张图片可以登场了

- control信号无论是从上面通过还是从下面通过,都经过两级采样,避免了亚稳态的出现

- 后一级的DFF用下降沿采样,避免了采样毛刺的出现

- 第二级DFF的not Q的逻辑以负反馈的形式接回了输入,取了与逻辑,构建起50M时钟和100M时钟的关系,代表着切换前时钟等待一阵子后,才会转换到切换后时钟,避免了切换毛刺的出现

- 最终上面的电路和下面的电路,以或的逻辑相取,输出clk_output.

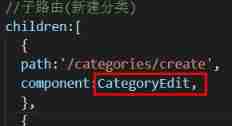

四、RTL设计

module free_glitch(clk_50M,clk_100M,control,rst_n,clk_output);

input clk_50M; // clock with 50M frequency

input clk_100M; // clock with 100M frequency

input control; // control signal

input rst_n; // reset signal

output clk_output; // output clock

reg clk_50_r1; // register for 50M clock

reg clk_50_r2;

reg clk_100_r1;// register for 100M clock

reg clk_100_r2;

wire logic_50_ctl; // logic "and" before DFF_r1 for 50M clock

wire logic_100_ctl; // logic "and" before DFF_r2 for 100M clock

assign logic_50_ctl = control & !clk_100_r2; // generate logic

assign logic_100_ctl = !control & !clk_50_r2; // generate logic

[email protected](posedge clk_50M or negedge rst_n)

if(!rst_n)

clk_50_r1 <= 1'b0;

else

clk_50_r1 <= logic_50_ctl;

[email protected](negedge clk_50M or negedge rst_n)

if(!rst_n)

clk_50_r2 <= 1'b0;

else

clk_50_r2 <= clk_50_r1;

[email protected](posedge clk_100M or negedge rst_n)

if(!rst_n)

clk_100_r1 <= 1'b0;

else

clk_100_r1 <= logic_100_ctl;

[email protected](negedge clk_100M or negedge rst_n)

if(!rst_n)

clk_100_r2 <= 1'b0;

else

clk_100_r2 <= clk_100_r1;

assign clk_output = (clk_100_r2&clk_100M) | (clk_50_r2&clk_50M ); // generate final signal clock output

endmodule

五、仿真

`timescale 1ns / 1ps

module free_glitch_tb();

reg clk_50M;

reg clk_100M;

reg control;

reg rst_n;

wire clk_output;

free_glitch u1(clk_50M,clk_100M,control,rst_n,clk_output);

always #5 clk_100M = !clk_100M;

always #10 clk_50M = !clk_50M;

initial

begin

clk_100M = 0;

clk_50M = 1;

rst_n = 1;

control = 1;

#100

rst_n = 0;

#50

rst_n = 1;

#100

control =0;

#100

control =1;

#128

control = 0;

end

endmodule

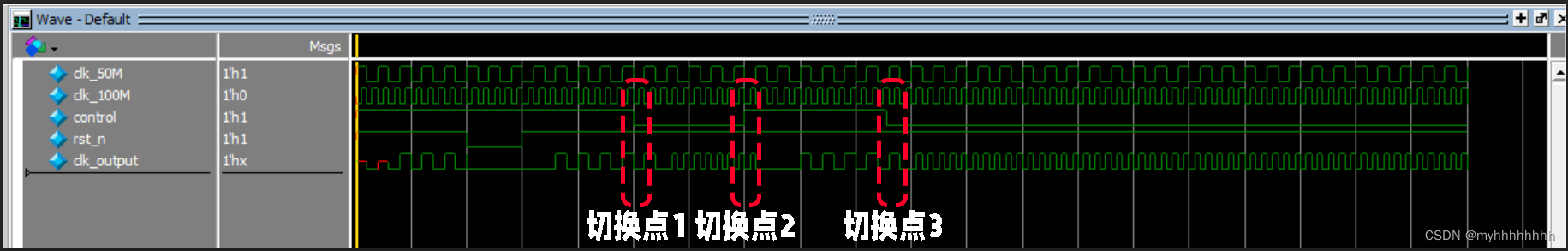

六、仿真分析

我们可以发现,当control变化后,有一段时间的延时,时钟信号才切换至目标的时钟处,就是这段延时的出现,确保了没有毛刺的出现,设计符合需求

边栏推荐

- GPS from getting started to giving up (19), precise ephemeris (SP3 format)

- The golden age of the U.S. technology industry has ended, and there have been constant lamentations about chip sales and 30000 layoffs

- What is the RDD operator in spark

- PVL EDI 项目案例

- 硬件开发笔记(十): 硬件开发基本流程,制作一个USB转RS232的模块(九):创建CH340G/MAX232封装库sop-16并关联原理图元器件

- Write a rotation verification code annotation gadget with aardio

- [asp.net core] set the format of Web API response data -- formatfilter feature

- 用aardio写一个旋转验证码标注小工具

- 20 large visual screens that are highly praised by the boss, with source code templates!

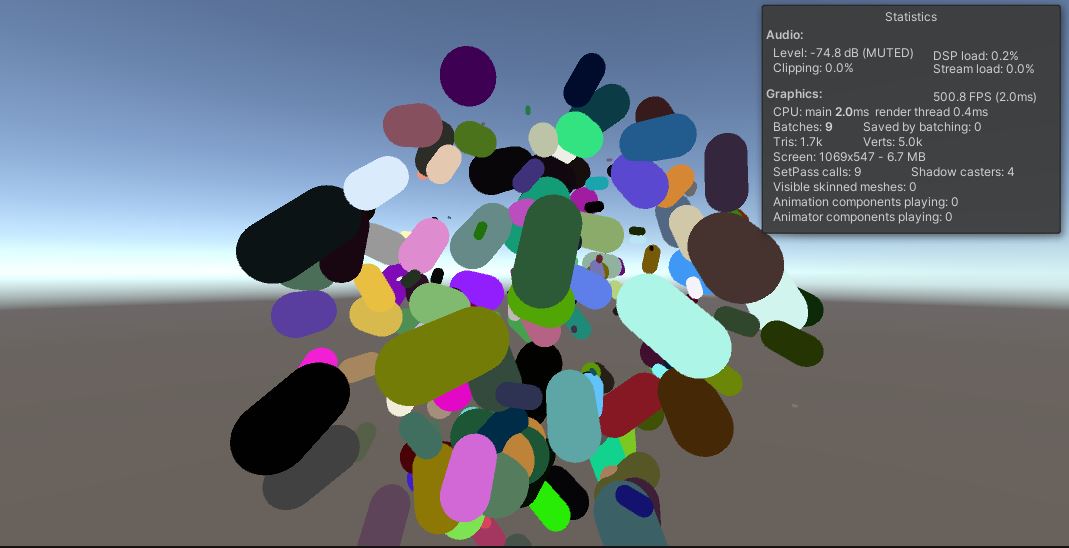

- Unity3D学习笔记6——GPU实例化(1)

猜你喜欢

20 large visual screens that are highly praised by the boss, with source code templates!

Huawei has launched attacks in many industries at the same time, and its frightening technology has made European and American enterprises tremble

Seata聚合 AT、TCC、SAGA 、 XA事务模式打造一站式的分布式事务解决方案

数据处理技巧(7):MATLAB 读取数字字符串混杂的文本文件txt中的数据

C # realizes crystal report binding data and printing 4-bar code

Oracle control file and log file management

Management background --1 Create classification

【MySQL】Online DDL详解

Unity3d Learning Notes 6 - GPU instantiation (1)

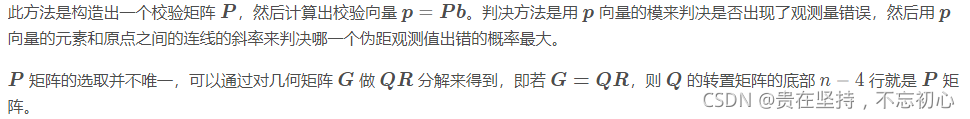

GPS从入门到放弃(十三)、接收机自主完好性监测(RAIM)

随机推荐

[Chongqing Guangdong education] Tianjin urban construction university concrete structure design principle a reference

11、 Service introduction and port

Record the process of cleaning up mining viruses

GPS from getting started to giving up (12), Doppler constant speed

What is the difference between animators and animators- What is the difference between an Animator and an Animation?

GPS from getting started to giving up (XIII), receiver autonomous integrity monitoring (RAIM)

二叉(搜索)树的最近公共祖先 ●●

20 large visual screens that are highly praised by the boss, with source code templates!

LeetCode学习记录(从新手村出发之杀不出新手村)----1

Kohana 数据库

About the professional ethics of programmers, let's talk about it from the way of craftsmanship and neatness

HDR image reconstruction from a single exposure using deep CNNs阅读札记

MariaDb数据库管理系统的学习(一)安装示意图

Codeforces Round #274 (Div. 2) –A Expression

Force buckle 575 Divide candy

[Yu Yue education] reference materials for surgical skills teaching in Tongji University

HDU 2008 digital statistics

Method return value considerations

保存和检索字符串

Mongodb (III) - CRUD