当前位置:网站首页>USB (XVI) 2022-04-28

USB (XVI) 2022-04-28

2022-07-07 23:25:00 【Xiao Xiao and evening rain Xiao Xiao】

The relevant configuration of firmware should be clear before testing , May refer to ( fourteen ); Check the development environment article to understand Control center and Streamer Use , Use test use Streamer Conduct speed test , Make sure FX3 Running on the 3.0 state , Use Control center Complete the basic reading and writing test . In addition, you should know the board information before testing , Modify the corresponding pin mapping .

1. Reading test

The mechanism of lower machine reading test code is to read it all the time as long as there are a few numbers in the buffer , Until the buffer is read empty . In the read operation, use 16kB By the upper computer (control center) Data distribution , If the data is less than 16kB, Notice when sending , Not for 1024bit Multiple , Otherwise, only when the cumulative data reaches 16kB Can only be collected . At the same time, it has been verified , If the data sent by the upper computer is less than 1024 It can also be done through ILA Collect to . adopt GPIF II Interfaces can be FPGA Read , And it can be captured and verified by logic analyzer . among flag_x_d All signals are sampled . The sampled signal is used in the general formula calculation in the case of local signs . Use vivado burning (.bit) Documents are burned at the same time DEBUG(.ltx) The file will pop up ILA display , The trigger signal can be set to slrd_n Falling edge trigger of , Observe ILA Whether the last data captured is consistent with the data sent by the upper computer , Verify the experimental results . meanwhile Make it clear that a cell of the logic analyzer represents writing or reading a data word .

verilog The code is as follows :

边栏推荐

- POJ2392 SpaceElevator [DP]

- 给出一个数组,如 [7864, 284, 347, 7732, 8498],现在需要将数组中的数字拼接起来,返回「最大的可能拼出的数字」

- 三问TDM

- leetcode-520. 检测大写字母-js

- 1. Sum of two numbers

- 聊聊支付流程的设计与实现逻辑

- Wechat forum exchange applet system graduation design completion (1) development outline

- UE4_UE5蓝图command节点的使用(开启关闭屏幕响应-log-发布全屏显示)

- Network security - Eternal Blue

- ArcGIS: field assignment_ The attribute table field calculator assigns values to fields based on conditions

猜你喜欢

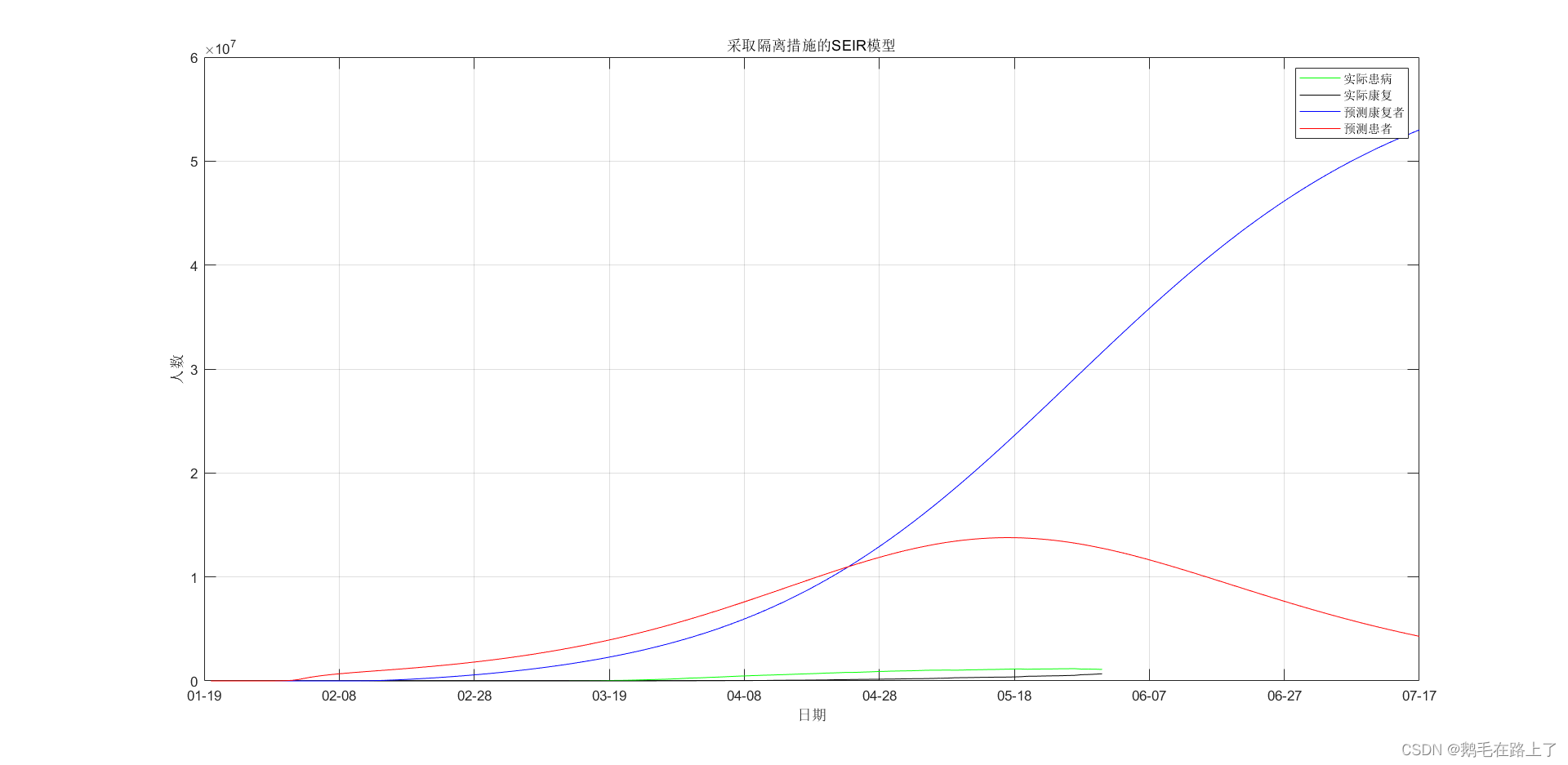

Matlab-SEIR传染病模型预测

包装行业智能供应链S2B2B商城解决方案:开辟电商消费新生态

13、 System optimization

MySQL Index Optimization Practice II

城联优品作为新力量初注入,相关上市公司股价应声上涨150%

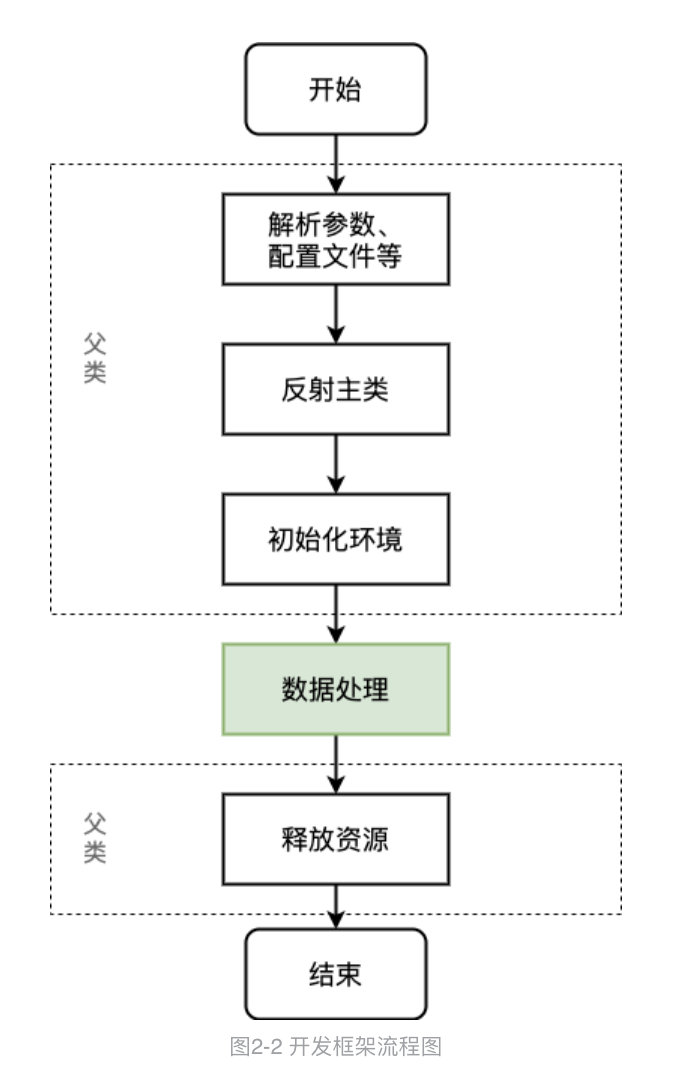

Spark 离线开发框架设计与实现

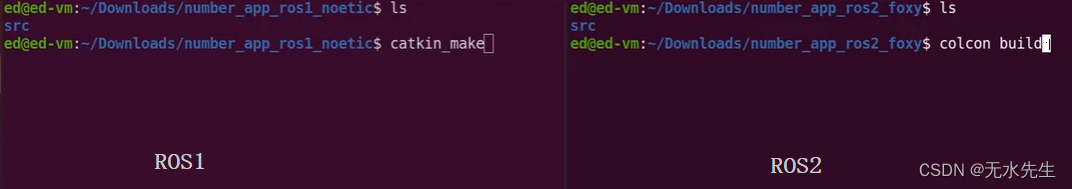

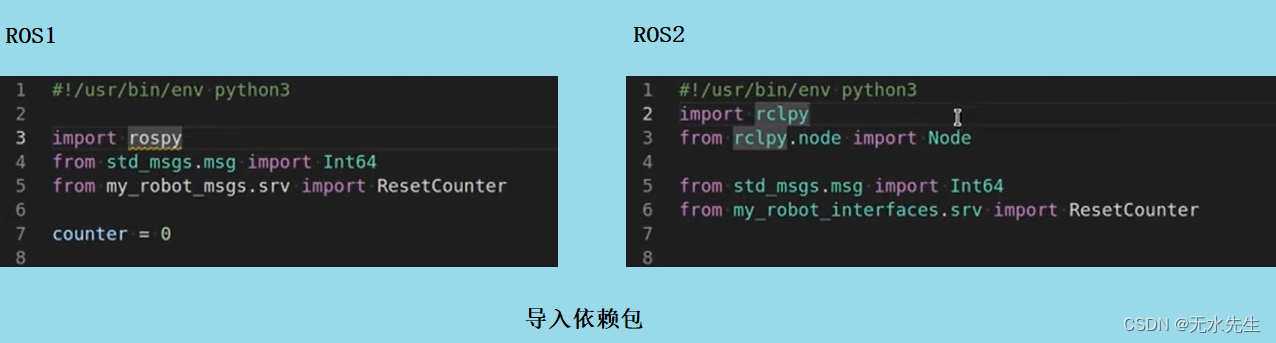

ROS2专题(03):ROS1和ROS2的区别【02】

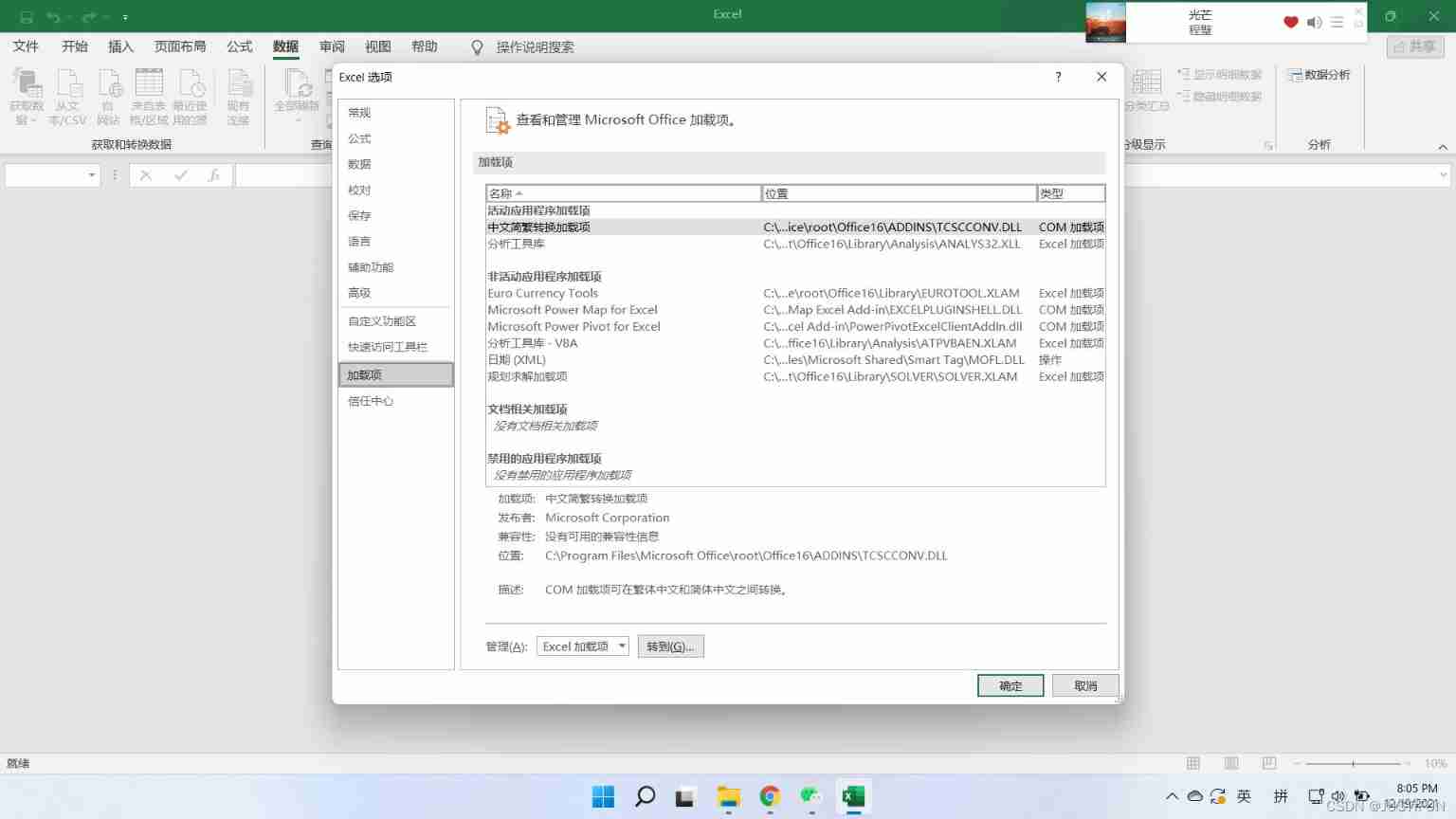

Add data analysis tools in Excel

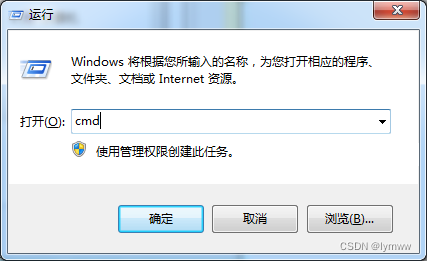

When copying something from the USB flash disk, an error volume error is reported. Please run CHKDSK

ROS2专题(03):ROS1和ROS2的区别【01】

随机推荐

Conversion between commonsmultipartfile and file

UE4_UE5全景相机

USB(十五)2022-04-14

Wechat forum exchange applet system graduation design (2) applet function

System design overview

统计电影票房排名前10的电影并存入还有一个文件

MySQL Index Optimization Practice I

Wechat forum exchange applet system graduation design (3) background function

Coreseek: the second step is index building and testing

Description of longitude and latitude PLT file format

欢聚时代一面

How to generate unique file names

Explain

Unity3D学习笔记6——GPU实例化(1)

违法行为分析1

Oracle-数据库的备份与恢复

What are the similarities and differences between smart communities and smart cities

Coreseek:第二步建索引及測试

Bea-3xxxxx error code

1. Sum of two numbers