当前位置:网站首页>【FPGA教程案例8】基于verilog的分频器设计与实现

【FPGA教程案例8】基于verilog的分频器设计与实现

2022-07-04 06:40:00 【fpga和matlab】

---------------------------------------------------------------------------------------

1.软件版本

vivado2019.2

2.本算法理论知识和Verilog程序

在实际FPGA开发过程中,系统的时钟clk往往较大,而实际所需要的时钟频率较低,那么需要将系统时钟的频率进行分频,得到频率较低的时钟信号。在本课程中,将通过计数器来实现时钟分频。计数器的实现过程可复习上一课程。

【FPGA教程案例7】基于verilog的计数器设计与实现

这里,在该计数器的基础上,增加如下的verilog程序:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/02 22:35:42

// Design 边栏推荐

- Wechat applet scroll view component scrollable view area

- tars源码分析之4

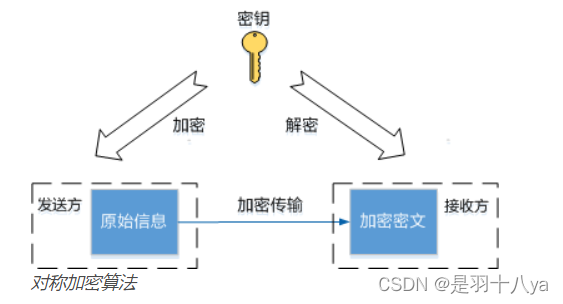

- C # symmetric encryption (AES encryption) ciphertext results generated each time, different ideas, code sharing

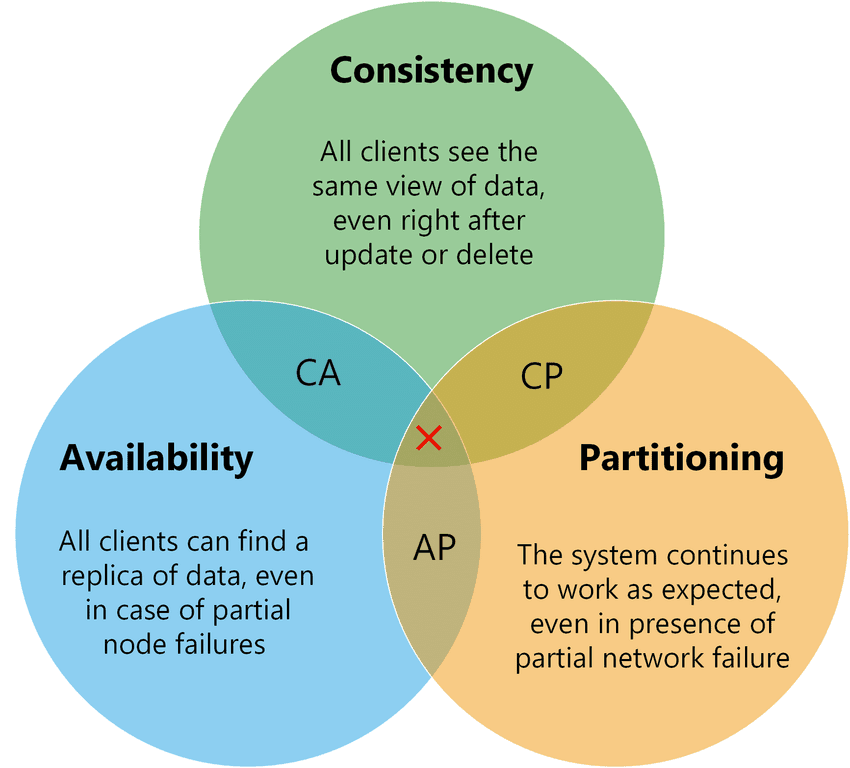

- 分布式CAP理论

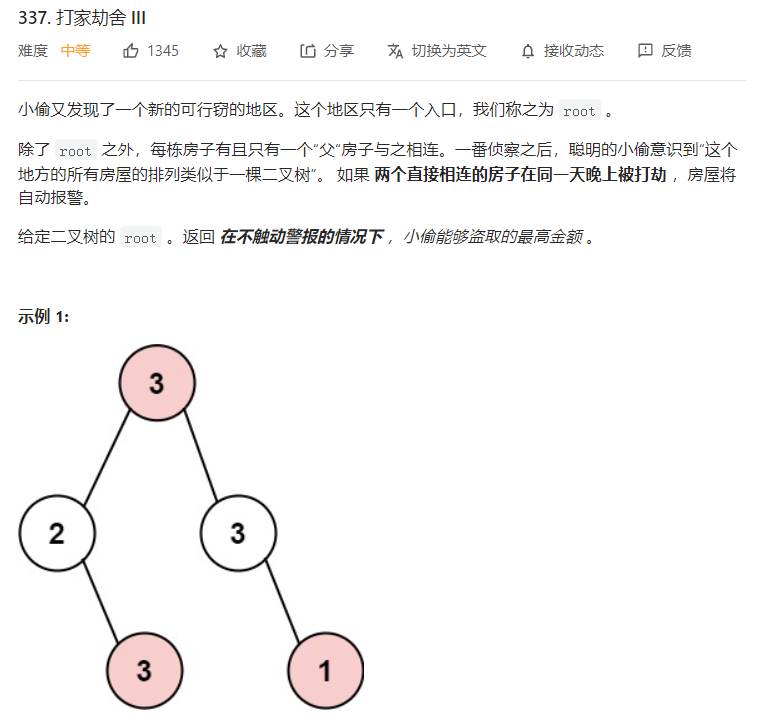

- 198. House raiding

- Fundamentals of SQL database operation

- Vant --- detailed explanation and use of list component in vant

- tcp socket 的 recv 如何接收指定长度消息?

- 图的底部问题

- 11. Dimitt's law

猜你喜欢

Native Cloud - SSH articles must be read on Cloud (used for Remote Login to Cloud Server)

【MySQL】数据库视图的介绍、作用、创建、查看、删除和修改(附练习题)

Tree DP

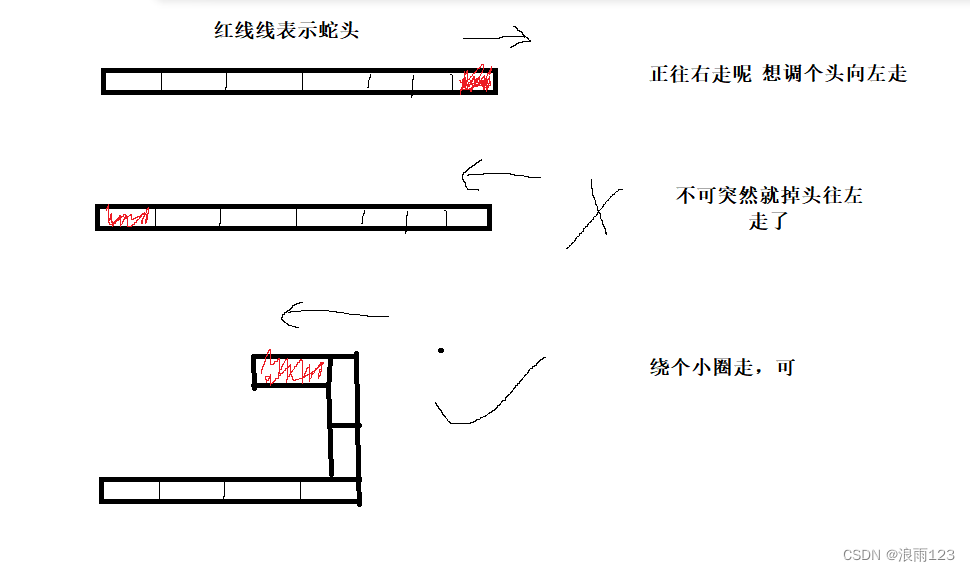

C réaliser des jeux de serpents gourmands

Which water in the environment needs water quality monitoring

Distributed cap theory

The solution of win11 taskbar right click without Task Manager - add win11 taskbar right click function

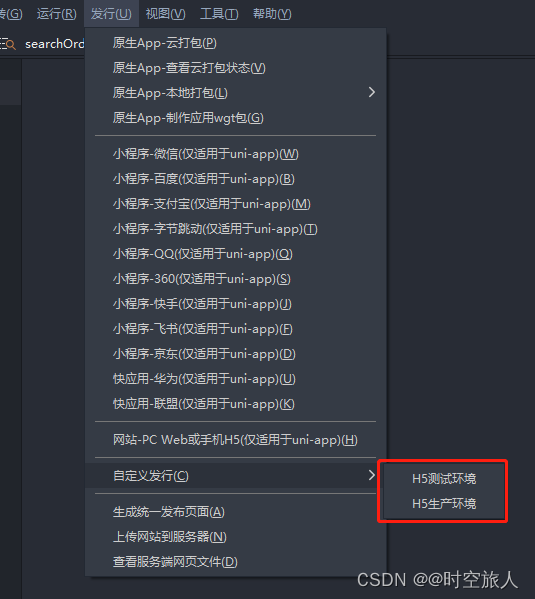

uniapp 自定义环境变量

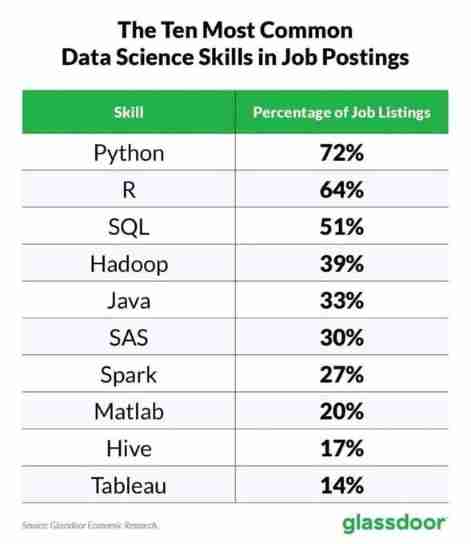

List of top ten professional skills required for data science work

![[March 3, 2019] MAC starts redis](/img/ff/88638fcdc8d24dc268781c224e8195.jpg)

[March 3, 2019] MAC starts redis

随机推荐

tars源码分析之9

同一个job有两个source就报其中一个数据库找不到,有大佬回答下吗

颈椎、脚气

2022年,或許是未來10年經濟最好的一年,2022年你畢業了嗎?畢業後是怎麼計劃的?

C # symmetric encryption (AES encryption) ciphertext results generated each time, different ideas, code sharing

Fundamentals of SQL database operation

Appium foundation - appium installation (II)

[March 3, 2019] MAC starts redis

4G wireless all network solar hydrological equipment power monitoring system bms110

Appium基础 — APPium安装(二)

uniapp 自定义环境变量

SQL injection SQL lab 11~22

Mysql 45讲学习笔记(十二)MySQL会“抖”一下

tcp socket 的 recv 如何接收指定长度消息?

STC8H开发(十二): I2C驱动AT24C08,AT24C32系列EEPROM存储

tars源码分析之2

MySQL 45 learning notes (XI) how to index string fields

Arcpy uses the updatelayer function to change the symbol system of the layer

树形dp

Abap:ooalv realizes the function of adding, deleting, modifying and checking