当前位置:网站首页>(4) UART application design and simulation verification 2 - RX module design (stateless machine)

(4) UART application design and simulation verification 2 - RX module design (stateless machine)

2022-07-05 23:17:00 【Shaoqing is not in Dali Temple】

Removed state machine RX How to design the module ? First sort out which modules to complete

1) Determine when data is received ? That is to detect start position , By detecting the falling edge, it is determined to start receiving data .—— negedge_detect

2) Determine the time period for receiving single frame data ? Detected from start Bit start , Until the last stop bit is passed . A total of 11 individual bit position , Then again 12 individual bit It can be closed halfway through the bit .——start_recieve_flag

3) Every time bit Count clk, Enter the data receiving area and then start counting , Clear when you leave this area .——baud_cnt

4) Calculation bit Count ,1bit Start bit +8bit Valid data bits +1bit Check bit +2bit Stop bit .—— bit_cnt

5) The data transfer , Data reception of valid data bits ,bit_cnt>=1,bit_cnt<=8——rx_data

6) data verification ,check_mode_bit,^{rx_data,check_mode_bit} == CHECKMODE

//2022.6.30

//edgar.yao

//uart rx blaock

module uart_rx(

input clk,

input rst_n,

input rx,

output[7:0] rx_data,

output rx_data_valid

);

parameter CHECKMODE = 1;

parameter BAUD_NUM = 50_000_000/115200;

//(1)define all 边栏推荐

- 数据库基础知识(面试)

- 2022 registration examination for safety management personnel of hazardous chemical business units and simulated reexamination examination for safety management personnel of hazardous chemical busines

- regular expression

- Three.js-01 入门

- 东南亚电商指南,卖家如何布局东南亚市场?

- Finally understand what dynamic planning is

- [digital signal denoising] improved wavelet modulus maxima digital signal denoising based on MATLAB [including Matlab source code 1710]

- 2022 R2 mobile pressure vessel filling review simulation examination and R2 mobile pressure vessel filling examination questions

- TOPSIS code part of good and bad solution distance method

- asp.net弹出层实例

猜你喜欢

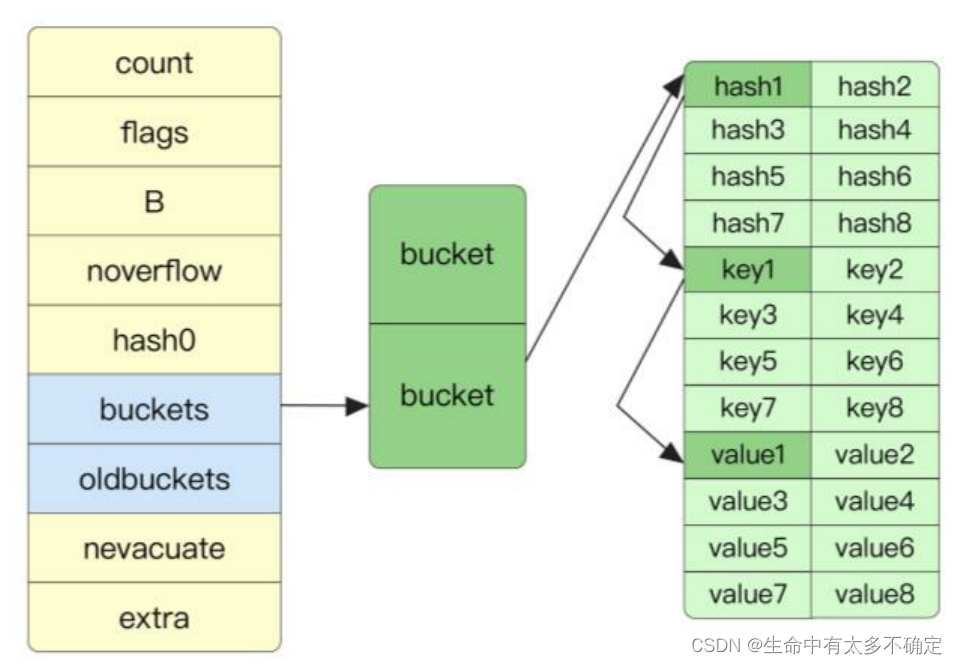

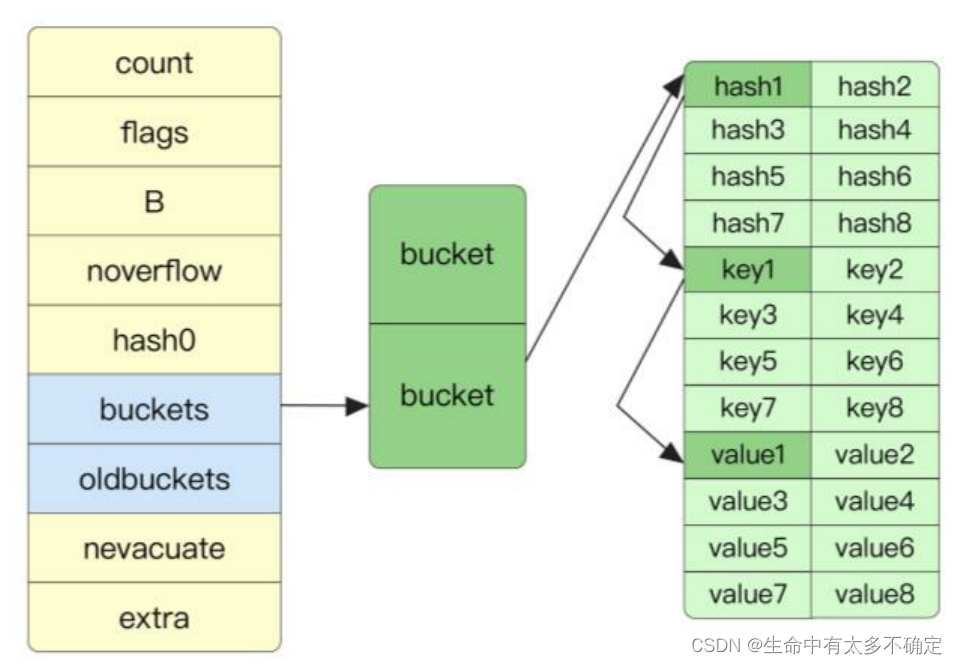

Go language implementation principle -- map implementation principle

![[digital signal denoising] improved wavelet modulus maxima digital signal denoising based on MATLAB [including Matlab source code 1710]](/img/b4/af689abb3ad4e25988f2d17152406e.jpg)

[digital signal denoising] improved wavelet modulus maxima digital signal denoising based on MATLAB [including Matlab source code 1710]

![Development specification: interface unified return value format [resend]](/img/3e/8751b818147cabbe22e4ce44af7d24.jpg)

Development specification: interface unified return value format [resend]

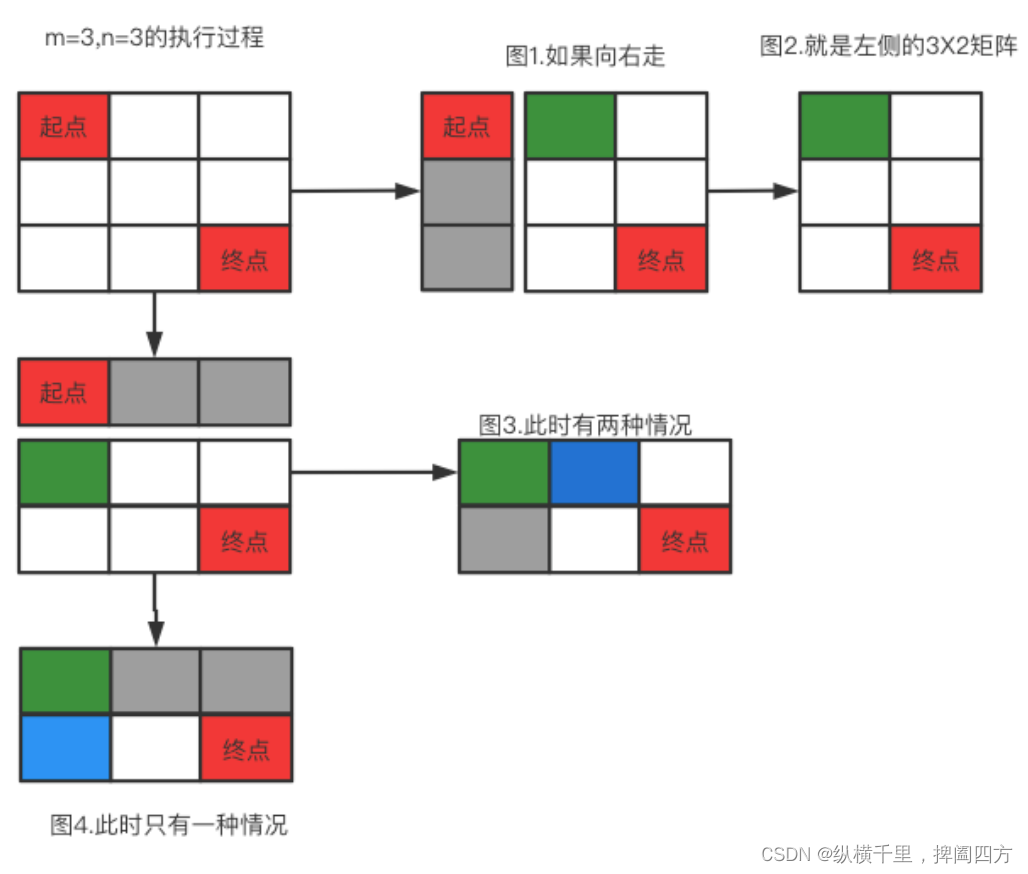

Finally understand what dynamic planning is

Hcip day 12 (BGP black hole, anti ring, configuration)

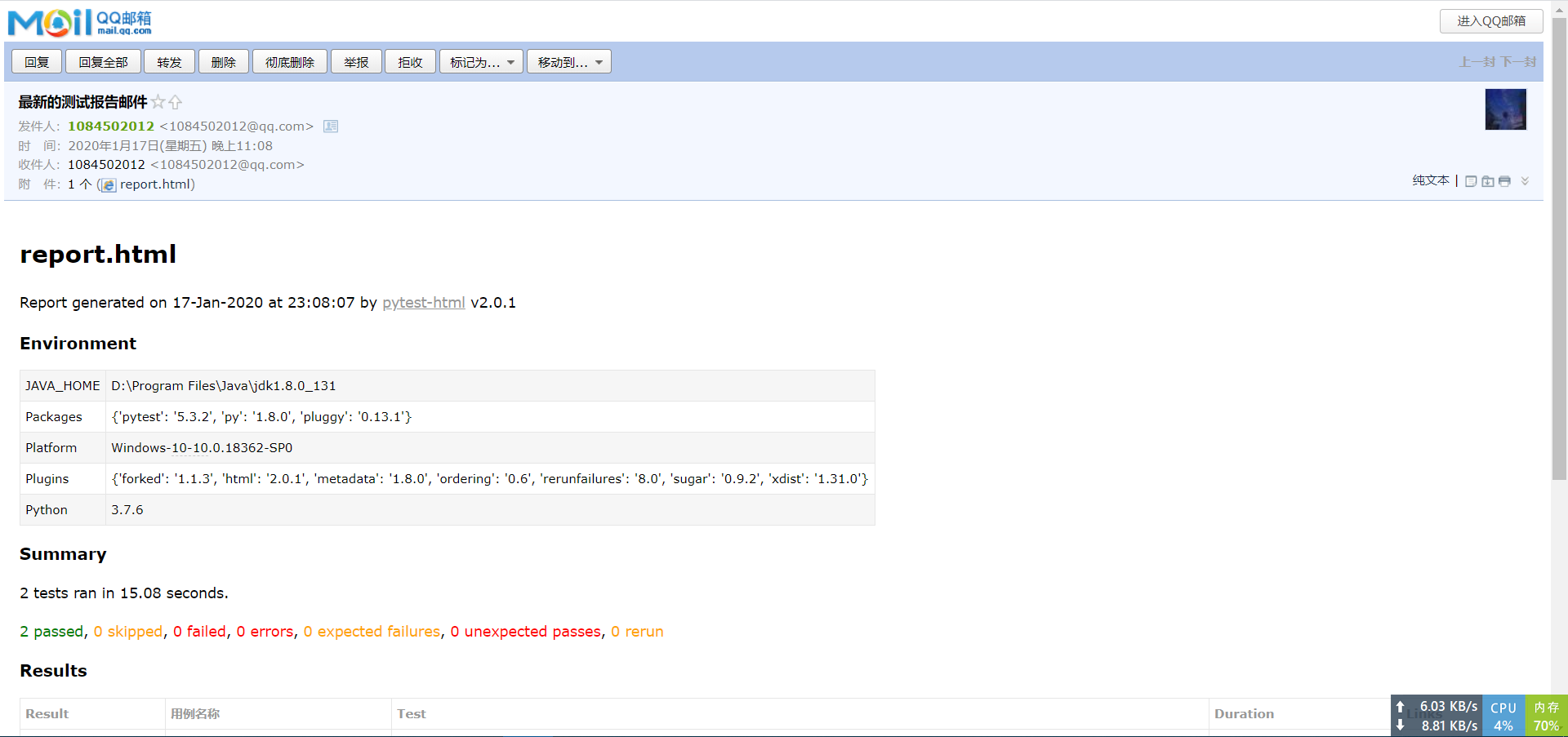

Selenium+Pytest自动化测试框架实战

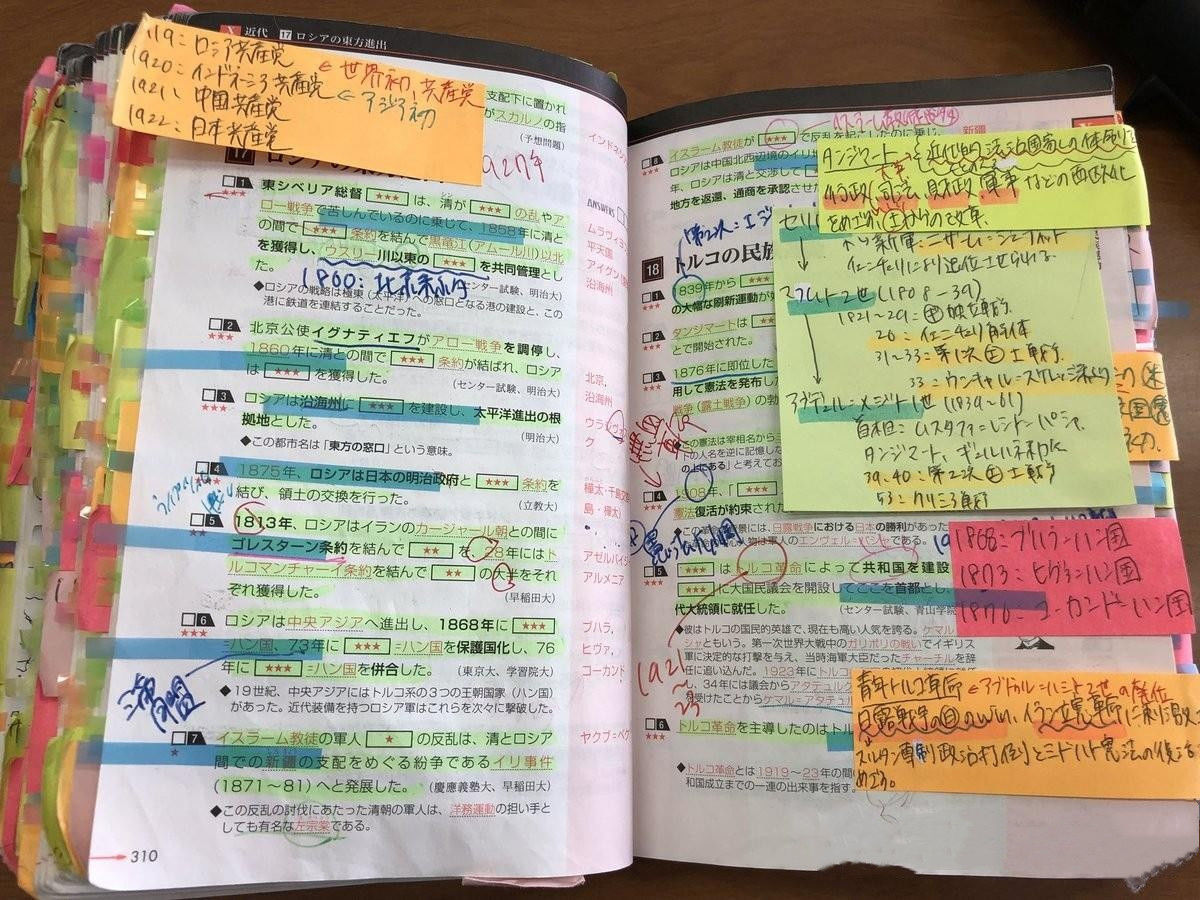

14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!

Go语言实现原理——Map实现原理

【Note17】PECI(Platform Environment Control Interface)

The PNG image is normal when LabVIEW is opened, and the full black image is obtained when Photoshop is opened

随机推荐

2.13 summary

两数之和、三数之和(排序+双指针)

2022 R2 mobile pressure vessel filling review simulation examination and R2 mobile pressure vessel filling examination questions

Summary of binary tree recursive routines

2022 G3 boiler water treatment simulation examination and G3 boiler water treatment simulation examination question bank

【原创】程序员团队管理的核心是什么?

[untitled]

Finally understand what dynamic planning is

Leetcode buys and sells stocks

Marginal probability and conditional probability

Basic knowledge of database (interview)

Negative sampling

3: Chapter 1: understanding JVM specification 2: JVM specification, introduction;

The PNG image is normal when LabVIEW is opened, and the full black image is obtained when Photoshop is opened

11gR2 Database Services for &quot;Policy&quot; and &quot;Administrator&quot; Managed Databases (文件 I

Hainan Nuanshen tea recruits warmhearted people: recruitment of the product experience recommender of Nuanshen multi bubble honey orchid single cluster

There are 14 God note taking methods. Just choose one move to improve your learning and work efficiency by 100 times!

JVM的简介

C Primer Plus Chapter 9 question 10 binary conversion

Expectation, variance and covariance