当前位置:网站首页>[FPGA tutorial case 10] design and implementation of complex multiplier based on Verilog

[FPGA tutorial case 10] design and implementation of complex multiplier based on Verilog

2022-07-05 00:54:00 【FPGA and MATLAB】

---------------------------------------------------------------------------------------

1. Software version

vivado2019.2

2. This algorithm has theoretical knowledge and Verilog Program

In digital signal processing , Complex multiplication has many applications , Including signal mixing ,FFT,IFFT. The calculation formula of complex multiplier is as follows :

Set the plural number

x = a + b i,

y = c + d i,

Then the result of multiplication of complex numbers is :

x * y = (a + b i)*(c + d i) = (ac - bd) + i (ad + bc) .

From this we can see that , A complex multiplier , Including four multipliers ( complete a*c,b*d,a*d as well as b*c), Three adders .

The implementation of multiplier , Refer to the previous course :

边栏推荐

- 兩個數相互替換

- Playwright之录制

- Check if this is null - checking if this is null

- P3304 [SDOI2013]直径(树的直径)

- P4281 [ahoi2008] emergency assembly / gathering (LCA)

- Inventory of more than 17 typical security incidents in January 2022

- Poap: the adoption entrance of NFT?

- Multilingual Wikipedia website source code development part II

- 资深测试/开发程序员写下无bug?资历(枷锁)不要惧怕错误......

- User login function: simple but difficult

猜你喜欢

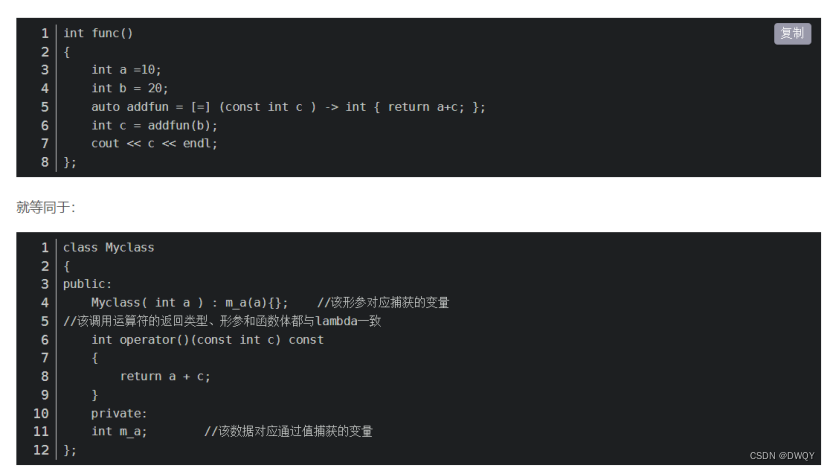

lambda expressions

26.2 billion! These universities in Guangdong Province have received heavy support

“薪資倒掛”、“畢業生平替” 這些現象說明測試行業已經...

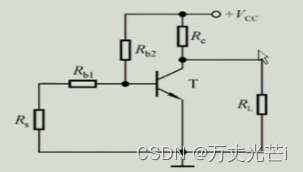

基本放大电路的学习

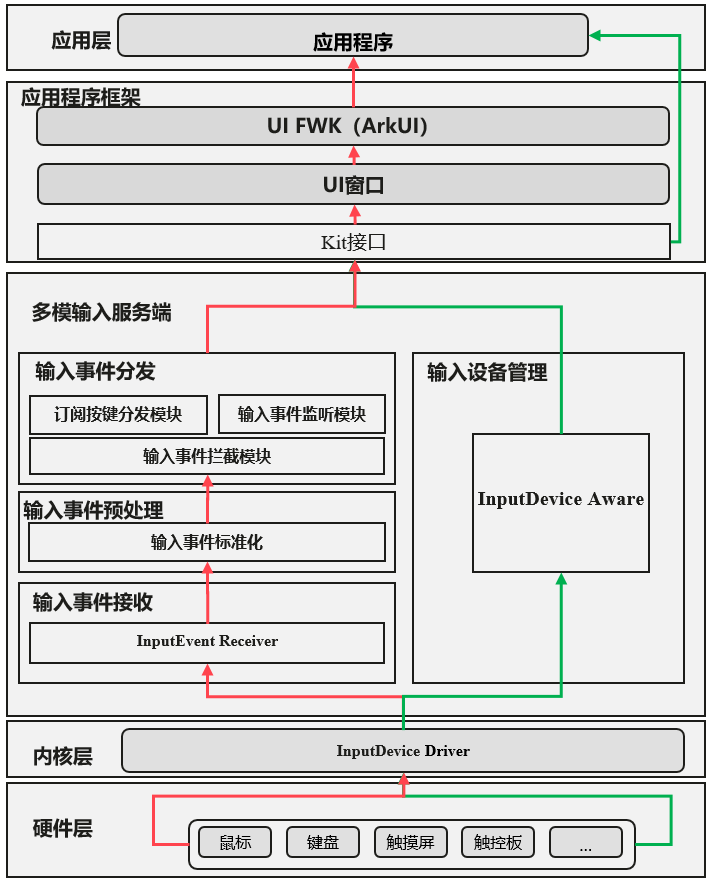

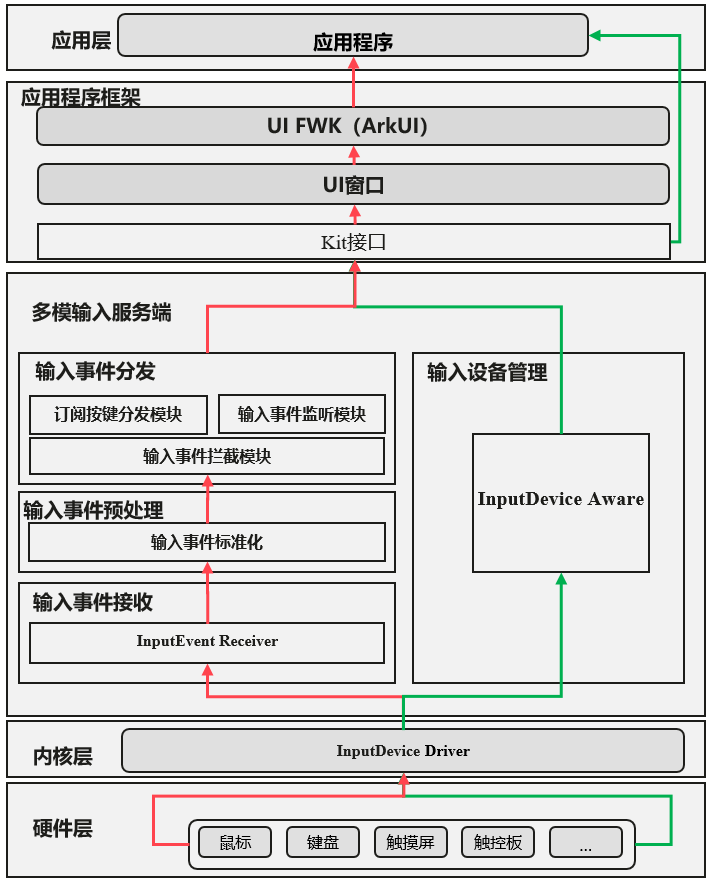

多模输入事件分发机制详解

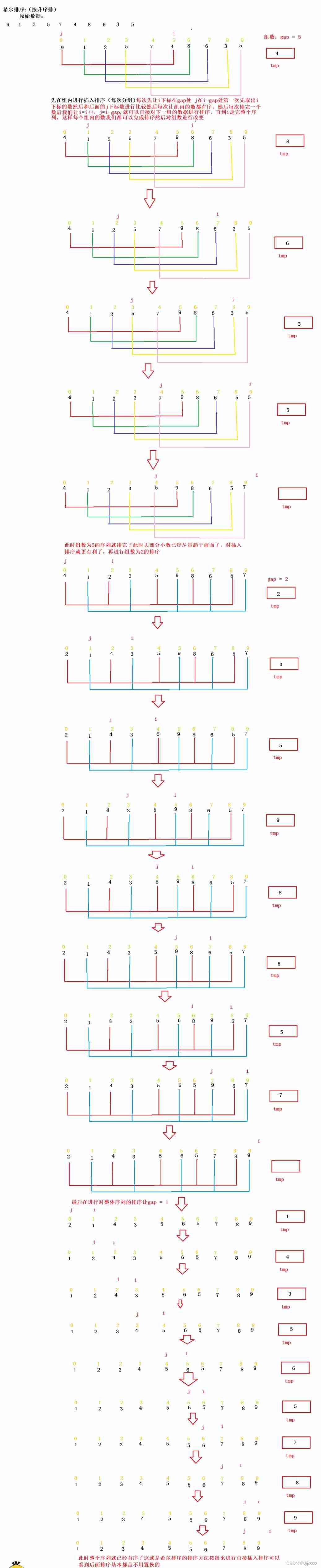

Hill sort of sorting

Detailed explanation of multi-mode input event distribution mechanism

Deux nombres se remplacent

两个数相互替换

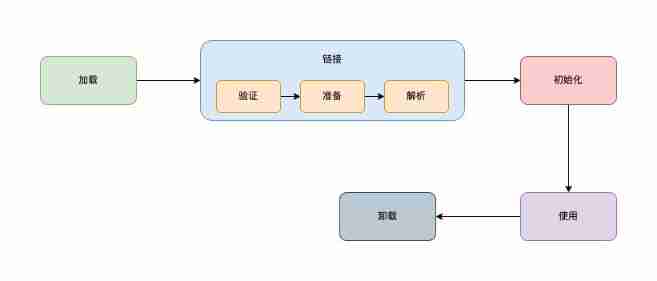

Talking about JVM 4: class loading mechanism

随机推荐

Introduction to the gtid mode of MySQL master-slave replication

华为200万年薪聘请数据治理专家!背后的千亿市场值得关注

全网最全正则实战指南,拿走不谢

Maximum number of "balloons"

SAP UI5 应用的主-从-从(Master-Detail-Detail)布局模式的实现步骤

[STM32] (I) overview and GPIO introduction

7. Scala process control

Detailed explanation of multi-mode input event distribution mechanism

FEG founder rox:smartdefi will be the benchmark of the entire decentralized financial market

【FPGA教程案例10】基于Verilog的复数乘法器设计与实现

[error reporting] "typeerror: cannot read properties of undefined (reading 'split')“

Liangzai's first program life and annual summary in 2022

"Upside down salary", "equal replacement of graduates" these phenomena show that the testing industry has

Distributed base theory

leetcode494,474

有哪些收益稳定的理财产品,这两个都不错

资深测试/开发程序员写下无bug?资历(枷锁)不要惧怕错误......

Hologres query management and timeout processing

ORB(Oriented FAST and Rotated BRIEF)

abc 258 G - Triangle(bitset)