当前位置:网站首页>FPGA课程:JESD204B的应用场景(干货分享)

FPGA课程:JESD204B的应用场景(干货分享)

2022-07-07 02:14:00 【MDYFPGA】

本文为明德扬原创文章,转载请注明出处!

一,JESD204B应用的优缺点

接触过FPGA高速数据采集设计的朋友,应该会听过新术语“JESD204B”。这是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC的采样速率变得越来越高,数据的吞吐量越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,如果依旧采用传统的CMOS和LVDS已经很难满足设计要求,因此“JESD204B”应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口。

与LVDS及CMOS接口相比,JESD204B数据转换器串行接口标准可提供一些显着的优势,比如更简单的布局以及更少的引脚数。也因此它获得了更多工程师的青睐和关注,它具备如下系统级优势:

1、更小的封装尺寸与更低的封装成本:JESD204B不仅采用8b10b编码技术串行打包数据,而且还有助于支持高达12.5Gbps的数据速率。显著减少数据转换器和FPGA上所需的引脚数,从而可帮助缩小封装尺寸,降低封装成本;

2、简化的PCB布局与布线:更少的引脚数可显着简化PCB布局与布线,因为电路板上的路径更少。由于对畸变管理的需求降低,因此布局和布线可进一步简化。这是因为数据时钟嵌入在数据流中,并在接收器中与弹性缓冲器结合,无需通过“波形曲线”来匹配长度。下方图片是JESD204B接口对简化PCB布局有多大帮助的实例;

3、高灵活布局:JESD204B对畸变要求低,可实现更远的传输距离。这有助于将逻辑器件部署在距离数据转换器更远的位置,以避免对灵敏模拟器件产生影响;

4、更简单的时序控制;

5、满足未来需求:该接口能够自适应不同数据转换器分辨率。对于未来模数转换器(ADC)及数模转换器(DAC)而言,无需对TX/RX电路板进行物理上的重新设计。

图:LVDSDAC的PCB布局(左);采用JESD204B的相同DAC的PCB布局(右)

下表是JESD204B、LVDS接口之间的对比:

既然JESD204B接口的优点如此多,这是不是意味着大家都要选取JESD204B接口了呢?

不一定。与LVDS接口相比,JESD204B的缺点是具有更长的绝对时延,这对于有些应用来说是不可接受的。

尽管JESD204B可提供很多优势,但有些应用要求极短的时延,最好是无时延。一个很好的实例是电子战中使用的信号屏蔽器。该设备不仅要求绝对时延,而且需要最大限度地降低任何可能的延迟。

对于这种应用,依旧应该考虑使用LVDS接口,因此它没有在JESD204B上进行数据串行化的延迟。

二,JESD204B协议相关介绍

1、什么是JESD204B协议

该标准描述的是转换器与其所连接的器件(一般为FPGA和ASIC)之间的数GB级串行数据链路,实质上,具有高速并串转换的作用。

a.不用再使用数据接口时钟(时钟嵌入在比特流中,利用恢复时钟技术CDR)

b.不用担心信道偏移(信道对齐可修复此问题,RX端FIFO缓冲器)

c.不用再使用大量IO口,布线方便(高速串行解串器实现高吞吐量)

d.多片IC同步方便

JESD204A和JESD204B参数对比如下图所示:

3、关键变量

M:converters/device,转换器(AD/DA)数量

L:lanes/device(link),通道数量

F:octets/frame(perlane),每帧的8位字节数

K:frames/multiframe,每个多帧的帧数

N:converterresolution,转换器分辨率

N’:totalbits/sample,4的倍数,N’=N+控制和伪数据位。

S:samples/converter/framecycle,每个转换器每帧发送的样本数。当S=1时,帧时钟=采样时钟

CS:controlbits/sample

CF:controlwords/framecycle/device(link),通常只在HD=1时使用。

4、subclass0~2确定延迟

subclass0:不支持确定延迟;

subclass1:SYSREF,(AD9370支持的是子类1,IP核默认也是子类1),利用确定延迟来对齐多片IC;

subclass2:SYNC~。

5、subclass1的三个阶段

A、第一阶段,代码组同步(CGS)

a、RX将SYNC~引脚拉低,发出一个同步请求。

b、TX从下一个符号开始,发送未加扰的/K28.5/符号(每个符号10位)。

c、当RX接收到至少4个无错误的连续/K28.5/符号时,RX同步,然后将SYNC~引脚拉高。

d、RX必须接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。

e、CGS阶段结束,ILAS阶段开始。

注意:

a、串行数据传输没有接口时钟,因此RX必须将其数位及字边界与TX串行输出对齐。RX向TX发送~SYNC请求信号,让其通过所有信道发送一个已知的重复比特序列K28.5。RX将移动每个信道上的比特数据,直到找到4个连续的K28.5字符为止。此时,它不仅将知道比特及字边界,而且已经实现了CGS。

b、RX~SYNC的输出必须与RX的帧时钟同步,同时要求TX的帧时钟与~SYNC同步(可通过~SYNC复位TX的帧时钟计数器来实现)。

c、不能使用交流耦合。

B、第二阶段,初始通道同步(ILAS):

a、在JESD204B中,发送模块捕捉到SYNC~信号的变换,在下一个本地多帧(LMFC)边界上启动ILAS。

b、ILAS主要对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

c、ILAS由4个多帧组成。每个多帧最后一个字符是多帧对齐字符/A,第一,三,四个多帧以/R字符开始,以/A字符结束。接收器以各通道的最后一个字符/A对齐接收器内各通道内各多帧的末尾。

d、这些特定的控制字符只用于初始通路对齐序列中,而不用在数据传输的任何其他阶段。CGS和ILAS阶段不加扰。

e、RX模块中的FIFO吸收信道偏移。

C、第三阶段,数据传输阶段:

没有控制字符,获取链路全带宽。利用字符替换来监视数据同步,多帧计数器LMFC。

6.Deviceclk

系统基准时钟,提供采样时钟,JESD204B时钟,帧串行器时钟。产生帧时钟和多帧时钟。器件时钟用来捕捉SYSREF,并完成帧和多帧时钟的前沿相位对齐。子类1中,多帧时钟周期必须是器件时钟的整数倍。ADC/DAC/FPGA可运行于不同速率,但必须同源且频率相关。

7、同步对齐过程

发送器和接收器各维护一个多帧计数器(LMFC),所有发送器和接收器连接到一个公共(源)SYSREF,这些器件利用SYSREF复位其LMFC,这样所有LMFC应互相同步(在一个时钟周期内)。

SYSREFsignal(DeviceSubclass1):

a、确定时延(小于1个多帧时钟周期)。

b、对齐和器件时钟同源,LMFC周期的整数倍,在DeviceClk沿变化时采样SYSREF信号,确定时延,对齐多帧和帧时钟。SYSREF用于对齐所有收发器件LMFC相位。

SYNC~signal:

同步请求信号。接收端:与接收器帧时钟同步。CGS后在接收端LMFC边沿拉高。释放SYNC(所有器件都会看到)后,发送器在下一次(TX)LMFC绕回0时开始ILAS。如果F*K设置适当,大于(发送器编码时间)+(线路传播时间)+(接收器解码时间),则接收数据将在下一个LMFC之前从接收器的SERDES传播出去。接收器将把数据送入FIFO,然后在下一个(RX)LMFC边界开始输出数据。发送器SERDES输入与接收器FIFO输出之间的已知关系称为确定性延迟。

三,JESD204B具体应用实例

1、相控阵雷达下行同步采集技术应用

多通道数据的同步采集是数字相控阵雷达下行数据接收和处理要解决的关键问题。提出了支持JESD204B协议的模数转换器和支持JESD204B协议的FPGA软核相结合的设计方案。利用JESD204B协议的确定性延迟特性,只要保证通道间下行数据的相互延迟不超过一个多帧时钟周期,通过关键控制信号的设计和处理,通道间可以实现数据的同步,有效控制板内多片ADC之间进行同步采样,从而解决数字相控阵雷达下行数据因采集带来的相位一致性问题。

2、雷达多通道同步采集实现

该设计是一种软硬件结合的简化方案,通过合理设计硬件、设计SYSREF信号的扇出控制逻辑,在一定采样率范围内满足JESD204B协议ADC多片多通道之间采样点相对时延固定,从而确保各通道采集信号相位一致。JESD204B协议支持的确定性延迟特性保证了设计实现。验证方案的测试电路采用Xilinx K7系列FPGA控制两片AD9694(采样率320Msps)同步采集,证实设计方案满足应用需求。

3、雷达视频信号同步传输设计与实现

以宽带测向接收机中多波束比幅测向为背景,设计了基于JESD204B协议的高速背板视频信号同步传输方案。时钟、JESD204B协议参数的设计合理,实现了2块多通道视频幅度采集板与1块数据处理板之间线速率为6.25Gbps的高速同步传输,解决了多波束比幅测向前多通道视频信号传输同步问题。

4、高速ADC应用与研究

在成像设备、通信、雷达、工业仪器仪表等需要实时传输大量数据的行业中,要求其数模转换器的采样率越来越高、数据位越来越大、带宽越来越宽、传输速率越来越快。这对高速数据采集传输系统提出了更高的要求。传统的ADC大多使用并行总线进行数据传输,随着采样率的提高,捕获数据量的激增,并行总线的吞吐率需大大提升,这就要增加输出数据线的位数,而位数的增加需要占用大量的芯片管脚,使芯片和PCB的小型化难以实现并且在大量高速数据信号走线的同时控制电压噪声也是难以做到的。

与传统的并行总线传输ADC相比,使用高速串行总线传输的ADC具有非常明显的优势,其中所需的信号传输线大大减少,总线传输速率也明显提升,并且在提高数据传输速率的同时节省了布线空间,同时也降低了芯片功耗。使用高速串行总线传输的ADC不仅在体积、功耗和数据传输速率都比并行总线传输的ADC更具优势。在高速数据采集传输系统中,串行总线传输的ADC已成为今后的发展趋势。在研究了高速串行传输技术后,设计了基于JESD204B协议的串行总线技术的ADC,并设计了基于此协议的高速ADC采样电路,该模数转换芯片支持JESD204BSubclass1工作模式,通过FMC接口与高性能FPGA的GTH接口相连接收ADC采样后的数据,最终通过PCIE金手指与PC端进行传输。

5、JESD204B协议中自同步加解扰电路设计与实现

作为JEDEC最新修订的AD/DA串行传输协议,JESD204B采用自同步扰码对数据链路层原始信号进行随机化转换,有效地避免了杂散频谱产生,减少了物理层误码概率.基于经典状态机结构对JESD204B协议中自同步加扰及解扰电路进行设计实现,根据协议中自同步扰码的原理细节,提出了一种加扰与解扰状态电路的设计方案,最终对该方案进行实现、仿真与综合.仿真与综合结果表明该方案充分兼容协议控制信号,功能完全符合协议要求,增强了加解扰电路的稳定性与容错性,同时提高了电路的处理效率,可应用于JESD204B高速串行接口电路设计中。

以上就是关于JESD204B的应用场景的介绍,明德扬可承接基于JESD204B的高速数据传输项目,若想了解更多,可联系。

边栏推荐

- 【OpenCV】形态学滤波(2):开运算、形态学梯度、顶帽、黑帽

- UIC(组态UI工程)公版文件库新增7款行业素材

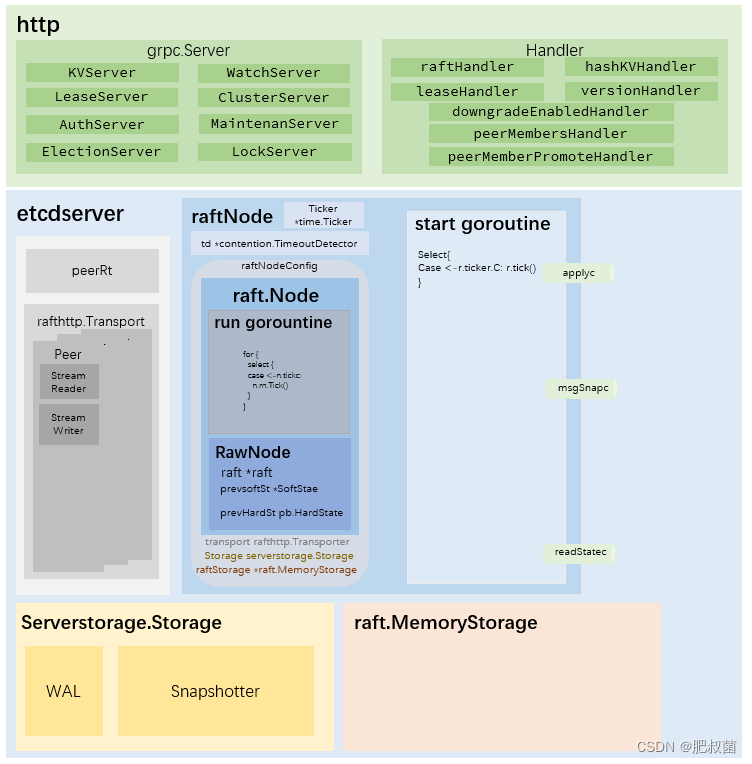

- Etcd database source code analysis -- starting from the start function of raftnode

- Can't you really do it when you are 35 years old?

- c语言(结构体)定义一个User结构体,含以下字段:

- Array proof during st table preprocessing

- docker-compose启动redis集群

- 骑士战胜魔王(背包&dp)

- 基本Dos命令

- Abnova 体外转录 mRNA工作流程和加帽方法介绍

猜你喜欢

What are the classic database questions in the interview?

Tkinter window selects PCD file and displays point cloud (open3d)

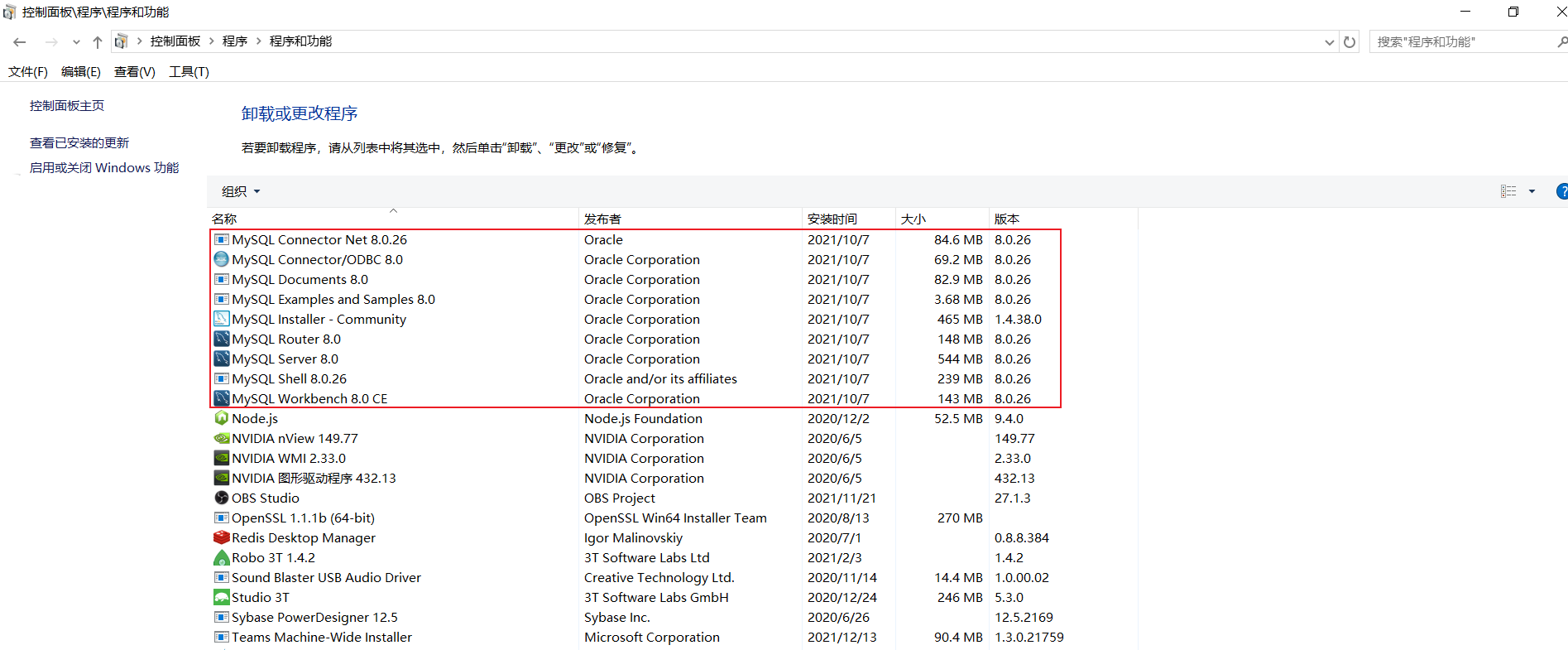

MySQL卸载文档-Windows版

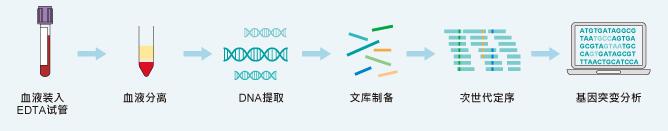

Abnova循环肿瘤DNA丨全血分离,基因组DNA萃取分析

POI export to excel: set font, color, row height adaptation, column width adaptation, lock cells, merge cells

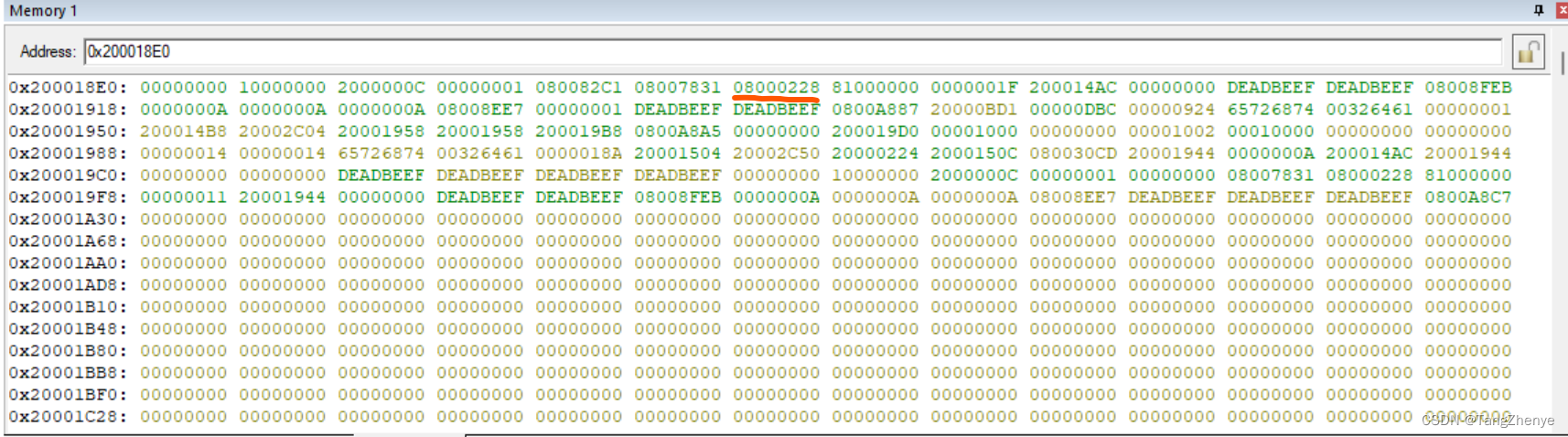

rt-thread 中对 hardfault 的处理

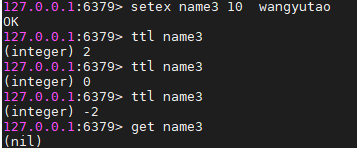

Redis (II) - redis General Command

ETCD数据库源码分析——从raftNode的start函数说起

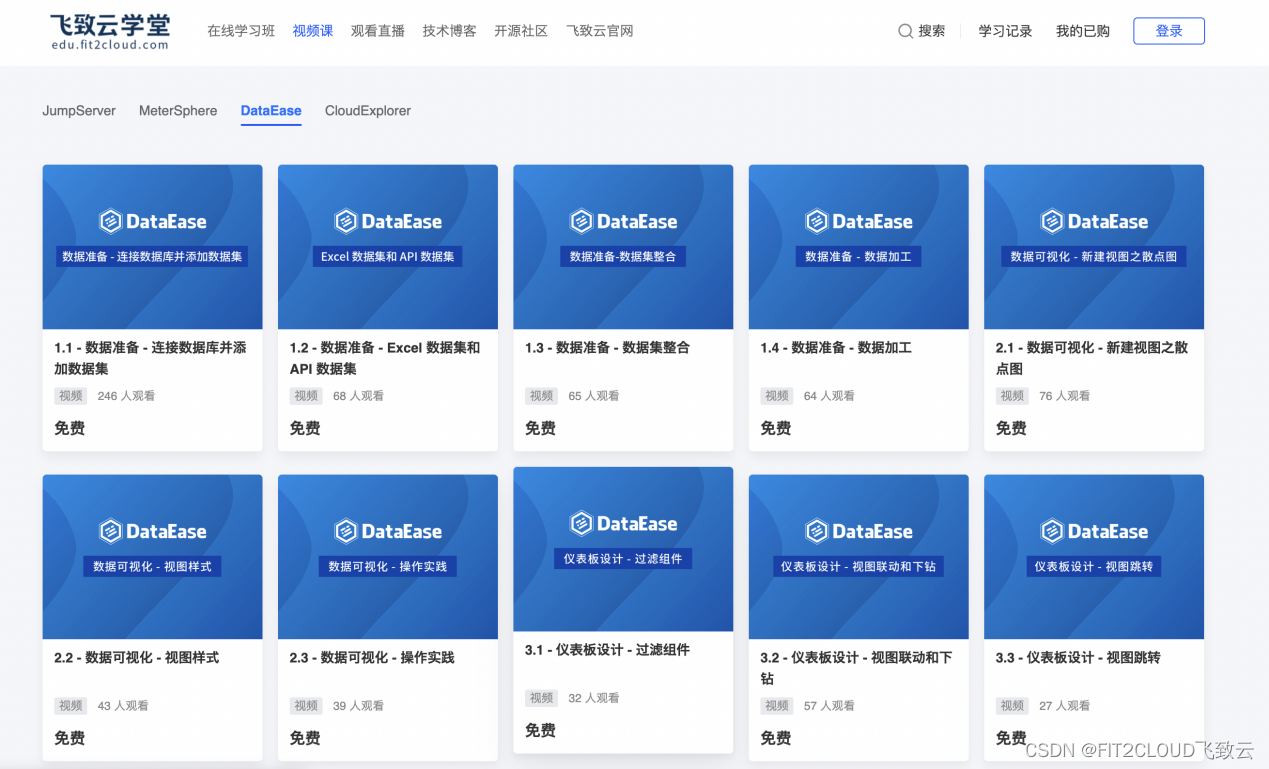

学习笔记|数据小白使用DataEase制作数据大屏

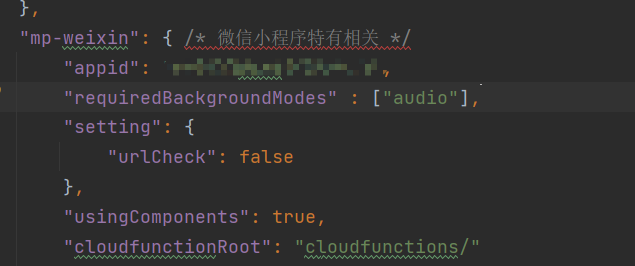

How to use wechat cloud hosting or cloud functions for cloud development of unapp development applet

随机推荐

快速定量,Abbkine 蛋白质定量试剂盒BCA法来了!

The difference between string constants and string objects when allocating memory

Postgresql源码(59)分析事务ID分配、溢出判断方法

3531. Huffman tree

对称的二叉树【树的遍历】

dolphinscheduler3.x本地启动

Ha Qu projection dark horse posture, only half a year to break through the 1000 yuan projector market!

You don't know the complete collection of recruitment slang of Internet companies

谷歌 Chrome 浏览器发布 103.0.5060.114 补丁修复 0-day 漏洞

Google Chrome browser released patch 103.0.5060.114 to fix the 0-day vulnerability

项目实战 五 拟合直线 获得中线

Abnova 体外转录 mRNA工作流程和加帽方法介绍

MySQL installation

学习笔记|数据小白使用DataEase制作数据大屏

Party A's requirements for those who have lost 800 yuan

「解析」FocalLoss 解决数据不平衡问题

C语言整理(待更新)

[SOC FPGA] peripheral PIO button lights up

C language interview to write a function to find the first public string in two strings

LM11丨重构K线构建择时交易策略