当前位置:网站首页>[Digital IC manual tearing code] Verilog asynchronous reset synchronous release | topic | principle | design | simulation

[Digital IC manual tearing code] Verilog asynchronous reset synchronous release | topic | principle | design | simulation

2022-07-06 02:29:00 【myhhhhhhhh】

Preface

This series aims to provide 100% Accurate numbers IC Design / Verify the title of the hand tearing code link , principle ,RTL Design ,Testbench And reference simulation waveform , The content of each article is checked by simulation . The quick navigation links are as follows :

Odd frequency division

Even frequency division

Semi integer batch

decimal / Fractional frequency division

Sequence detector

Mode three detector

Beverage machine

Asynchronous reset , Simultaneous release

Edge detection ( Rising edge , Falling edge , On both sides )

Full adder , Half adder

Gray code to binary

single bit Cross clock domain ( Two beats , Edge synchronization , Pulse synchronization )

Sync FIFO

Ought to say , The hand tearing code link is in the interview process Both important and simple A part of , Compared with software jobs , Numbers IC Hand tear code Fixed topic , Limited number , It belongs to a link that must be scored in the whole interview , Outside this series , I also recommend numbers IC Job seekers use “HdlBits” Code Training

Links are as follows

HDLBits — Verilog Practice

Asynchronous reset synchronous release problem

Use Verilog Code , Complete the design of asynchronous reset and synchronous release circuit

The principle of asynchronous reset and synchronous release

One with asynchronous reset end DFF workflow

If one DFF The reset value of is 0, that rst_n=0 When the signal comes , The DFF Reset , When rst_n=1 When the signal comes , The DFF Normal work .

Possible problems

When rst_n The signal returns 1 Time and clk When the signal coming from the rising edge is very close ,DFF Metastable state may be output , The reason why the signal cannot be recognized is 1 still 0

terms of settlement

Asynchronous reset : Yes 0 The reset signal of is not processed , Let it reset normally asynchronously

Simultaneous release : Yes 1 Make two beats of the reset signal , Align the edge of the clock when it is pulled up , In order to avoid metastable state

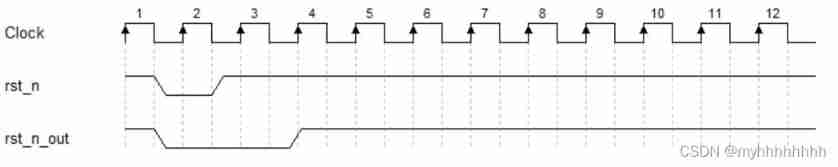

Sequence diagram of asynchronous reset and synchronous release

RTL Design

module rst_asy(clk,rst_n,rst_out);

input clk;

input rst_n;

output reg rst_out;

reg rst_r1;

[email protected](posedge clk or negedge rst_n)

if(!rst_n)

begin

rst_out<= 1'b0;

rst_r1 <= 1'b0;

end

else

begin

rst_r1 <= rst_n;

rst_out <= rst_r1;

end

endmodule

Testbench Code

`timescale 1ns /1ps

module rst_asy_tb();

reg clk ;

reg rst_n;

wire rst_out;

rst_asy u1(.clk(clk),.rst_n(rst_n),.rst_out(rst_out));

always #5 clk = !clk;

initial

begin

clk = 0;

rst_n = 1;

#7

rst_n = 0;

#5

rst_n = 1;

#30

$stop;

end

endmodule

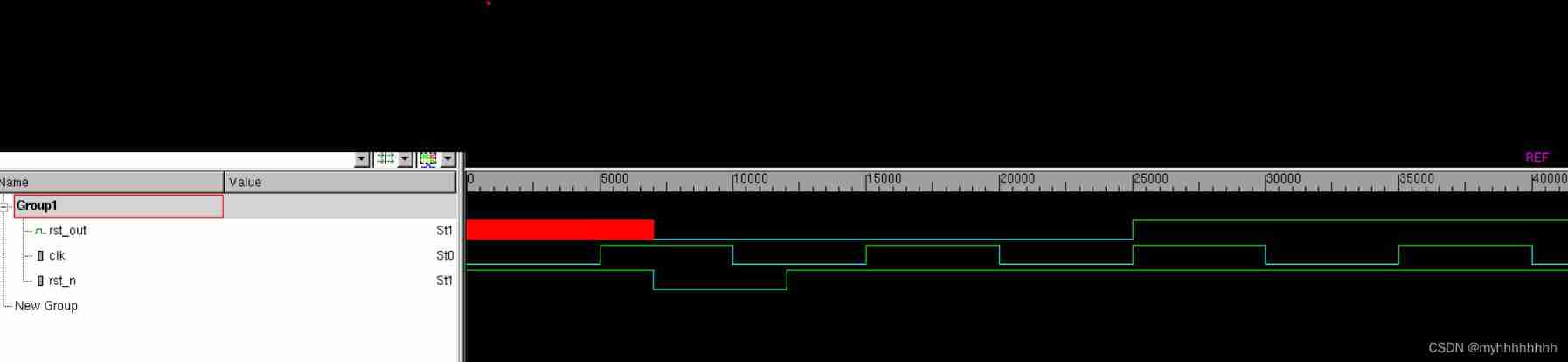

Simulation analysis

rst_n After re raising ,rst_out Wait for the register to save twice before output , Metastable state is avoided , Design establishment

边栏推荐

- LeetCode 103. Binary tree zigzag level order transverse - Binary Tree Series Question 5

- Template_ Find the reverse pair of permutations_ Sort based on merge

- Concept of storage engine

- [coppeliasim] efficient conveyor belt

- RDD conversion operator of spark

- [coppeliasim] 6-DOF path planning

- sql表名作为参数传递

- MySQL index

- Looking at the trend of sequence modeling of recommended systems in 2022 from the top paper

- Data preparation

猜你喜欢

Lecture 4 of Data Engineering Series: sample engineering of data centric AI

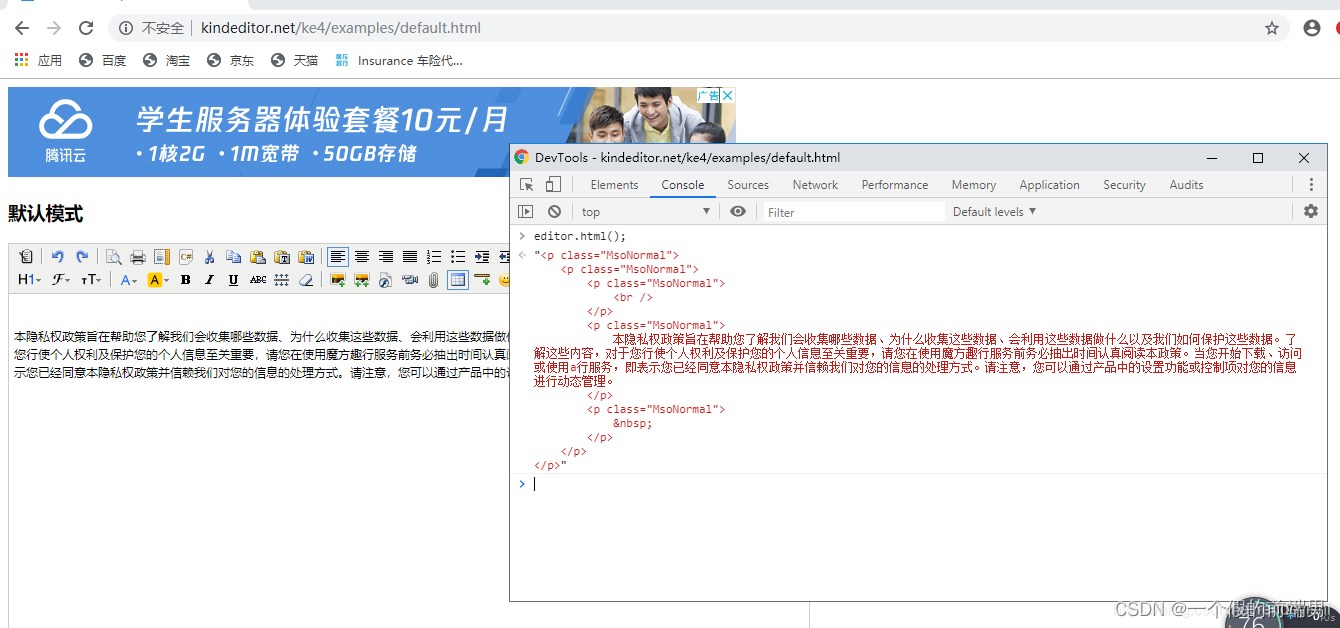

在线怎么生成富文本

【社区人物志】专访马龙伟:轮子不好用,那就自己造!

The ECU of 21 Audi q5l 45tfsi brushes is upgraded to master special adjustment, and the horsepower is safely and stably increased to 305 horsepower

PAT甲级 1033 To Fill or Not to Fill

A basic lintcode MySQL database problem

![[community personas] exclusive interview with Ma Longwei: the wheel is not easy to use, so make it yourself!](/img/aa/af98b588efd61d71b1b02609817c49.png)

[community personas] exclusive interview with Ma Longwei: the wheel is not easy to use, so make it yourself!

![[postgraduate entrance examination English] prepare for 2023, learn list5 words](/img/6d/47b853e76d1757fb6e42c2ebba38af.jpg)

[postgraduate entrance examination English] prepare for 2023, learn list5 words

Computer graduation design PHP part-time recruitment management system for College Students

Easy to use js script

随机推荐

ftp上传文件时出现 550 Permission denied,不是用户权限问题

Minecraft 1.16.5 biochemical 8 module version 2.0 storybook + more guns

The ECU of 21 Audi q5l 45tfsi brushes is upgraded to master special adjustment, and the horsepower is safely and stably increased to 305 horsepower

Keyword static

Concept of storage engine

一题多解,ASP.NET Core应用启动初始化的N种方案[上篇]

The ECU of 21 Audi q5l 45tfsi brushes is upgraded to master special adjustment, and the horsepower is safely and stably increased to 305 horsepower

构建库函数的雏形——参照野火的手册

Visualstudio2019 compilation configuration lastools-v2.0.0 under win10 system

Apicloud openframe realizes the transfer and return of parameters to the previous page - basic improvement

Adapter-a technology of adaptive pre training continuous learning

[Clickhouse] Clickhouse based massive data interactive OLAP analysis scenario practice

Use the list component to realize the drop-down list and address list

Template_ Quick sort_ Double pointer

SQL statement

Dachang image library

Ue4- how to make a simple TPS role (II) - realize the basic movement of the role

Have a look at this generation

Httprunnermanager installation (III) - configuring myql Database & initialization data under Linux

Building the prototype of library functions -- refer to the manual of wildfire