当前位置:网站首页>How to become a senior digital IC Design Engineer (1-6) Verilog coding Grammar: Classic Digital IC Design

How to become a senior digital IC Design Engineer (1-6) Verilog coding Grammar: Classic Digital IC Design

2022-07-07 09:36:00 【New core design】

-- adder (Adder): Consider carry overflow

assign o_sum[DATA_WIDTH:0] = i_parta[DATA_WIDTH-1:0] + i_partb[DATA_WIDTH-1:0];

-- Half adder (Half-Adder)(DATA_WIDTH == 1): No carry input (DATA_WIDTH == 1)

assign {o_carry, o_sum[DATA_WIDTH-1:0]} = i_parta[DATA_WIDTH-1:0] + i_partb[DATA_WIDTH-1:0];

-- Full adder (Full-Adder)(DATA_WIDTH == 1): There is a carry input (DATA_WIDTH == 1)

assign {o_carry, o_sum[DATA_WIDTH-1:0]} = i_parta[DATA_WIDTH-1:0] + i_partb[DATA_WIDTH-1:0] + i_carry;

The comparator (Comparator)

assign equal = (compa == compb) ? 1'b1 : 1'b0;

assign bigger = (compa >= compb) ? 1'b1 : 1'b0;

assign smaller = (compa <= compb) ? 1'b1 : 1'b0;

Selectors (Selector)(Arbiter)(Multiplexor)(MUX)

// Three implementation methods are simply given :

// The way 1:

assign result = sel ? dina : dinb;

// The way 2:

assign result = ({(DATA_WIDTH){sel}} & dina[D

边栏推荐

- 数据建模中利用3σ剔除异常值进行数据清洗

- Oracle installation enhancements error

- 章鱼未来之星获得25万美金奖励|章鱼加速器2022夏季创业营圆满落幕

- Unity shader (data type in cghlsl)

- golang select机制和超时问题怎么解决

- Colorbar of using vertexehelper to customize controls (II)

- 华为HCIP-DATACOM-Core_03day

- [4G/5G/6G专题基础-147]: 6G总体愿景与潜在关键技术白皮书解读-2-6G发展的宏观驱动力

- Network request process

- Postman data driven

猜你喜欢

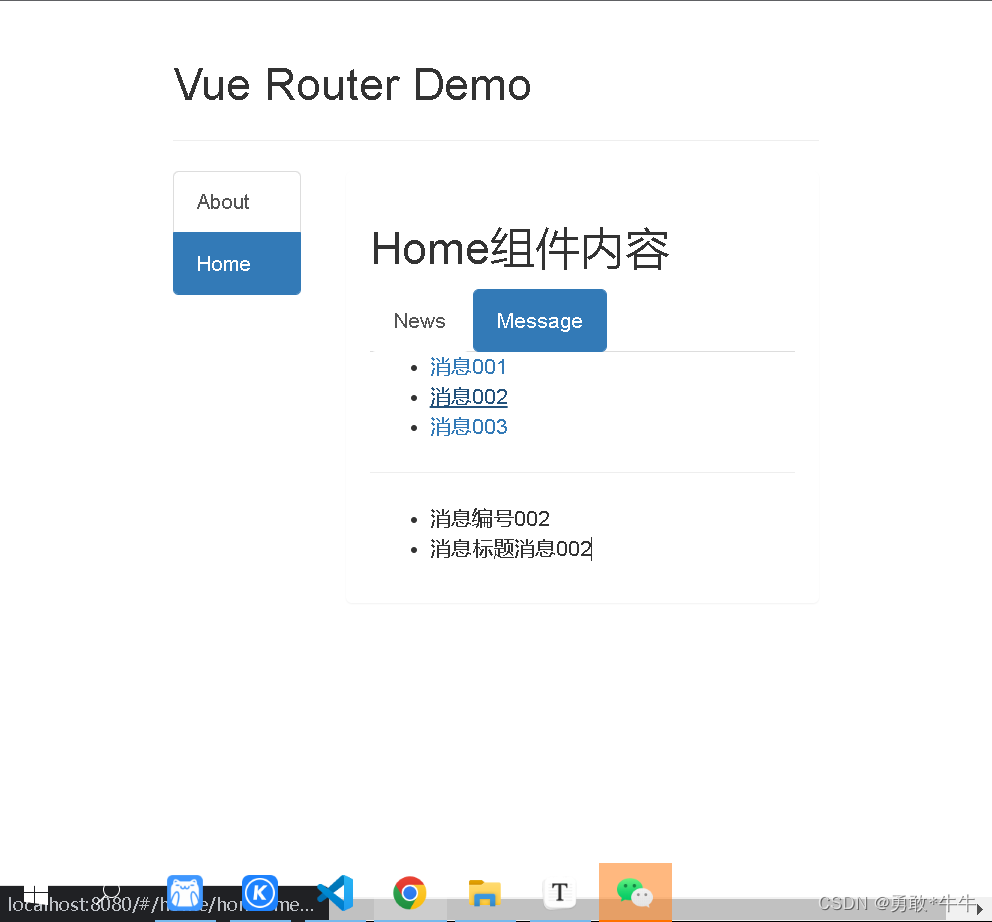

嵌套(多级)childrn路由,query参数,命名路由,replace属性,路由的props配置,路由的params参数

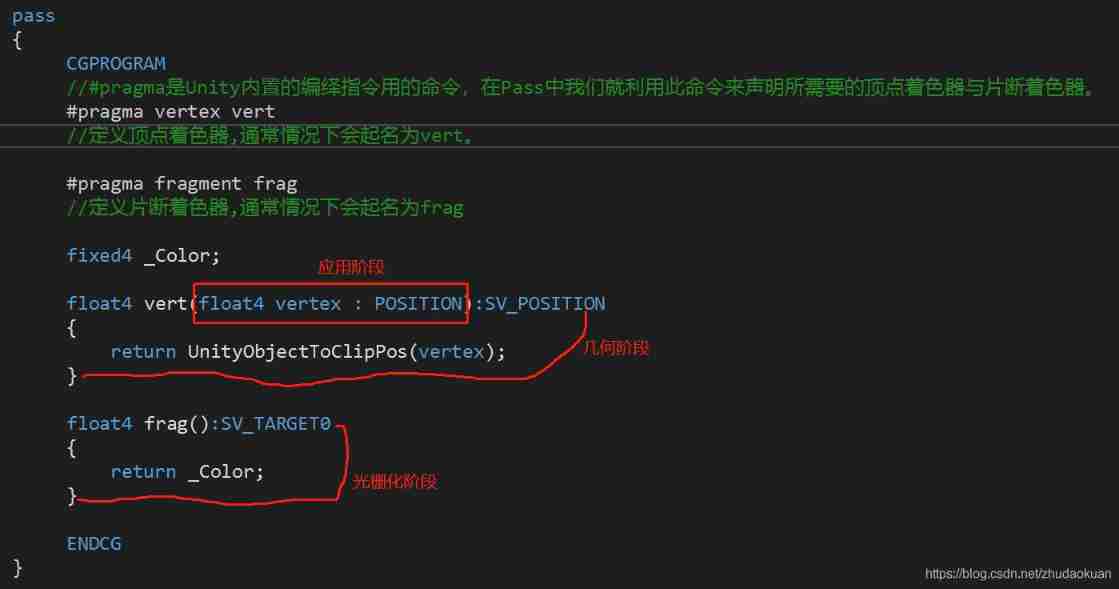

Unity shader (learn more about vertex fragment shaders)

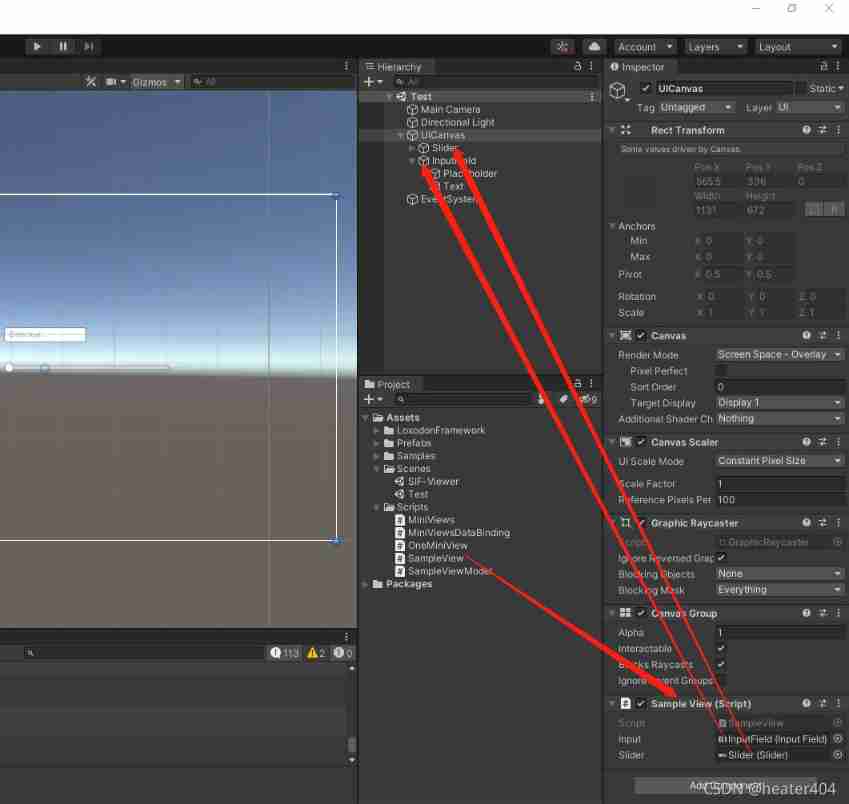

Loxodonframework quick start

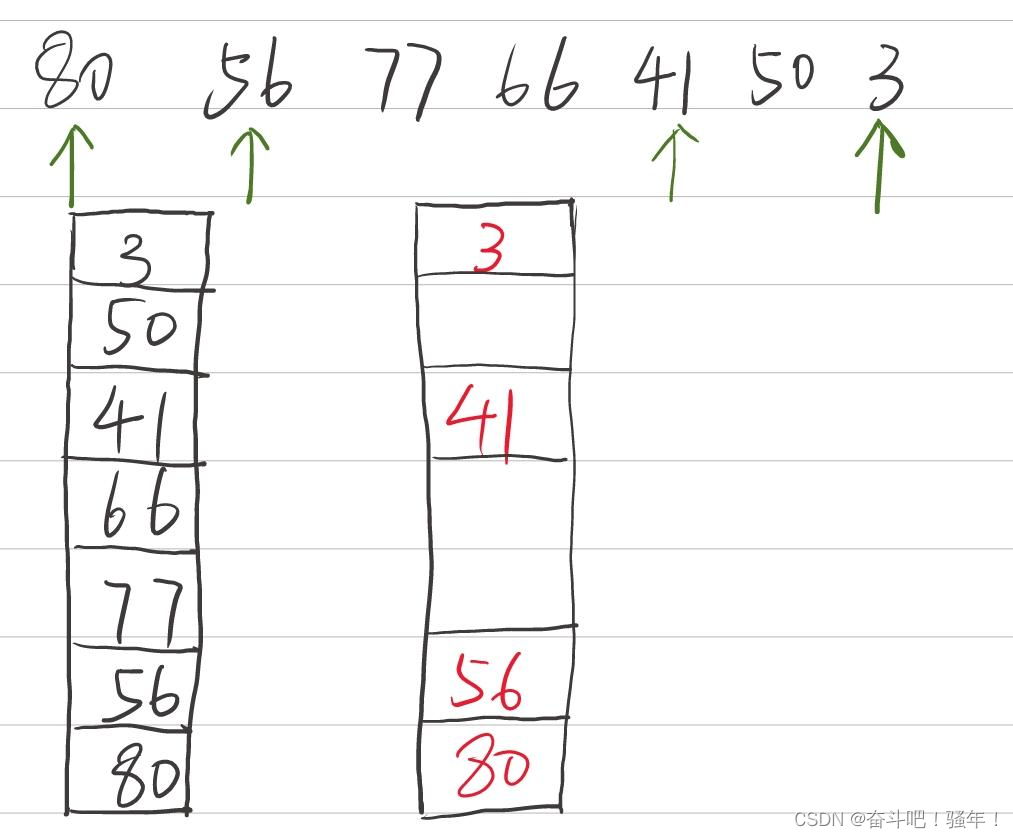

Lecture 1: stack containing min function

![[4G/5G/6G专题基础-146]: 6G总体愿景与潜在关键技术白皮书解读-1-总体愿景](/img/fd/5e8f74da25d9c5f7bd69dd1cfdcd61.png)

[4G/5G/6G专题基础-146]: 6G总体愿景与潜在关键技术白皮书解读-1-总体愿景

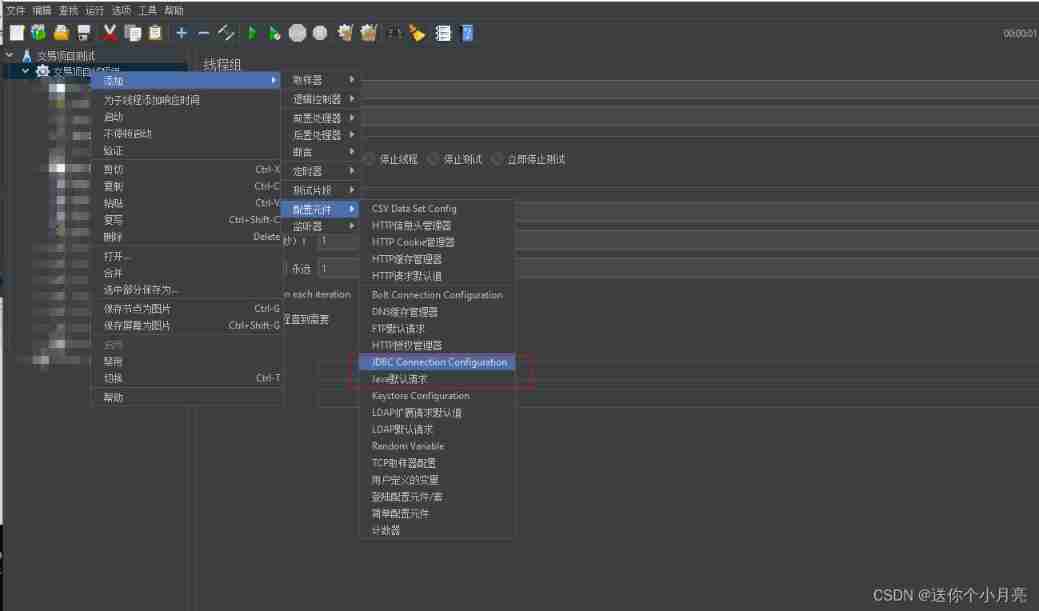

JMeter JDBC batch references data as input parameters (the simplest method for the whole website)

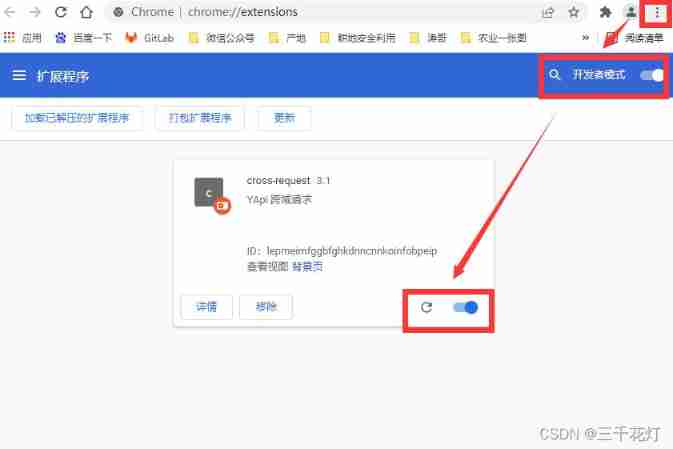

Yapi test plug-in -- cross request

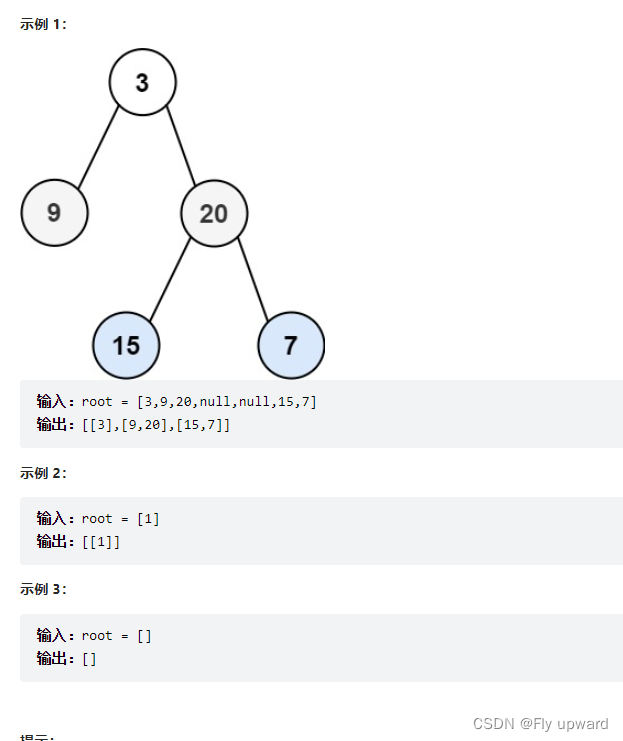

Binary tree high frequency question type

iNFTnews | 时尚品牌将以什么方式进入元宇宙?

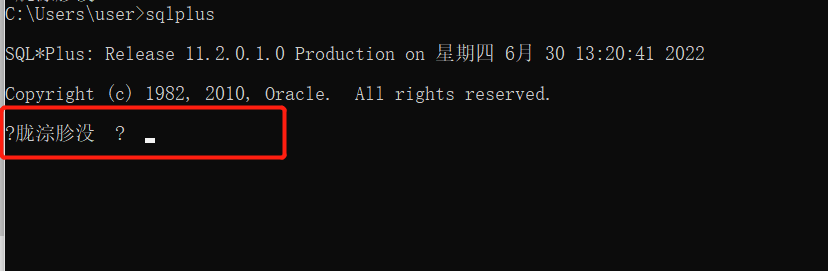

sqlplus乱码问题,求解答

随机推荐

Impression notes finally support the default markdown preview mode

Mysql database lock learning notes

Add new item after the outbound delivery order of SAP mm sto document is created?

MongoDB怎么实现创建删除数据库、创建删除表、数据增删改查

Information Security Experiment 3: the use of PGP email encryption software

Unity shader (pass user data to shader)

细说Mysql MVCC多版本控制

Error: selenium common. exceptions. WebDriverException: Messag‘geckodriver‘ execute

Diffusion模型详解

What development models did you know during the interview? Just read this one

第一讲:鸡蛋的硬度

Difference between interface iterator and iteratable

Unity shader (learn more about vertex fragment shaders)

Lesson 1: hardness of eggs

華為HCIP-DATACOM-Core_03day

DRF defines views and routes

Dynamics 365Online ApplicationUser创建方式变更

Redis common commands

信息安全实验一:DES加密算法的实现

如何成为一名高级数字 IC 设计工程师(5-3)理论篇:ULP 低功耗设计技术精讲(下)