当前位置:网站首页>Weidongshan Internet of things learning lesson 1

Weidongshan Internet of things learning lesson 1

2022-07-05 08:12:00 【qq_ forty-one million seven hundred and forty-four thousand fou】

I reviewed it again today STM32 Internet of things programming for . Mainly review the past STM32 Clock settings for , And put notes :

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0}; // hold RCC_OscInitStruct The variable is cleared .

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0}; // hold RCC_ClkInitStruct The variable is cleared .

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI; // Clock type

/*

#define RCC_OSCILLATORTYPE_NONE 0x00000000U // No clock

#define RCC_OSCILLATORTYPE_HSE 0x00000001U // Use the external oscillator crystal oscillator as the clock

#define RCC_OSCILLATORTYPE_HSI 0x00000002U // Use internal high-speed clock , The clock frequency is 8MHz

#define RCC_OSCILLATORTYPE_LSE 0x00000004U // Use an external low-speed clock , The clock frequency is 32.768kHZ

#define RCC_OSCILLATORTYPE_LSI 0x00000008U // Internal low-power sleep clock , The frequency is 30~60Hz

*/

RCC_OscInitStruct.HSEState = RCC_HSE_OFF; // Turn off the clock when the external crystal oscillator is not used , Open it when you need it .

RCC_OscInitStruct.HSEPredivValue = RCC_HSE_PREDIV_DIV1;

/* One function is to empty HSE frequency division , initialization HSE frequency division ; You can also rewrite RCC_HSE_PREDIV_DIV1,

Rewrite directly RCC_CFGR Register value , But it's useless. Later, it will be changed back by the later code , So it usually doesn't move here .*/

RCC_OscInitStruct.HSIState = RCC_HSI_ON; // If you use an internal clock , Just turn it on , Close it before you use it .

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; // Turn on the PLL , Close the PLL without frequency division

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI_DIV2;

/*

If it is RCC_PLLSOURCE_HSI_DIV2, The PLL uses the internal clock as the benchmark , Frequency is 8MHZ After dichotomy, it becomes 4MHz.

If it is RCC_PLLSOURCE_HSE, The PLL uses the external clock as the reference , The frequency is the external clock frequency

*/

RCC_OscInitStruct.PLL.PLLMUL = RCC_PLL_MUL16;

/*

#define RCC_PLL_MUL2 RCC_CFGR_PLLMULL2

#define RCC_PLL_MUL3 RCC_CFGR_PLLMULL3

#define RCC_PLL_MUL4 RCC_CFGR_PLLMULL4

#define RCC_PLL_MUL5 RCC_CFGR_PLLMULL5

#define RCC_PLL_MUL6 RCC_CFGR_PLLMULL6

#define RCC_PLL_MUL7 RCC_CFGR_PLLMULL7

#define RCC_PLL_MUL8 RCC_CFGR_PLLMULL8

#define RCC_PLL_MUL9 RCC_CFGR_PLLMULL9

#define RCC_PLL_MUL10 RCC_CFGR_PLLMULL10

#define RCC_PLL_MUL11 RCC_CFGR_PLLMULL11

#define RCC_PLL_MUL12 RCC_CFGR_PLLMULL12

#define RCC_PLL_MUL13 RCC_CFGR_PLLMULL13

#define RCC_PLL_MUL14 RCC_CFGR_PLLMULL14

#define RCC_PLL_MUL15 RCC_CFGR_PLLMULL15

#define RCC_PLL_MUL16 RCC_CFGR_PLLMULL16

From 2 To 16 There are these frequencies to choose

*/

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK) // Perform initialization of clock frequency configuration , Maximum output of external crystal oscillator clock after frequency doubling 72M

{

while(1);

}

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK

| RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2;

/*

RCC_CLOCKTYPE_SYSCLK Select this to configure the system clock HSE,HSI, still PLL,

RCC_CLOCKTYPE_HCLK Select this to configure AHB The clock ,

RCC_CLOCKTYPE_PCLK1 Select this to configure APB1 The clock of ,

RCC_CLOCKTYPE_PCLK2 Select this to configure APB2 The clock of .

*/

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

/*

#define RCC_SYSCLKSOURCE_HSI RCC_CFGR_SW_HSI !< Select the internal high-speed clock as the system clock

#define RCC_SYSCLKSOURCE_HSE RCC_CFGR_SW_HSE !< Select the external crystal oscillator clock as the system clock

#define RCC_SYSCLKSOURCE_PLLCLK RCC_CFGR_SW_PLL !< Choose PLL clock as the system clock

*/

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; //AHB Clock division is divided by 1~512 One of the values

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; //APB1 The clock frequency division , First get from the system clock frequency division AHB The clock , Again from AHB The clock is divided according to this option APB1 The frequency of , The final calculation shall not exceed 36MHz

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1; //APB2 The clock frequency division , First get from the system clock frequency division AHB The clock , Again from AHB The clock is divided according to this option APB2 The frequency of , The final calculation shall not exceed 72MHz

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK) // Execute the configuration of the system clock and the clock of the system clock frequency division to the following components .

{

while(1);

}

}

边栏推荐

- Shape template matching based on Halcon learning [v] find_ cocoa_ packages_ max_ deformation. Hdev routine

- [trio basic from introduction to mastery tutorial XIV] trio realizes unit axis multi-color code capture

- Define in and define out

- Why is 1900 not a leap year

- Improve lighting C program

- Basic embedded concepts

- Mlperf training v2.0 list released, with the same GPU configuration, the performance of Baidu PaddlePaddle ranks first in the world

- IEEE access personal contribution experience record

- The research found that the cross-border e-commerce customer service system has these five functions!

- C language # and #

猜你喜欢

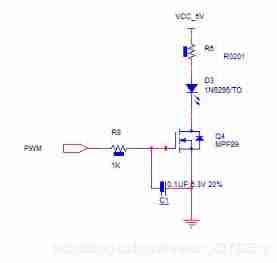

On boost circuit

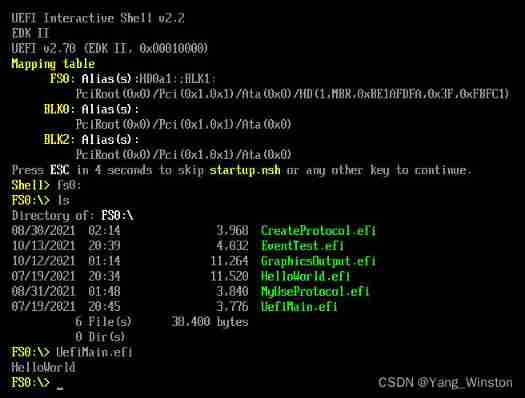

UEFI development learning 3 - create UEFI program

Basic embedded concepts

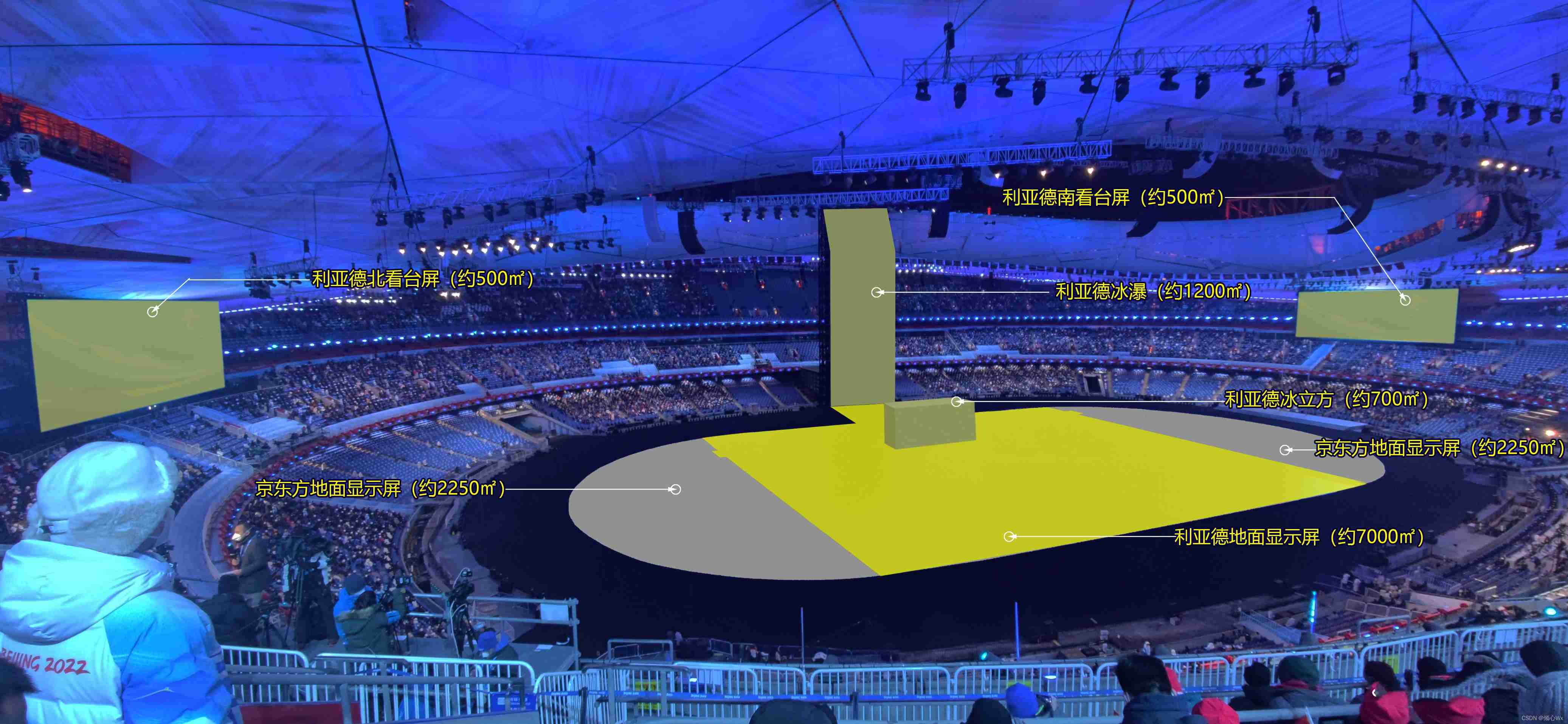

Screen record of the opening ceremony of the Beijing winter olympics 2

Classic application of MOS transistor circuit design (2) - switch circuit design

Tailq of linked list

![Shape template matching based on Halcon learning [viii] PM_ multiple_ models. Hdev routine](/img/13/22a1915329f58acd54c40176f6f301.jpg)

Shape template matching based on Halcon learning [viii] PM_ multiple_ models. Hdev routine

Can't find real-time chat software? Recommend to you what e-commerce enterprises are using!

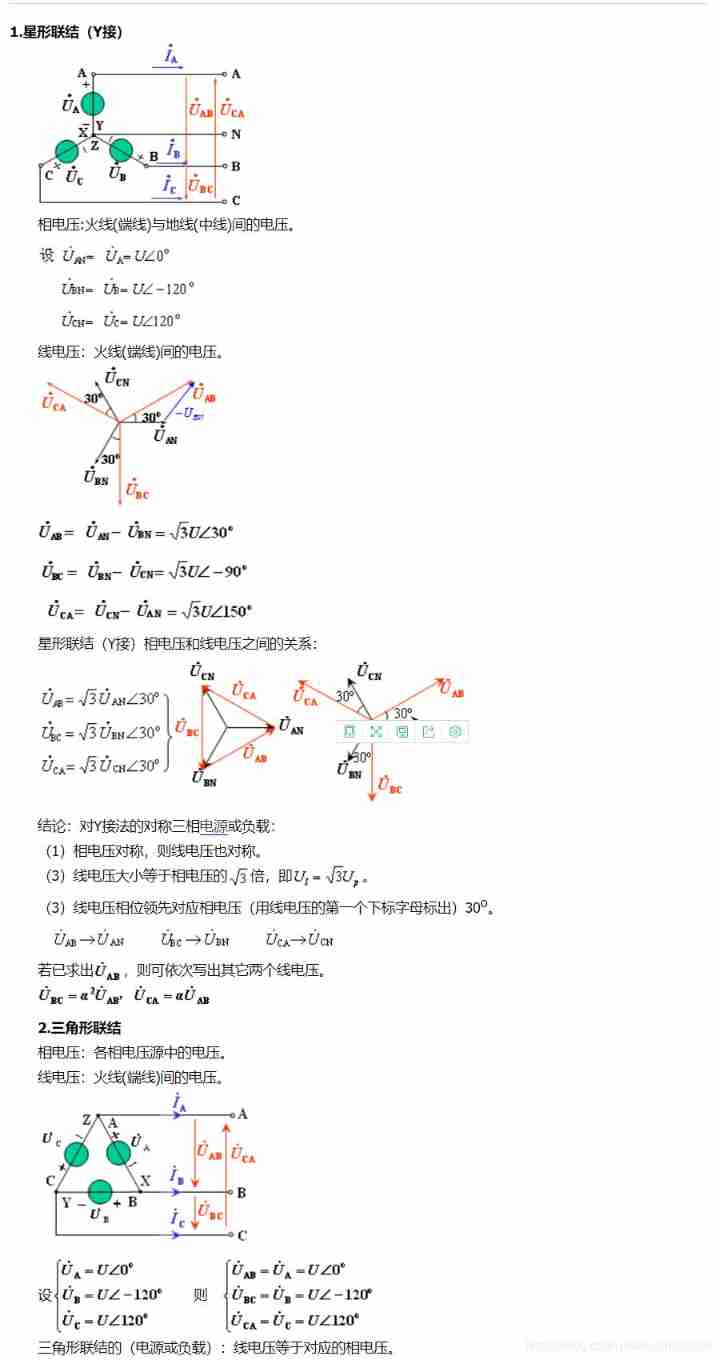

Relationship between line voltage and phase voltage, line current and phase current

![Halcon's practice based on shape template matching [1]](/img/68/206eed7502fbf108a929aa9365b1ae.jpg)

Halcon's practice based on shape template matching [1]

随机推荐

My-basic application 2: my-basic installation and operation

[tutorial 19 of trio basic from introduction to proficiency] detailed introduction of trio as a slave station connecting to the third-party bus (anybus PROFIBUS DP...)

Extern keyword function

LED display equipment records of the opening ceremony of the Beijing Winter Olympics

Basic embedded concepts

[paper reading] the latest transfer ability in deep learning: a survey in 2022

Process communication mode between different hosts -- socket

Drive LED -- GPIO control

Communication standard -- communication protocol

Hardware 1 -- relationship between gain and magnification

Class of color image processing based on Halcon learning_ ndim_ norm. hdev

Brief discussion on Buck buck circuit

[trio basic tutorial 18 from introduction to proficiency] trio motion controller UDP fast exchange data communication

Zero length array in GNU C

[trio basic tutorial 16 from introduction to proficiency] UDP communication test supplement

What are the test items of power battery ul2580

Matlab2018b problem solving when installing embedded coder support package for stmicroelectronic

导电滑环磨损快的原因

Sql Server的存儲過程詳解

Naming rules for FreeRTOS