当前位置:网站首页>PCI-Express接口的PCB布线规则

PCI-Express接口的PCB布线规则

2022-07-07 21:51:00 【ltqshs】

1.阻抗要求

PCI-Express的接口走线阻抗在4层或6层板时必须保持100差分(±20% MAX)/60单端(±15%)。

2.线宽和线距

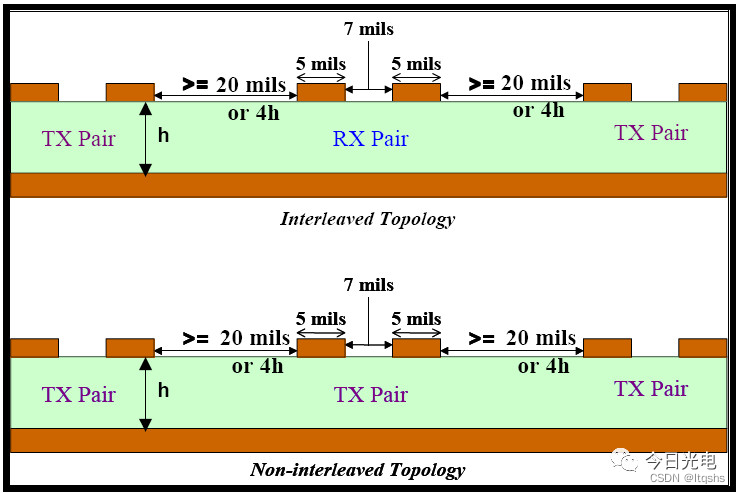

通过阻抗计算软件,结合PCB叠层情况,计算出合理的走线线宽和线距。比如,微带线情况下,差分线的宽度为5mil,差分对中2条走线的间距是7mil。(带状线情况下,差分线的宽度为5mil,差分对中2条走线的间距是5mil。)

差分对之间的距离和差分线与其他非PCI Express信号的距离保持20mil或介质厚度的四倍,选择其中更大者。如果非PCI Express信号电压明显高于或非PCI EXPRESS信号边缘比PCI Express信号边缘快的话,两者的空间应增加到30mil,以避免耦合。如图1所示:

图1

3.长度和长度匹配

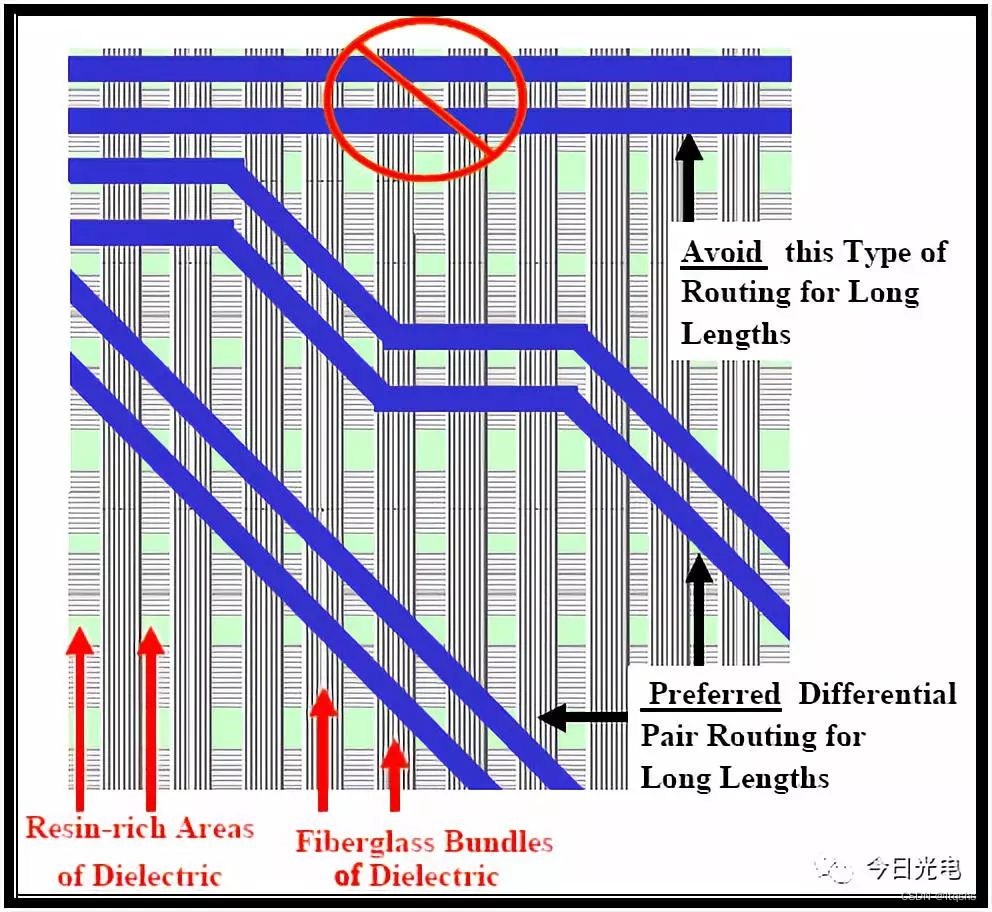

为了分散玻璃纤维束编织和介质层非增强表面树脂层的有效厚度区域的影响,长距离走线必须与XY轴成一个斜的角度(长走线应在板上走斜线),如图2所示:

图2

PCB的每英寸走线可能会引进1ps5ps的抖动预算和0.25dB0.35dB的损耗。介质为FR4的PCB,一般来说:

a.差分对从芯片到芯片的走线最大不能超过6英寸;

b.差分对中两条走线的长度的差距应小于等于5mil。

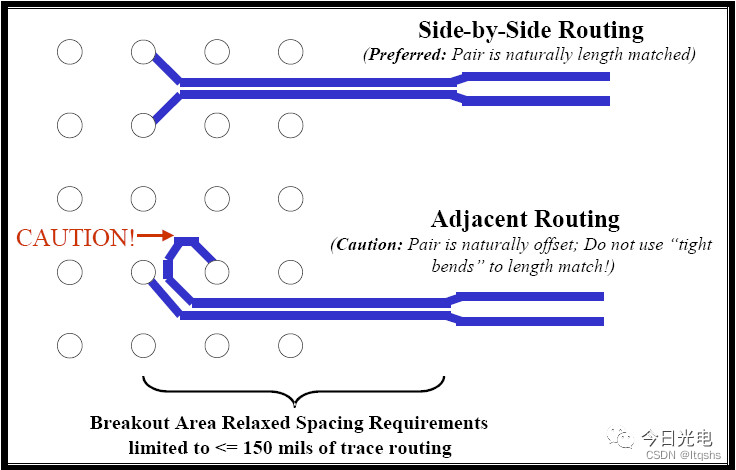

在遇到布局紧张等特殊情况时时走线可以由5-7变为更小的线宽和线距,但是当发生这种情况时,变换的差分对走线长度不能超过150mil。如图3所示:

图3

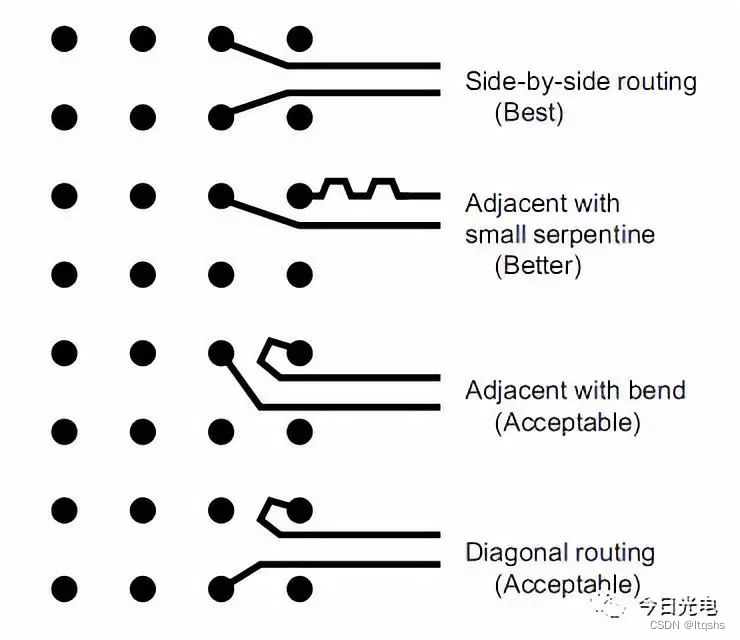

还有长度匹配应尽可能接近信号引脚而没有引入任何小角度弯曲。具体走线可参考图4:

图4

4.测试点、过孔和焊盘

信号过孔影响整体的损耗和抖动预算,限制最大的走线长度。

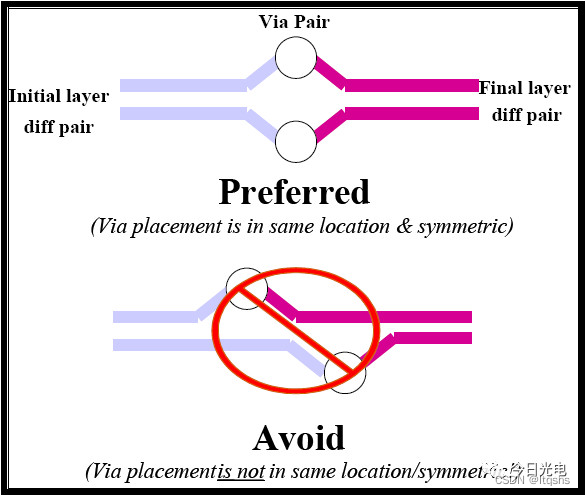

在TX差分对中最多可以使用4个过孔,而在RX差分对中最多只可以使用2个过孔。过孔应该有一个25mil或更小的焊盘,并且其完成内径应该为14mil或更小。两个过孔必须放在一互相对称的位置上。如图5所示:

图5

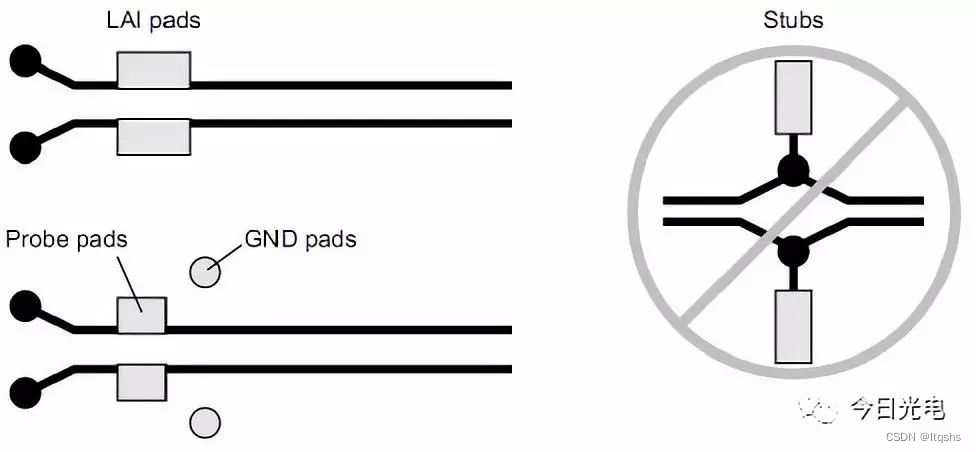

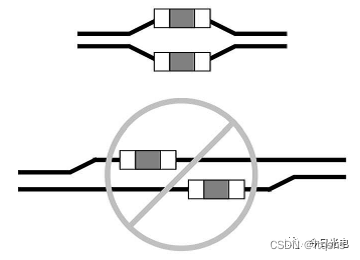

测试点(可以是过孔,焊盘或是元件)及探针脚应置于对称的位置,不应当在差分对引入stub,如图6:

图6

5.弯曲

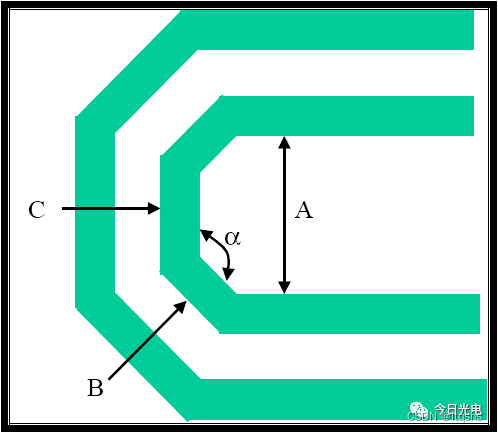

应尽量不使用弯曲,因为其会引入共模噪声。差分对使用弯曲应该遵循以下规则:(以图7为例)

1.所有弯曲的角度(α)应该≥135°;

2.保持走线间距(A)≥20mil;

3.片断,比如B和C,其侧翼有一个弯曲,其长度应该≥1.5倍的走线宽度。

图7

尽量使左弯曲的数量和右弯曲的数量相等。

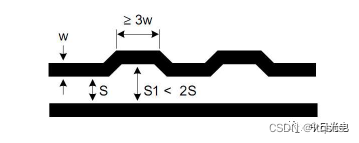

当一段蛇形线用来和另一段走线来进行长度匹配时,每段长弯折的长度必须至少15mil(3倍于5mil的线宽)。蛇行线弯折部分和差分线的另一条线的最大距离必须小于正常差分线线距的2倍。如图8所示:

图8

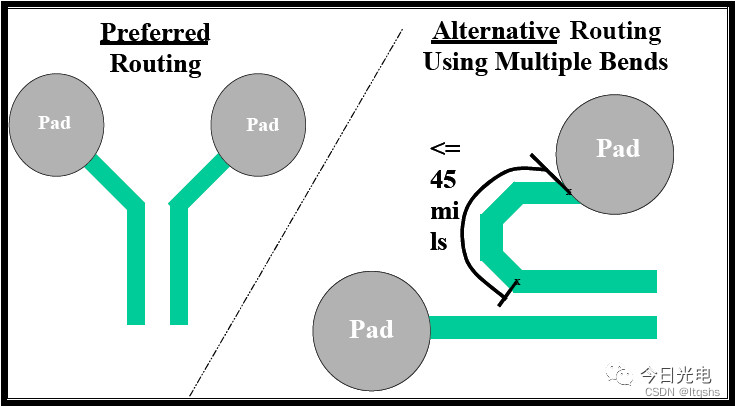

当使用多重弯曲布线到一个管脚或是一个BGA的焊盘的非匹配的部分应该≤45mil,如图9所示:

图9

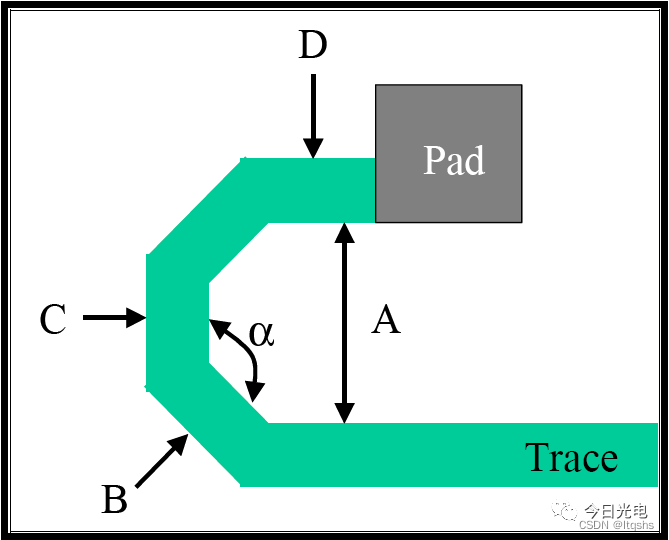

连接到焊盘的弯曲线应该遵循以下规则:(以图10为例)

1.所有弯曲的角度(α)应该≥135°;

2.保持走线间距(A)≥3倍的走线宽度;

3.B和C段其长度应该≥1.5倍的走线宽度;

4.D段应该尽量短。

图10

6.AC电容

PCIExpress需要在发送端和接收端之间交流耦合。差分对两个信号的交流耦合电容必须有相同的电容值,相同的封装尺寸,并且位置对称。

AC电容必须放在最靠近信号发送端的位置。电容值必须介于75nF到200nF之间(最好是100nF)。推荐使用0402封装,但是0603封装也是可以接受的。两电容应该对称放置,如图11所示:

图11

此外差分参考时钟应该和高速串行数据线一样使用相同几何结构的差分线。

参看原文:《PCI-Express接口的布线规则》

边栏推荐

- Network security CSRF

- STL标准模板库(Standard Template Library)一周学习总结

- Txt file virus

- Network security - information query of operating system

- Specific method example of V20 frequency converter manual automatic switching (local remote switching)

- php 使用阿里云存储

- USB(十六)2022-04-28

- Brush question 3

- Matlab 信号处理【问答随笔·2】

- Unity3D学习笔记5——创建子Mesh

猜你喜欢

Are the microorganisms in the intestines the same as those on the skin?

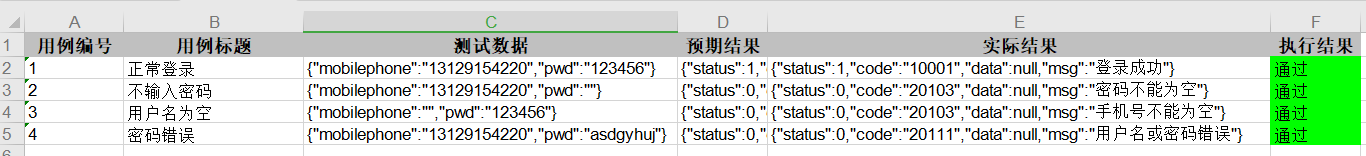

JMeter interface automated test read case, execute and write back result

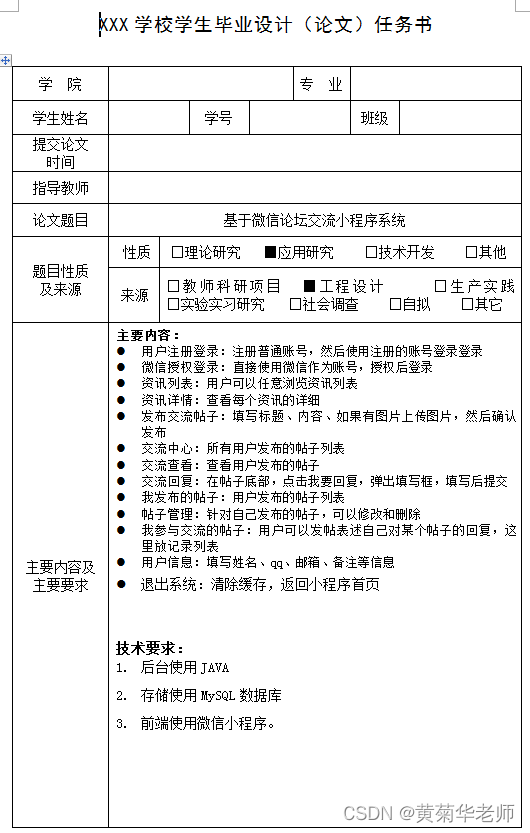

Wechat forum exchange applet system graduation design (5) assignment

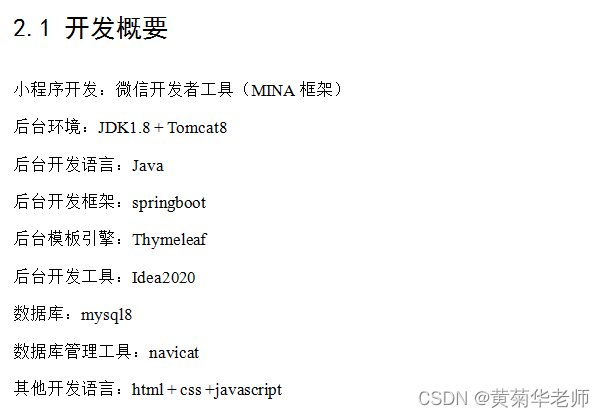

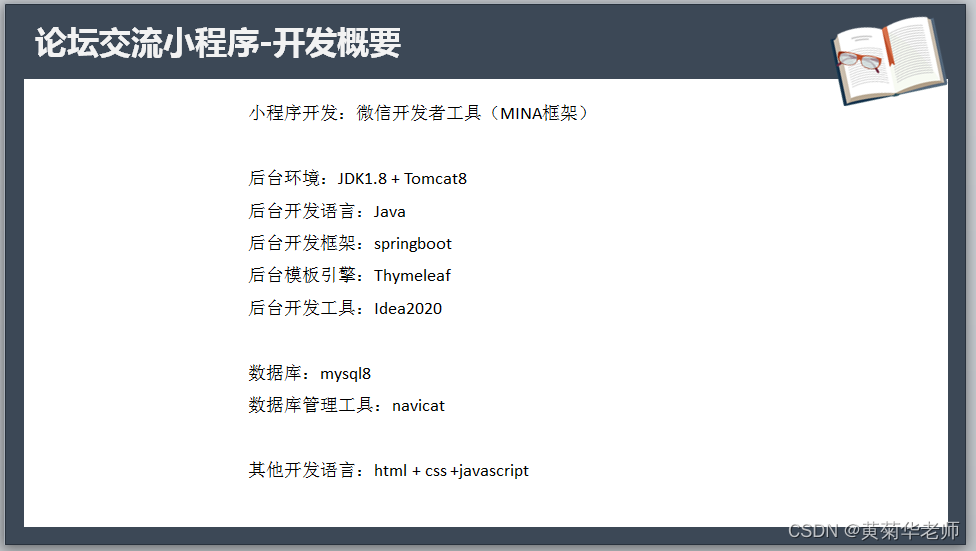

微信论坛交流小程序系统毕业设计毕设(1)开发概要

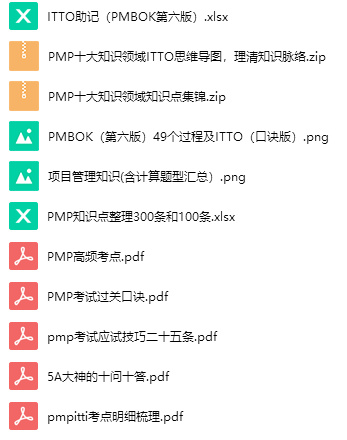

PMP project management exam pass Formula-1

云原生正在吞噬一切,开发者该如何应对?

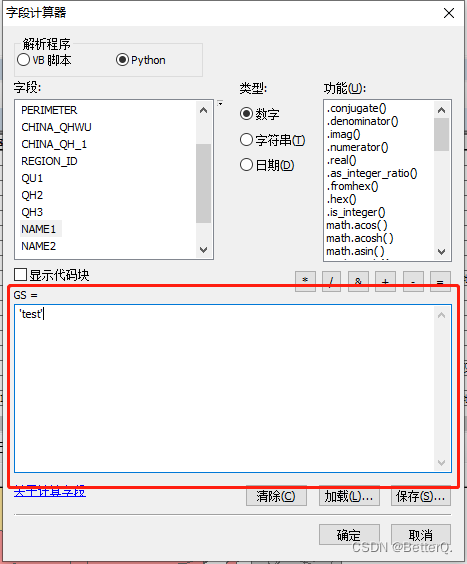

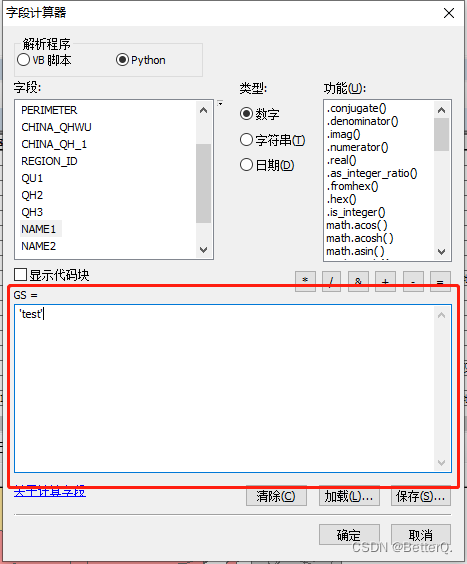

ArcGIS: field assignment_ The attribute table field calculator assigns values to fields based on conditions

Oracle-数据库的备份与恢复

ArcGIS:字段赋值_属性表字段计算器(Field Calculator)依据条件为字段赋值

Wechat forum exchange applet system graduation design completion (6) opening defense ppt

随机推荐

【编译原理】词法分析设计实现

云原生数据仓库AnalyticDB MySQL版用户手册

USB (十七)2022-04-15

Add data analysis tools in Excel

Unity3D学习笔记4——创建Mesh高级接口

Quelles sont les similitudes et les différences entre les communautés intelligentes et les villes intelligentes?

Guessing game (read data from file)

2021ICPC上海 H.Life is a Game Kruskal重构树

Grid

Circumvention Technology: Registry

UE4_UE5全景相机

Wechat forum exchange applet system graduation design completion (6) opening defense ppt

Install a new version of idea. Double click it to open it

The 19th Zhejiang Provincial Collegiate Programming Contest 2022浙江省赛 F.EasyFix 主席树

1. Sum of two numbers

U盘拷贝东西时,报错卷错误,请运行chkdsk

ArcGIS: two methods of attribute fusion of the same field of vector elements

Unity dynamically merges mesh textures

Technology at home and abroad people "see" the future of audio and video technology

PMP项目管理考试过关口诀-1