当前位置:网站首页>Abnormal mode of ARM processor

Abnormal mode of ARM processor

2022-07-04 12:34:00 【sydyh43】

1、ARM The processor has various exception modes , For response ARM Different states appear . When something unusual happens , Will then enter the relevant exception vector , meanwhile CPSR The register of will also be set to the specific mode .

example : When there is an interruption , No matter what kind of interruption , Will jump to 0x18 This main entrance address ( It could be 0xFFFFFF18, Look at the virtual address of the system initialization , It doesn't matter ), Then execute the specific interrupt registration function through the interrupt number .

At the same time, I will put CPSR The register is set to the corresponding mode .

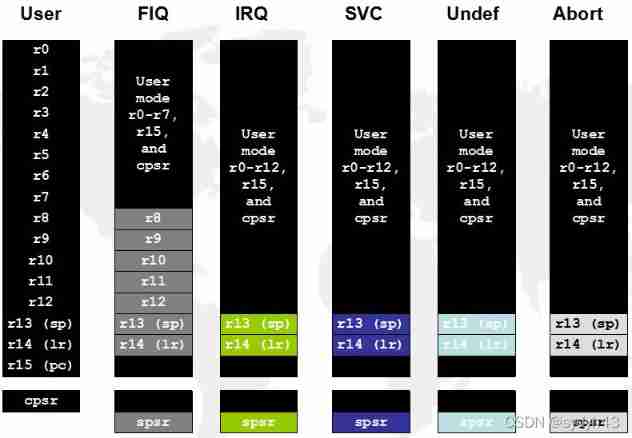

When switching from one mode to another , You need to put the previous mode HW context Save up , For example, from user mode to kernel mode , Because in the new mode , Memory area division is different . Here's the picture , The general register in each mode is the same , In two modes , It can be used to transmit information , But like sp,lr Space related registers will be independent .

2、 When something unusual happens , How to enter exception mode

2.1、 In the kernel boot phase , Initialize the exception vector table .

start_kernel

setup_arch

early_trap_initvoid __init early_trap_init(void *vectors_base)

{

unsigned long vectors = (unsigned long)vectors_base;

extern char __stubs_start[], __stubs_end[];

extern char __vectors_start[], __vectors_end[];

unsigned i;

vectors_page = vectors_base;

......

/*

* Copy the vectors, stubs and kuser helpers (in entry-armv.S)

* into the vector page, mapped at 0xffff0000, and ensure these

* are visible to the instruction stream.

*/

memcpy((void *)vectors, __vectors_start, __vectors_end - __vectors_start);

memcpy((void *)vectors + 0x1000, __stubs_start, __stubs_end - __stubs_start);

......

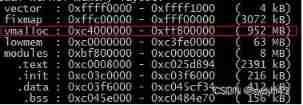

}The exception vector address is saved in vectors_base Variable (CONFIG_VECTORS_BASE=0xffff0000) in .

Exception vector address __vectors_start stay entry-armv.S - arch/arm/kernel/entry-armv.S - Linux source code (v5.16.9) - Bootlin Implement initialization .

At compile time , The address has been determined

grep "__vectors" System.map -nR![]()

When it starts , You can see the address distribution of the exception vector .

2.2、 When something unusual happens , Jump to the exception vector entry __vectors_start, Different exceptions correspond to different offsets , From the picture 1 It can be seen that software interrrupt Corresponding to the third term of the anomaly vector , namely W(ldr) pc, .L__vectors_start + 0x1000 Corresponding software interrupt Entrance .

.L__vectors_start:

W(b) vector_rst

W(b) vector_und

W(ldr) pc, .L__vectors_start + 0x1000

W(b) vector_pabt

W(b) vector_dabt

W(b) vector_addrexcptn

W(b) vector_irq

W(b) vector_fiq

.data

.align 2

.globl cr_alignmentSubsequently, it will jump to the specific exception vector processing process according to the macro definition .

.macro vector_stub, name, mode, correction=0

.align 5

vector_\name:

.if \correction

sub lr, lr, #\correction

.endif

@

@ Save r0, lr_<exception> (parent PC) and spsr_<exception>

@ (parent CPSR)

@

stmia sp, {r0, lr} @ save r0, lr

mrs lr, spsr

str lr, [sp, #8] @ save spsr

@

@ Prepare for SVC32 mode. IRQs remain disabled.

@

mrs r0, cpsr

eor r0, r0, #(\mode ^ SVC_MODE | PSR_ISETSTATE)

msr spsr_cxsf, r0

@

@ the branch table must immediately follow this code

@

and lr, lr, #0x0f

THUMB( adr r0, 1f )

THUMB( ldr lr, [r0, lr, lsl #2] )

mov r0, sp

ARM( ldr lr, [pc, lr, lsl #2] )

movs pc, lr @ branch to handler in SVC mode

ENDPROC(vector_\name)边栏推荐

- It's hard to hear C language? Why don't you take a look at this (V) pointer

- Entitas learning [3] multi context system

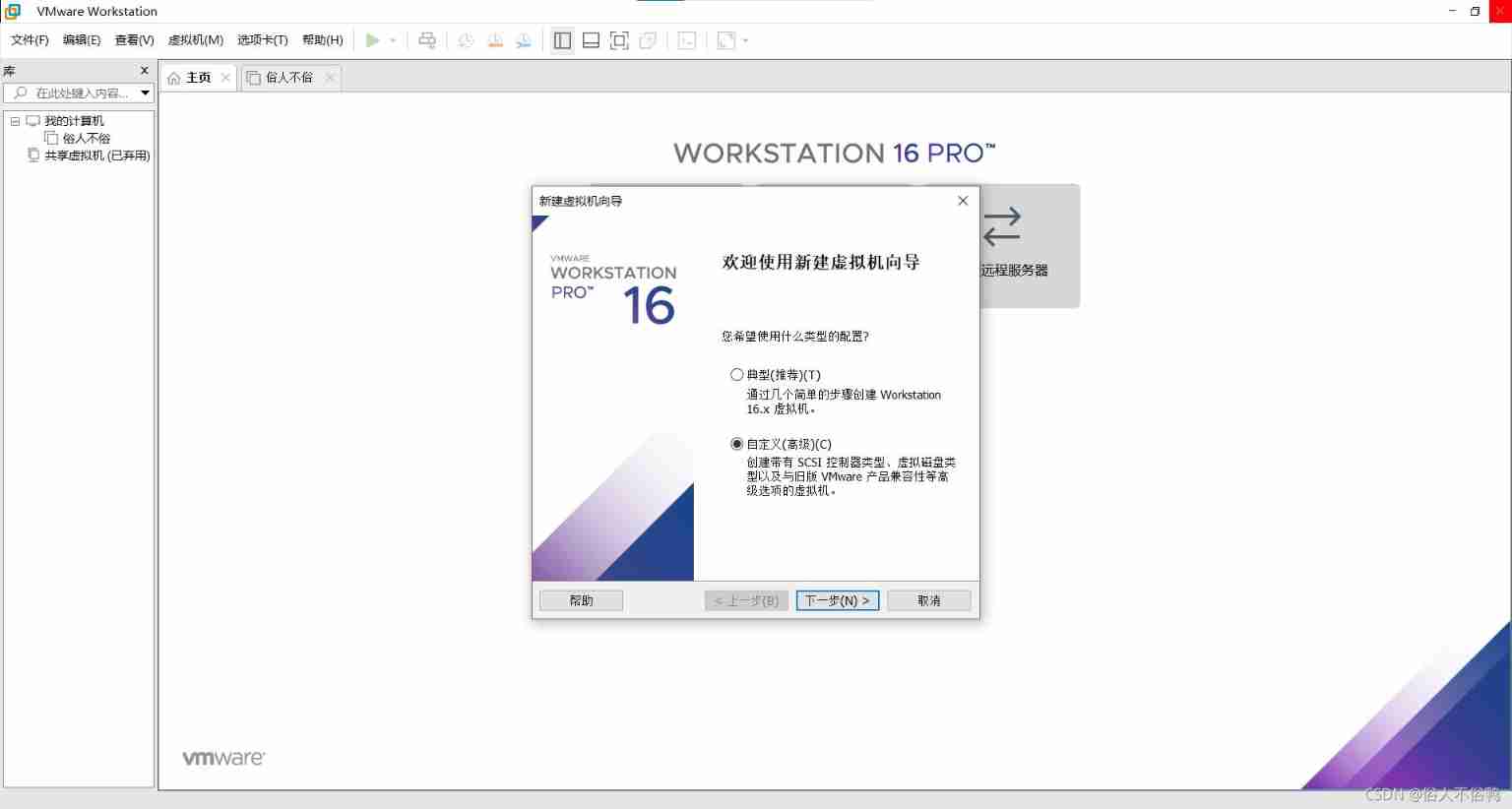

- How to create a new virtual machine

- [Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 5

- Global and Chinese market of cardiac monitoring 2022-2028: Research Report on technology, participants, trends, market size and share

- Detailed explanation of classic process synchronization problems

- 2021-08-09

- Decrypt the advantages of low code and unlock efficient application development

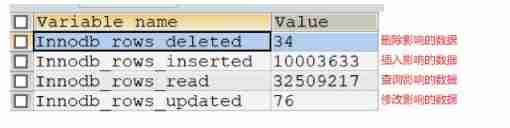

- MySQL advanced (Advanced) SQL statement

- Wechat video Number launches "creator traffic package"

猜你喜欢

Star leap plan | new projects are continuously being recruited! MSR Asia MSR Redmond joint research program invites you to apply!

Lecture 9

![[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 12](/img/b1/926d9b3d7ce9c5104f3e81974eef07.jpg)

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 12

MySQL performance optimization index

![[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 22](/img/e0/21367eeaeca10c0a2f2aab3a4fa1fb.jpg)

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 22

Ultimate bug finding method - two points

Servlet learning notes

22 API design practices

![[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 8](/img/16/33f5623625ba817e6e022b5cb7ff5d.jpg)

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 8

How to create a new virtual machine

随机推荐

Experiment 7. IPv6

Pat 1059 prime factors (25 points) prime table

What if the chat record is gone? How to restore wechat chat records on Apple Mobile

Flet教程之 按钮控件 ElevatedButton入门(教程含源码)

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 11

Method of setting default items in C # ComboBox control code

[directory] search

Haproxy cluster

How to create a new virtual machine

LxC shared directory addition and deletion

AI should take code agriculture? Deepmind offers a programming version of "Alpha dog" alphacode that surpasses nearly half of programmers!

asp. Core is compatible with both JWT authentication and cookies authentication

How to use the mongodb ID array to get multiple documents- How to get multiple document using array of MongoDb id?

[Android reverse] function interception instance (③ refresh CPU cache | ④ process interception function | ⑤ return specific results)

CSDN documentation specification

The database connection code determines whether the account password is correct, but the correct account password always jumps to the failure page with wrong account password

VBA, JSON interpretation, table structure -json string conversion

netstat

[Yunju entrepreneurial foundation notes] Chapter II entrepreneur test 10

It's hard to hear C language? Why don't you take a look at this (V) pointer