当前位置:网站首页>Armv8-a programming guide MMU (2)

Armv8-a programming guide MMU (2)

2022-07-06 10:58:00 【Linux decoder】

1.1 TLB

TLB yes MMU Cache of recently accessed page transformations in . For each memory access of the processor ,MMU Check TLB Whether the conversion is cached . If the requested address translation is TLB Hit in the middle , Address translation is effective immediately .

Every TLB Items usually contain more than physical and virtual addresses , It also contains attributes such as memory type ,cache Strategy , Access right ,ASID, and VMID. If TLB Does not contain a valid translation of the virtual address issued by the processor (TLB Not hit ), Issue an external conversion table walk Or transform table lookup .MMU The hardware in makes it read the conversion table in memory . If the conversion table walk Did not lead to page fault, The newly loaded transformation may be cached in TLB in .TLB The specific structure of is based on ARM There are differences in the implementation of processors .

If OS Revised TLB Cached transformation table entries in ,OS Responsible for invalidation stale TLB term .

When executed A64 Code ,TLBI by TLB Invalidation instructions .

TLBI <type><level>{IS}{,<Xt>}The following list give type Some public choices for domains .

ALL all TLB term

VMALL all TLB term . At present guest OS Of stage1

VMALLS12 all TLB term . At present guest OS Of stage1 and stage2

ASID stay Xt Match ASID term

VA Xt in VA and ASID Specified item

VAA Xt in VA Specified item , arbitrarily ASID

EL3,EL2,EL1 The exception level operation of is applied to its own virtual address space .IS The domain indicates that this applies only to inner shareable term .

NOTE: see Context Switching About ASID And transformation table configuration .

<level> The domain simply indicates the exception level virtual address space of the operation application .

IS The field indicates that this is only for inner shareable term .

| TLB Invalidate command | Parameters | describe |

| ALLEn | TLB Invalidate all ,ELn | |

| ALLEnIS | TLB Invalidate all ,ELn,inner shareable | |

| ASIDE1 | adopt ASID Of TLB To invalidate ,EL1 | |

| ASIDE1IS | adopt ASID Of TLB To invalidate ,EL1,inner shareable | |

| IPAS2E1 | adopt IPA Of TLB To invalidate ,stage2,EL1 | |

| IPAS2E1IS | adopt IPA Of TLB To invalidate ,stage2,EL1,inner shareable | |

| VAAE1 | adopt VA Of TLB To invalidate , all ASID,EL1 | |

| VAAE1IS | adopt VA Of TLB To invalidate , all ASID,EL1,inner shareable | |

| VAALE1IS | adopt VA The last level of TLB To invalidate , all ASID,EL1,inner shareable | |

| VAEn | adopt VA Of TLB To invalidate ,ELn | |

| VAEnIS | adopt VA Of TLB To invalidate ,ELn,inner shareable | |

| VALEn | adopt VA The last level of TLB To invalidate ,ELn | |

| VALEnIS | adopt VA The last level of TLB To invalidate ,ELn,inner shareable | |

| VMALLE1 | adopt VMID Of TLB To invalidate ,stage1, EL1 | |

| VMALLE1IS | adopt VMID Of TLB To invalidate ,stage1, EL1,inner shareable | |

| VMALLS12E1 | adopt VMID Of TLB To invalidate ,stage1 and stage2,EL1 | |

| VMALLS12E1IS | adopt VMID Of TLB To invalidate ,stage1 and stage2,EL1,inner shareable |

The following code example shows writing a code by inner shareable Timing of memory post conversion table :

<writes to translation tables>

DSB ISHST

TLBI ALLE1

DSB ISH

ISBsuch as , Modify the conversion table entry , Use instruction :

TLBI VAE1,X0This will invalidate X0 Register specified address related conversion table entry .

TLB The conversion table items that can be cached are fixed . You can minimize the external memory access caused by conversion table traversal and get higher TLB Hit rate to get higher performance .ARMv8-A Architecture provides contiguous block Features to use effectively TLB Space . Each conversion table block Item contains one contiguous position . When setting , This bit tells TLB It can cache only one table item to cover multiple block. Find and index one at a time contigous Address range covered by the block . therefore TLB You can cache a table entry with a defined address range , Enable it to TLB Store a wider range of virtual addresses in .

In order to use contiguous position , These continuous block Must be connected , That is, they must be related to the continuous range of virtual addresses . They must start at the aligned boundary , Consistent properties , And point to the continuous output address range of the same level of conversion . The required alignment is 4KB Granular VA[20:16] or 64KB Granular VA[28:21] For all addresses the same . The following requirements :

(1)16*4KB The connected blocks give 4KB Granular 64KB term ;

(2)32*32MB The connected blocks give L2 Descriptors 1GB Table item ,128*16KB Give when using 16KB when L3 Descriptors 2MB Table item ;

(3)32*64KB The connected blocks give 64KB Granular 2MB Table item .

If these conditions are met , A program error occurs , This can lead to TLB abort Or look for a run . These errors include :

(1) One or more table entries do not contain contiguous position ;

(2) The output of one of the entries exceeds the alignment range .

about ARMv8 framework , Wrong use is not allowed EL0 and EL1 Check the permissions of valid address range , or EL3 Wrong access to space .

边栏推荐

- [BMZCTF-pwn] 12-csaw-ctf-2016-quals hungman

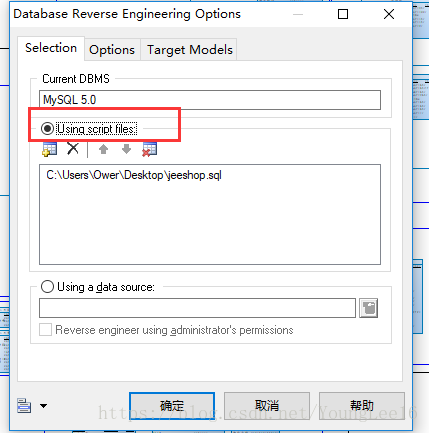

- Navicat 導出錶生成PDM文件

- CSDN-NLP:基于技能树和弱监督学习的博文难度等级分类 (一)

- A trip to Macao - > see the world from a non line city to Macao

- Mysql27 index optimization and query optimization

- Valentine's Day is coming, are you still worried about eating dog food? Teach you to make a confession wall hand in hand. Express your love to the person you want

- Ubuntu 20.04 安装 MySQL

- Navicat 导出表生成PDM文件

- C language string function summary

- Discriminant model: a discriminant model creation framework log linear model

猜你喜欢

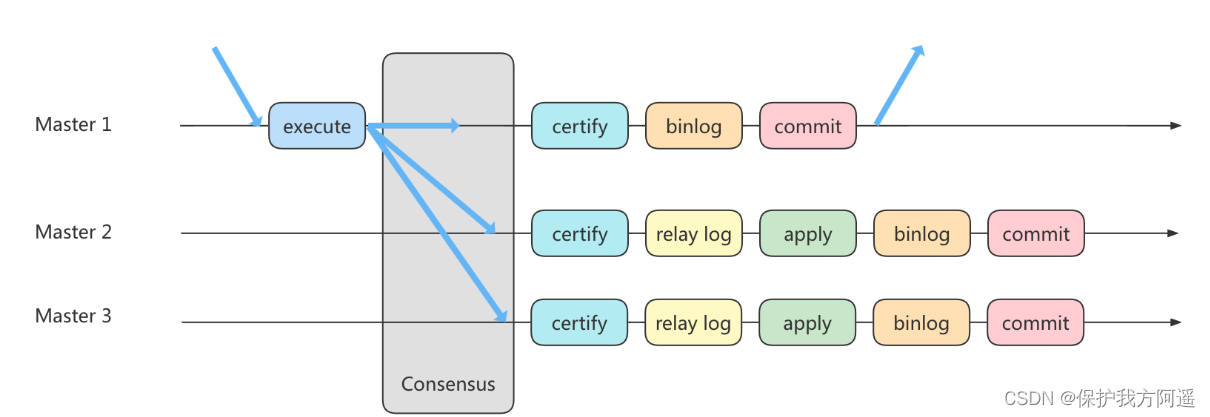

Mysql35 master slave replication

![[Li Kou 387] the first unique character in the string](/img/2d/f2c99549cac86c08efbfbd8ba76427.jpg)

[Li Kou 387] the first unique character in the string

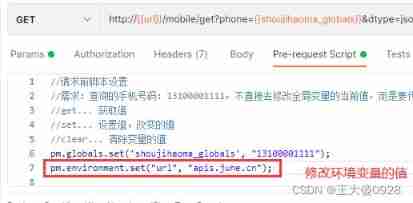

Postman uses scripts to modify the values of environment variables

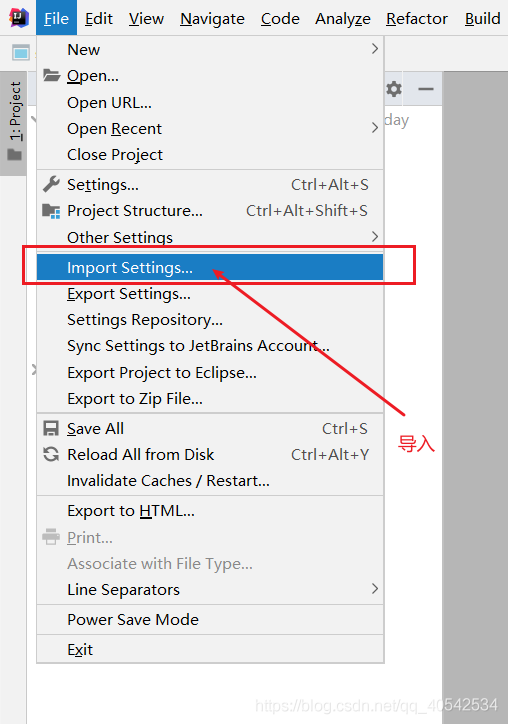

IDEA 导入导出 settings 设置文件

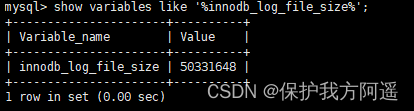

MySQL31-MySQL事务日志

Opencv uses freetype to display Chinese

![[recommended by bloggers] C MVC list realizes the function of adding, deleting, modifying, checking, importing and exporting curves (with source code)](/img/b7/aae35f049ba659326536904ab089cb.png)

[recommended by bloggers] C MVC list realizes the function of adding, deleting, modifying, checking, importing and exporting curves (with source code)

![[recommended by bloggers] C WinForm regularly sends email (with source code)](/img/5d/57f8599a4f02c569c6c3f4bcb8b739.png)

[recommended by bloggers] C WinForm regularly sends email (with source code)

Generate PDM file from Navicat export table

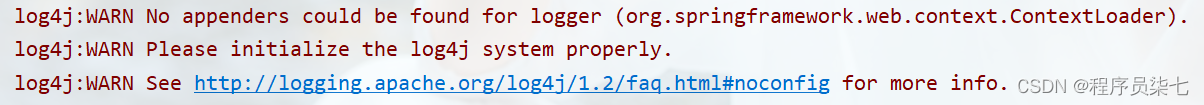

解决:log4j:WARN Please initialize the log4j system properly.

随机推荐

Global and Chinese market of thermal mixers 2022-2028: Research Report on technology, participants, trends, market size and share

@Controller, @service, @repository, @component differences

Mysql35 master slave replication

Copy constructor template and copy assignment operator template

@controller,@service,@repository,@component区别

Case identification based on pytoch pulmonary infection (using RESNET network structure)

MySQL30-事务基础知识

Invalid global search in idea/pychar, etc. (win10)

Ubuntu 20.04 安装 MySQL

MySQL24-索引的数据结构

Timestamp with implicit default value is deprecated error in MySQL 5.6

SSM整合笔记通俗易懂版

[paper reading notes] - cryptographic analysis of short RSA secret exponents

Solution: log4j:warn please initialize the log4j system properly

Mysql 其他主机无法连接本地数据库

[BMZCTF-pwn] 12-csaw-ctf-2016-quals hungman

frp内网穿透那些事

Adaptive Bezier curve network for real-time end-to-end text recognition

Breadth first search rotten orange

Mysql30 transaction Basics