当前位置:网站首页>SOC_ SD_ CMD_ FSM

SOC_ SD_ CMD_ FSM

2022-07-05 07:07:00 【Eight four one one】

Catalog

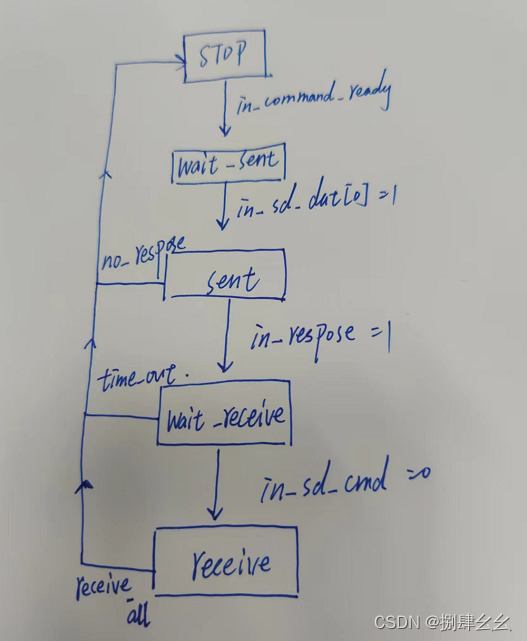

1. State machine flow chart

- CMD_STATE_STOP: In my spare time

- CMD_STATE_WAIT_SEND: Waiting to be sent

- CMD_STATE_SEND: In sending

- CMD_STATE_WAIT_RECEIVE: Waiting to receive

- CMD_STATE_RECEIVE: Receiving

2. Interface description

- Clock reset soft reset

- There are two response types ,R2 The response is long in_longresponse, Others are in_response

- Drive the state machine to work in_command_ready The signal

- sd The data signal from the card in_sd_dat And command signals in_sd_cmd

- Send and receive signals to two younger brother modules has_send_bit、has_receive_bit And the current state of the state machine current_state

- Give back sd Card response feedback signal end_command、end_command_and_response、response_timeout

input in_sd_clk;

input in_soft_reset;

input hrst_n;

//sd if

input in_longresponse;

input in_response;

input in_command_ready;

//sd bus (sd card)

input [3:0] in_sd_dat;

input in_sd_cmd;

// Give two younger brother modules

output [2:0] current_state;

output [5:0] has_send_bit;

output [7:0] has_receive_bit;

// return sd if

output end_command;

output end_command_and_response;

output response_timeout;

3. Response digit selection

- Long response R2 yes 136bit, The short response is 48bit

assign need_to_receive_bit = in_longresponse ? 8'd136 : 8'd47; // Use to compare with has received bits

4. Three stage state machine

① The first paragraph describes sub state migration , The default state is CMD_STATE_STOP

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

current_state <= `CMD_STATE_STOP;

else if (!in_soft_reset)

current_state <= `CMD_STATE_STOP;

else

current_state <= next_state;

end

② The second segment of the state machine , Describe state transition with combinatorial logic , Complete the corresponding transition according to the above state transition diagram

always @(*) begin

case (current_state)

`CMD_STATE_STOP:

if (in_command_ready)

next_state = `CMD_STATE_WAIT_SEND;

else

next_state = current_state;

`CMD_STATE_WAIT_SEND:

if (in_sd_dat[0])

next_state = `CMD_STATE_SEND;

else

next_state = current_state;

`CMD_STATE_SEND:

if (has_send_bit != 47)

next_state = `CMD_STATE_SEND;

else if (!in_response)

next_state = `CMD_STATE_STOP;

else

next_state = `CMD_STATE_WAIT_RECEIVE;

`CMD_SEND_WAITE_RECEIVE:

if(resp_time == 7'b0111111)

next_state = `CMD_STATE_STOP;

else if (!in_sd_cmd)

next_state = `CMD_STATE_RECEIVE;

else

next_state = `CMD_SEND_WAITE_RECEIVE;

`CMD_STATE_RECEIVE:

if(has_receive_bit == (need_to_receive_bit - 1))

next_state = `CMD_STATE_STOP;

else

next_state = `CMD_STATE_RECEIVE;

default: next_state = `CMD_STATE_STOP;

endcase

end

③ The third segment of the state machine , Describe what actions each State performs , It mainly includes the assignment of the following signals

- has_send_bit: Sent bit Count

- receive_bit_counter_en: receive bit Counter enable

- resp_time_counter_en: Wait for the timeout counter to enable

- end_command_and_response: The signal of the end of the whole cycle of the responding command

- end_command: Unresponsive command end signal of the whole cycle

- response_timeout: Wait for the timeout signal

always @(*) begin

case (current_state)

`CMD_STATE_STOP:

begin

has_send_bit = 1'b0;

receive_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command_and_response = 1'b0;

end_command = 1'b0;

response_timeout =1'b0;

end

`CMD_STATE_WAIT_SEND:

begin

has_send_bit = 1'b0;

receive_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command_and_response = 1'b0;

end_command = 1'b0;

response_timeout =1'b0;

end

`CMD_STATE_SEND:

begin

receive_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command_and_response = 1'b0;

end_command = 1'b0;

response_timeout =1'b0;

if (has_send_bit !=47)

begin

send_bit_counter_en = 1'b1;

next_state = `CMD_STATE_SEND;

end

else

begin

if(!in_response)

begin

next_state = `CMD_STATE_STOP;

send_bit_counter_en = 1'b0 ;

end_command_and_response= 1'b1;

end_command = 1'b1;

end

else

begin

next_state =`CMD_STATE_WAIT_RECEIVE;

send_bit_counter_en = 1'b0;

end_command = 1'b1 ;

end

end

end

`CMD_SEND_WAITE_RECEIVE:

begin

end_command = 1'b1;

send_bit_counter_en = 1'b0;

receive_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command_and_response = 1'b0;

response_timeout =1'b0;

if(resp_time == 7'b0111111)

response_timeout = 1'b1;

else if (!in_sd_cmd)

resp_time_counter_en = 1'b0;

else

resp_time_counter_en = 1'b1;

end

`CMD_STATE_RECEIVE:

begin

send_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command = 1'b1;

end_command_and_response = 1'b0;

response_timeout = 1'b0;

if(has_receive_bit == (need_to_receive_bit - 1))

begin

end_command_and_response = 1'b1;

receive_bit_counter_en = 1'b0;

end

else

receive_bit_counter_en = 1'b1;

end

default:

begin

has_send_bit = 1'b0;

receive_bit_counter_en = 1'b0;

resp_time_counter_en = 1'b0;

end_command_and_response = 1'b0;

end_command = 1'b0;

response_timeout =1'b0;

end

endcase

end

5. Corresponding 3 A counter

- Send count

- Receive count

- Timeout count

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

has_send_bit <= 6'b0;

else if(!in_soft_reset)

has_send_bit <= 6'b0;

else

begin

if(has_send_bit == 47)

has_send_bit <= 6'b0;

else if (send_bit_counter_en == 1'b1)

has_send_bit <= has_send_bit + 1;

end

end

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

has_receive_bit <= 8'b0;

else if (!in_soft_reset)

has_receive_bit <= 8'b0;

else begin

if(has_receive_bit == (need_to_receive_bit - 1))

has_receive_bit <= 8'b0;

else if (receive_bit_counter_en == 1'b1)

has_receive_bit <= has_receive_bit + 1;

end

end

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

resp_time <= 7'b0;

else if (!in_soft_reset)

resp_time <= 7'b0;

else if( current_state == `CMD_STATE_RECEIVE)

resp_time <= 7'b0;

else if (resp_time == 63)

resp_time <= 7'b0;

else if (resp_time_counter_en == 1'b1)

resp_time <= resp_time + 1;

end

边栏推荐

- .net core踩坑实践

- Error: "mountvolume.setup failed for volume PVC fault handling

- C语言数组专题训练

- CGroup CPU group source code analysis

- Technical conference arrangement

- [software testing] 06 -- basic process of software testing

- Unity UGUI不同的UI面板或者UI之间如何进行坐标匹配和变换

- Preemption of CFS scheduling

- testing framework

- postmessage通信

猜你喜欢

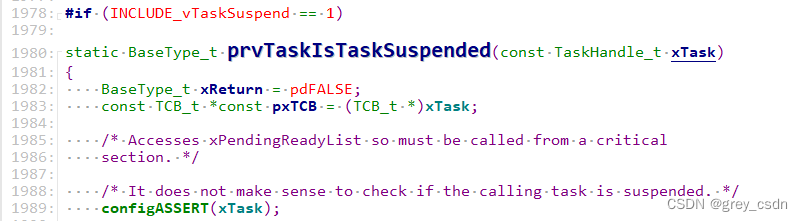

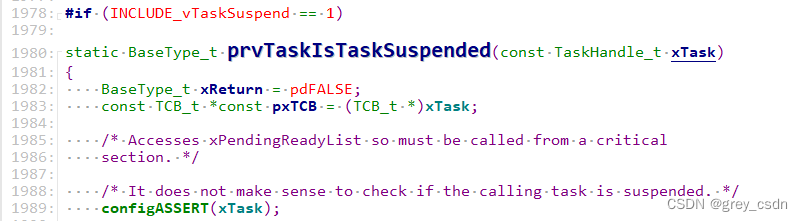

1290_FreeRTOS中prvTaskIsTaskSuspended()接口实现分析

All English in the code

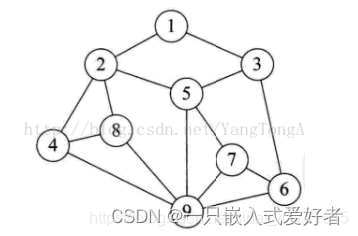

逻辑结构与物理结构

![[algorithm post interview] interview questions of a small factory](/img/62/6e330b1eba38f2dc67b21a10f0e2a8.jpg)

[algorithm post interview] interview questions of a small factory

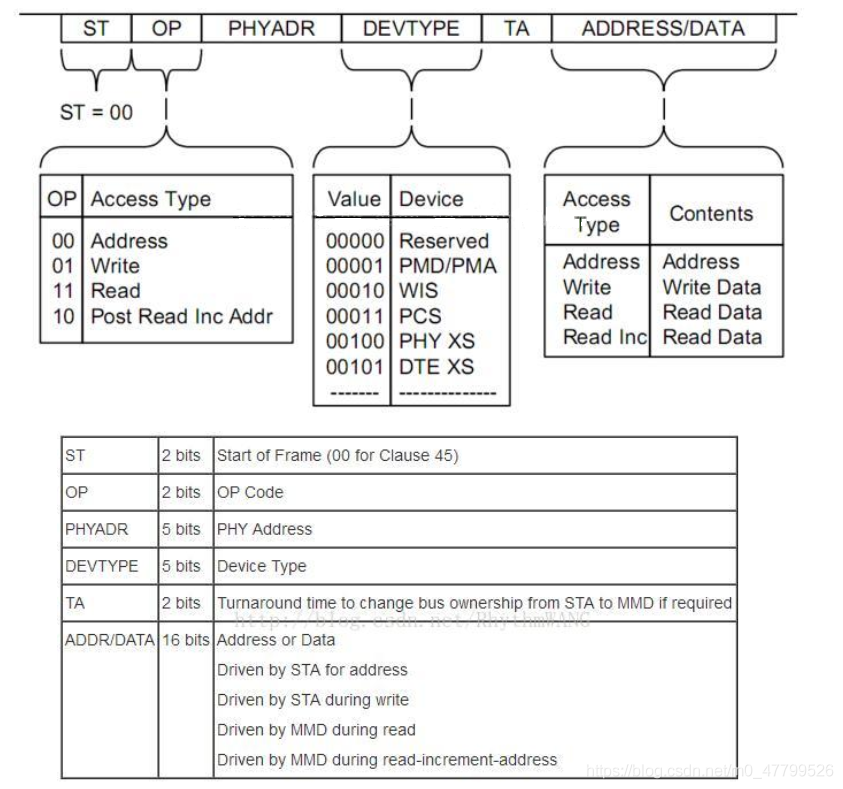

PHY drive commissioning --- mdio/mdc interface Clause 22 and 45 (I)

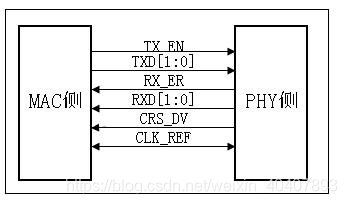

Literacy Ethernet MII interface types Daquan MII, RMII, smii, gmii, rgmii, sgmii, XGMII, XAUI, rxaui

ROS2——topic话题(八)

1290_ Implementation analysis of prvtaskistasksuspended() interface in FreeRTOS

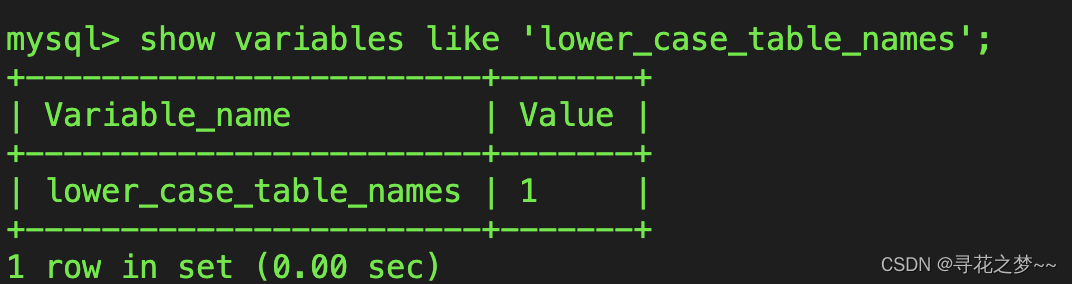

【MySQL8.0不支持表名大写-对应方案】

网易To B,柔外刚中

随机推荐

Sre core system understanding

[software testing] 06 -- basic process of software testing

vim

Orin 安装CUDA环境

SD_CMD_RECEIVE_SHIFT_REGISTER

并发编程 — 如何中断/停止一个运行中的线程?

Interpretation of the earliest sketches - image translation work sketchygan

Ros2 - common command line (IV)

ROS2——配置开发环境(五)

Unity ugui how to match and transform coordinates between different UI panels or uis

Rehabilitation type force deduction brush question notes D1

Special training of C language array

Xiaomi written test real question 1

Qt项目中的日志库log4qt使用

Ros2 - Service Service (IX)

IPage can display data normally, but total is always equal to 0

Database mysql all

The differences and connections among cookies, sessions, JWT, and tokens

1290_FreeRTOS中prvTaskIsTaskSuspended()接口实现分析

Inftnews | drink tea and send virtual stocks? Analysis of Naixue's tea "coin issuance"