当前位置:网站首页>【VHDL 并行语句执行】

【VHDL 并行语句执行】

2022-07-07 04:29:00 【又菜又爱玩_】

VHDL 判断信号上升沿的一种方式

一般的检测时钟上升沿

方法一:rising_edge 是非常严格的上升沿,必须从0到1 ,

方法二:(clk’event and clk=‘1’) 可以从 X 到 1

两种方式很好理解

/

问题

由于最近才接触FPGA,学习VHDL语言,碰到了一个初学者可能都会碰到的问题

clk10khz_d1 <= clk10khz;

clk10khz_d2 <= clk10khz_d1;

if key_cs='1' and clk10khz_d1='1' and clk10khz_d2='0' then --(判断上升沿)

.......

end if;

看到这里,clk10khz 的值给 clk10khz_d1 , clk10khz_d1的值再给clk10khz_d2,

这样一来clk10khz ,clk10khz_b1 ,clk10khz_b2 不应该是一样? 是不是错了?

后来看了很多检测上升沿的代码,都是这样,也没有解释。

其实就是 非阻塞赋值 和 阻塞赋值 的区别 , 资深的VHDL玩家就会觉得这个问题太基础不过了。

什么是非阻塞赋值?

非阻塞赋值操作符用小于等于号(即<=)表示。

为在赋值操作时刻开始时计算非阻塞赋值符的RHS表达式,赋值操作时刻结束时更新LHS。在计算非阻塞赋值的RHS表达式和更新LHS期间,其他的语句,包括其他的非阻塞赋值语句都能同时计算RHS表达式和更新LHS。非阻塞赋值允许其他的语句同时进行操作。

非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将begin-end之间的所有赋值语句同时赋值到赋值语句的左边,注意:是begin—end之间的所有语句,一起执行,且一个时钟只执行一次。

两种不同的赋值方式结果是不同的,非阻塞赋值b<=a;c<=b;两条语句是同时执行的,而阻塞赋值b=a;c=b;两条语句先执行b=a后执行c=b。

为什么能检测上升沿?

知道了什么是非阻塞赋值,那就很容易理解检测上升沿的方法了

clk10khz_d1 <= clk10khz;

clk10khz_d2 <= clk10khz_d1;

两句语句一起执行,假设clk10khz状态为 …01… (上升沿时)

在低电平时 clk10khz_d1 , clk10khz_d2 都被赋为了0 ,

在上升沿的顺间,同时执行两句语句时 clk10khz_d2 还是 被之前 clk10khz_d1存的值赋为了0;

此时clk10khz上升为1 , clk10khz_d1 被赋值为1.

由此通过clk10khz_d1='1' and clk10khz_d2='0检测信号上升沿。

也就是说两句赋值语句的顺序并不重要,反过来结果都一样。

边栏推荐

- Operation suggestions for today's spot Silver

- L'externalisation a duré trois ans.

- A bit of knowledge - about Apple Certified MFI

- Button wizard collection learning - mineral medicine collection and running map

- [OBS] win capture requires winrt

- 2022-07-06:以下go语言代码是否会panic?A:会;B:不会。 package main import “C“ func main() { var ch chan struct

- [P2P] local packet capturing

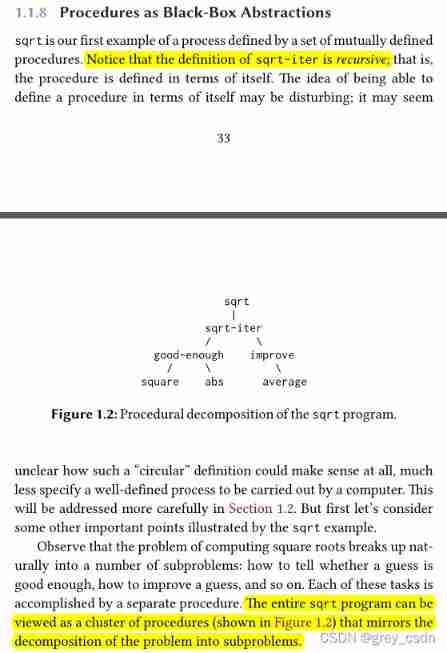

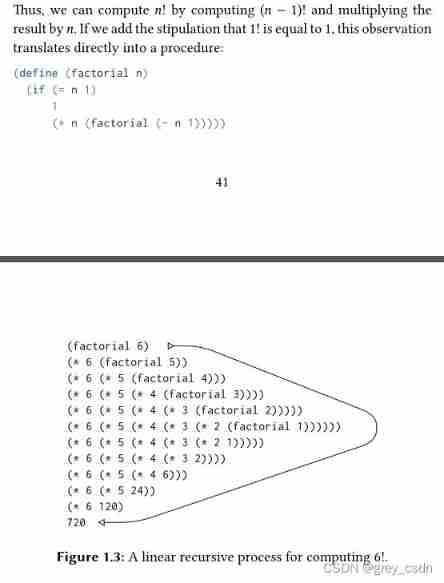

- 1142_ SiCp learning notes_ Functions and processes created by functions_ Linear recursion and iteration

- Is the test cycle compressed? Teach you 9 ways to deal with it

- Pytest+allure+jenkins environment -- completion of pit filling

猜你喜欢

leetcode:105. Constructing binary trees from preorder and inorder traversal sequences

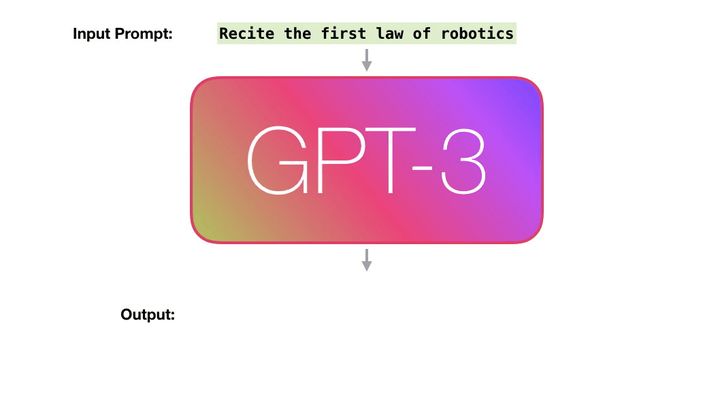

图解GPT3的工作原理

1141_ SiCp learning notes_ Functions abstracted as black boxes

After 95, the CV engineer posted the payroll and made up this. It's really fragrant

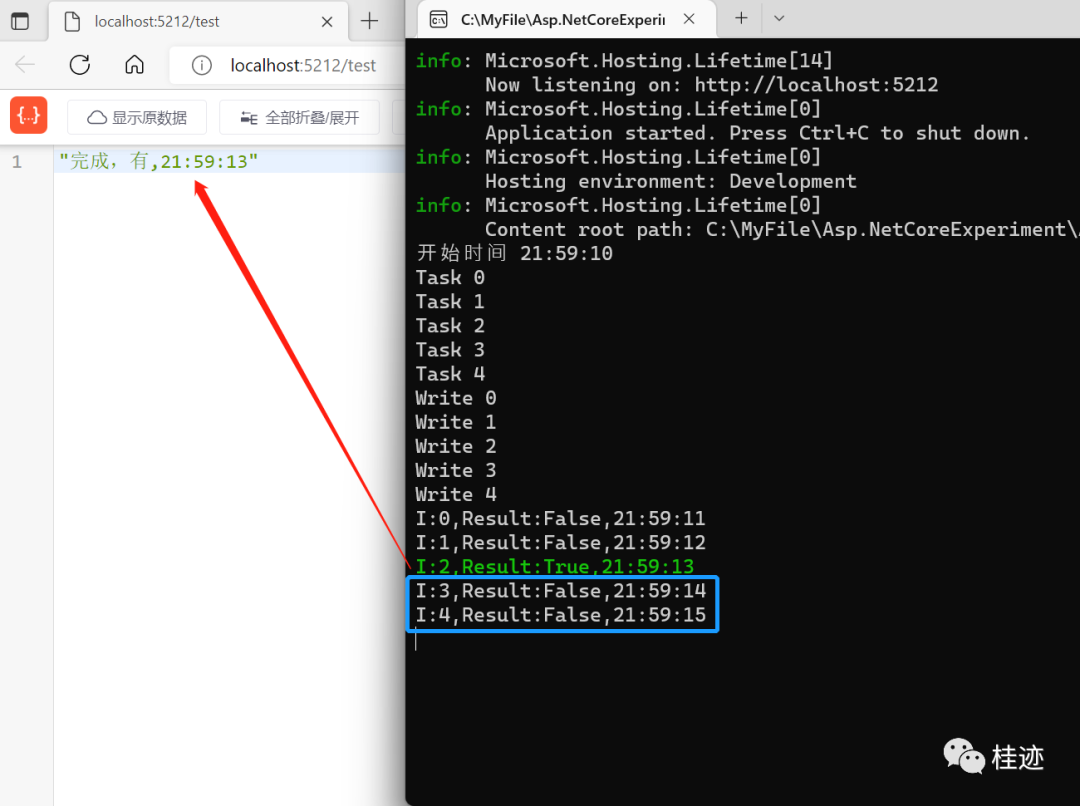

A concurrent rule verification implementation

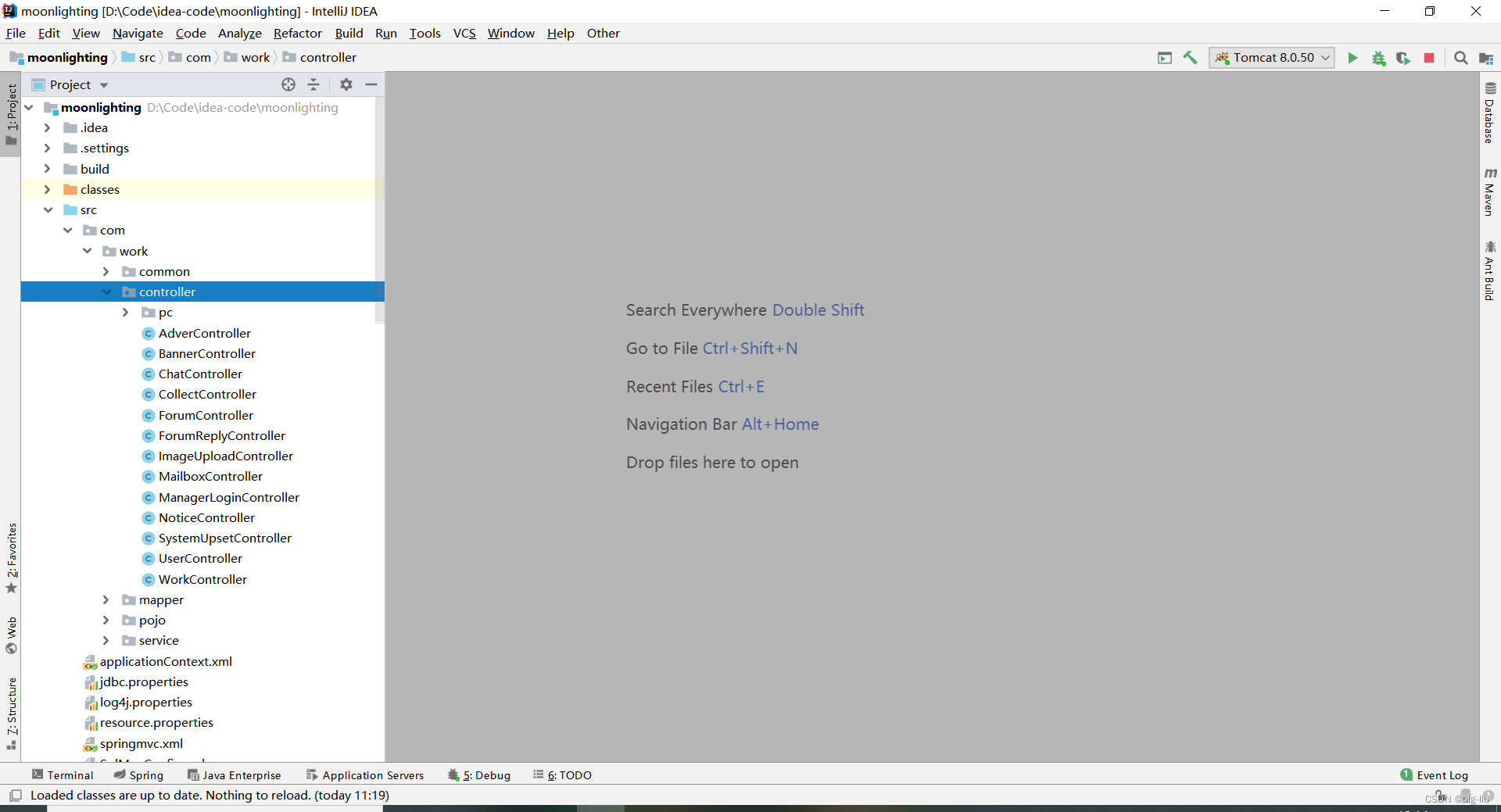

毕设-基于SSM大学生兼职平台系统

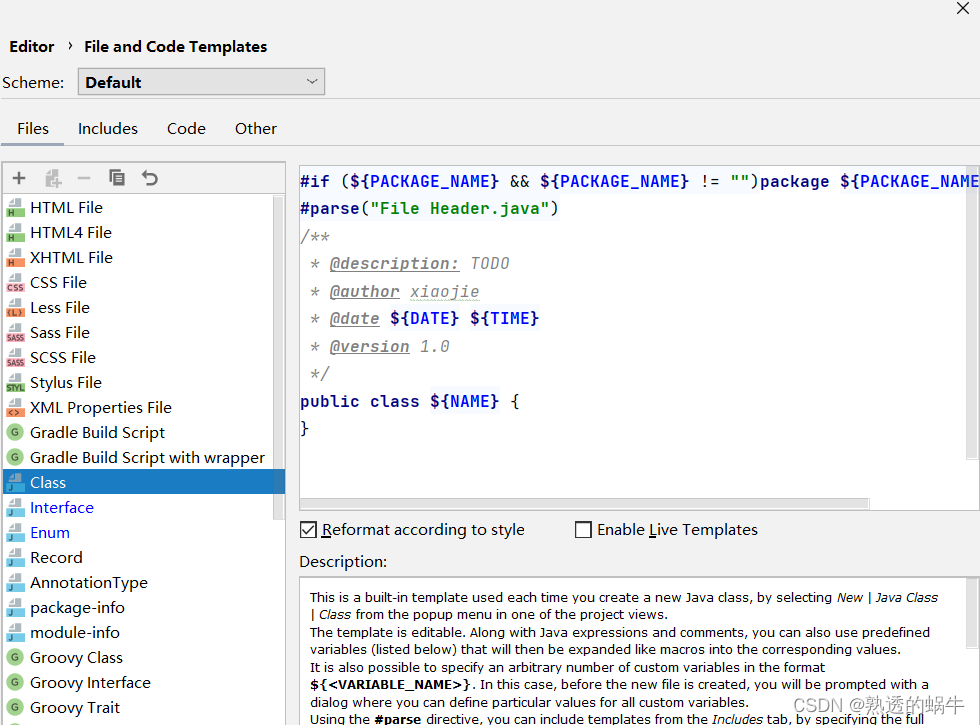

Idea add class annotation template and method template

1142_ SiCp learning notes_ Functions and processes created by functions_ Linear recursion and iteration

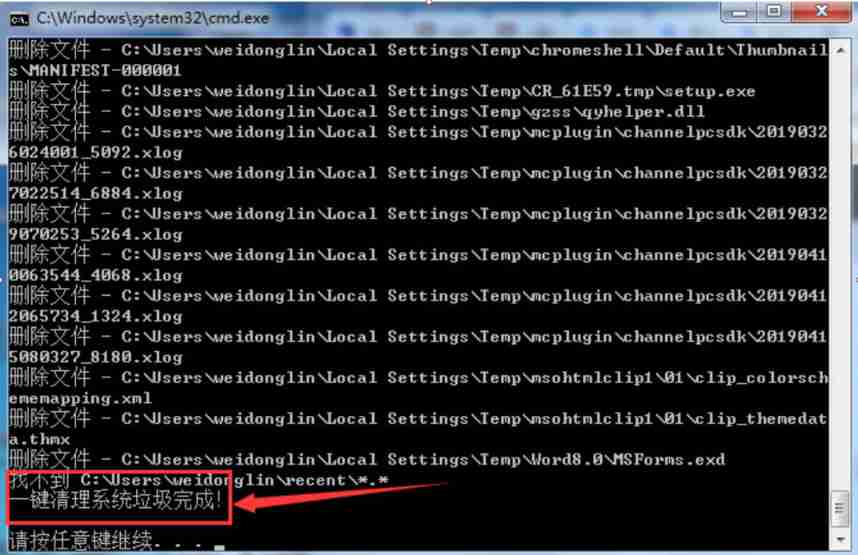

Make a bat file for cleaning system garbage

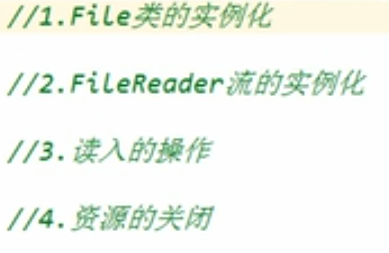

IO stream file

随机推荐

../ And/

[performance pressure test] how to do a good job of performance pressure test?

4、 High performance go language release optimization and landing practice youth training camp notes

Solution: could not find kf5 (missing: coreaddons dbusaddons doctools xmlgui)

[ANSYS] learning experience of APDL finite element analysis

Why should we understand the trend of spot gold?

解决could not find or load the Qt platform plugin “xcb“in ““.

After 95, the CV engineer posted the payroll and made up this. It's really fragrant

JS plot flot application - simple curve

nacos

1142_ SiCp learning notes_ Functions and processes created by functions_ Linear recursion and iteration

A concurrent rule verification implementation

English translation is too difficult? I wrote two translation scripts with crawler in a rage

What is the difference between TCP and UDP?

The configuration that needs to be modified when switching between high and low versions of MySQL 5-8 (take aicode as an example here)

[SUCTF 2019]Game

pytest+allure+jenkins環境--填坑完畢

What are the positions of communication equipment manufacturers?

Redis data migration

Iterable、Collection、List 的常见方法签名以及含义