当前位置:网站首页>FPGA learning notes: vivado 2019.1 add IP MicroBlaze

FPGA learning notes: vivado 2019.1 add IP MicroBlaze

2022-07-05 13:18:00 【Zhangshizheng】

Preface

At present FPGA omnipotent , Can add MCU The core of , That is, it can be embedded in the core of a single chip microcomputer , When a single-chip computer is used , Add here

MicroBlaze, This is RISC The core of , Not familiar yet , Estimate and ARM perhaps RISC-V This level of kernel architecture is similarDevelopment board :【 The punctual atoms 】 Vinci Pro FPGA Development board ,FPGA The model of the chip is :

XilinxOfxc7a35tfgg484-2IDE :

XilinxOfVivado 2019.1

add to 【MicroBlaze】

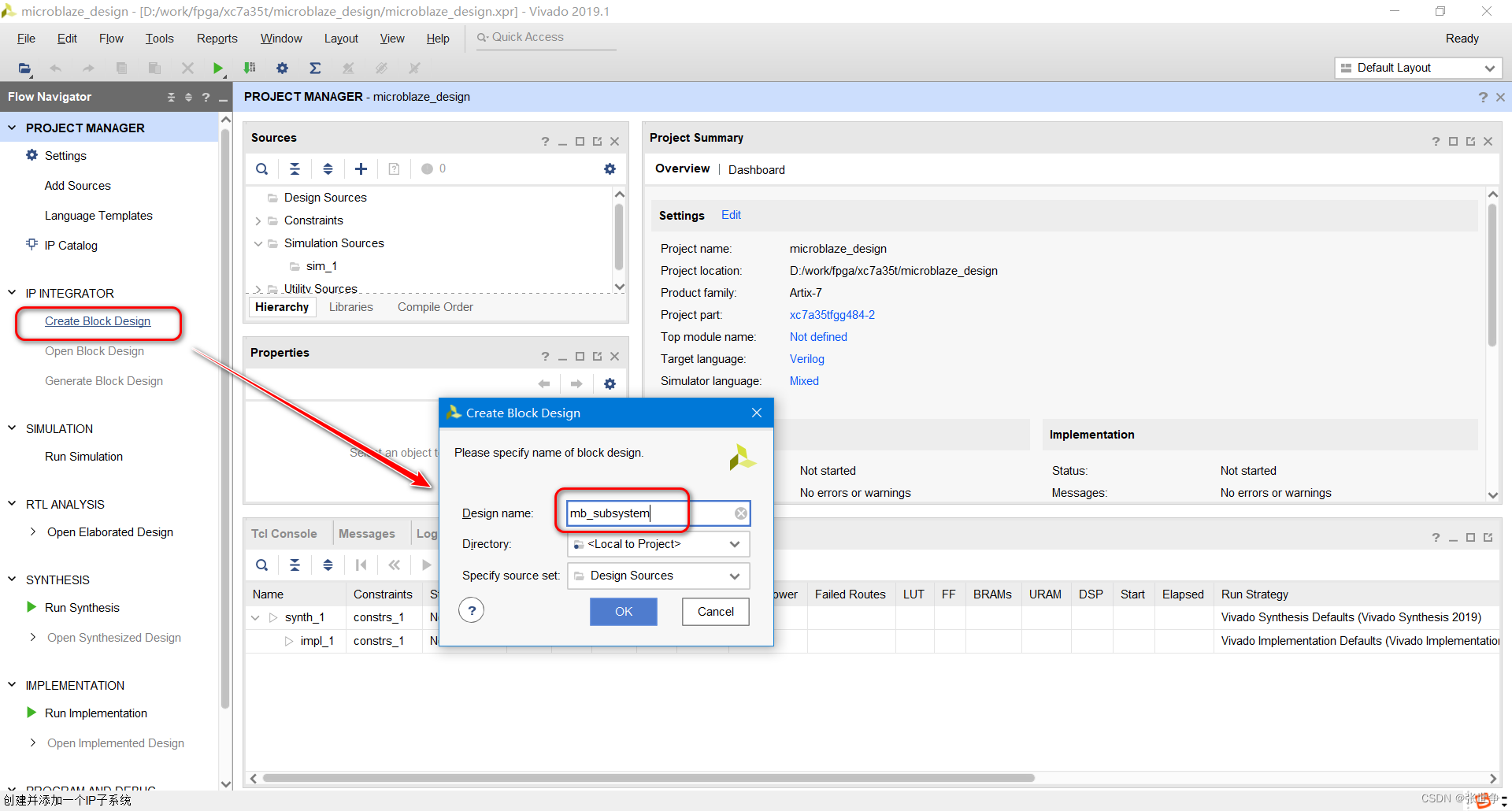

MicroBlazeIP The addition of , I followXilinxOfficial video operation , Take a study note here , Just want to know about this embedded in FPGA Medium MCU kernel , How to develop and useestablish Vivado After empty project , Click on 【IP INTEGRATOR】 Under the 【Create Block Design】, in other words , MicroBlaze As a IP Nuclear way to join the project

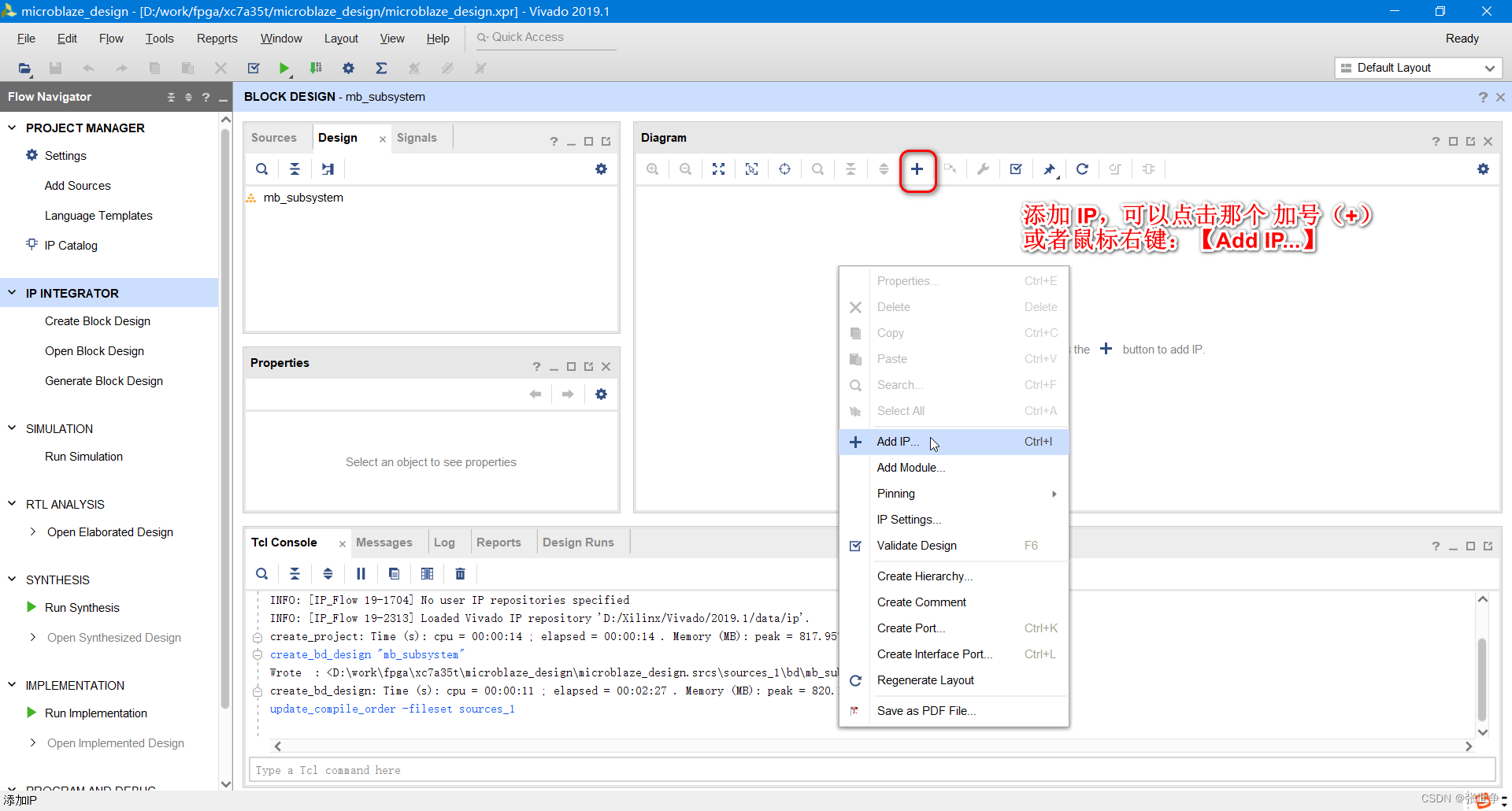

- stay 【Diagram】 window , Click on the right 【Add IP…】, Or click on the window toolbar 【+】, add to IP nucleus

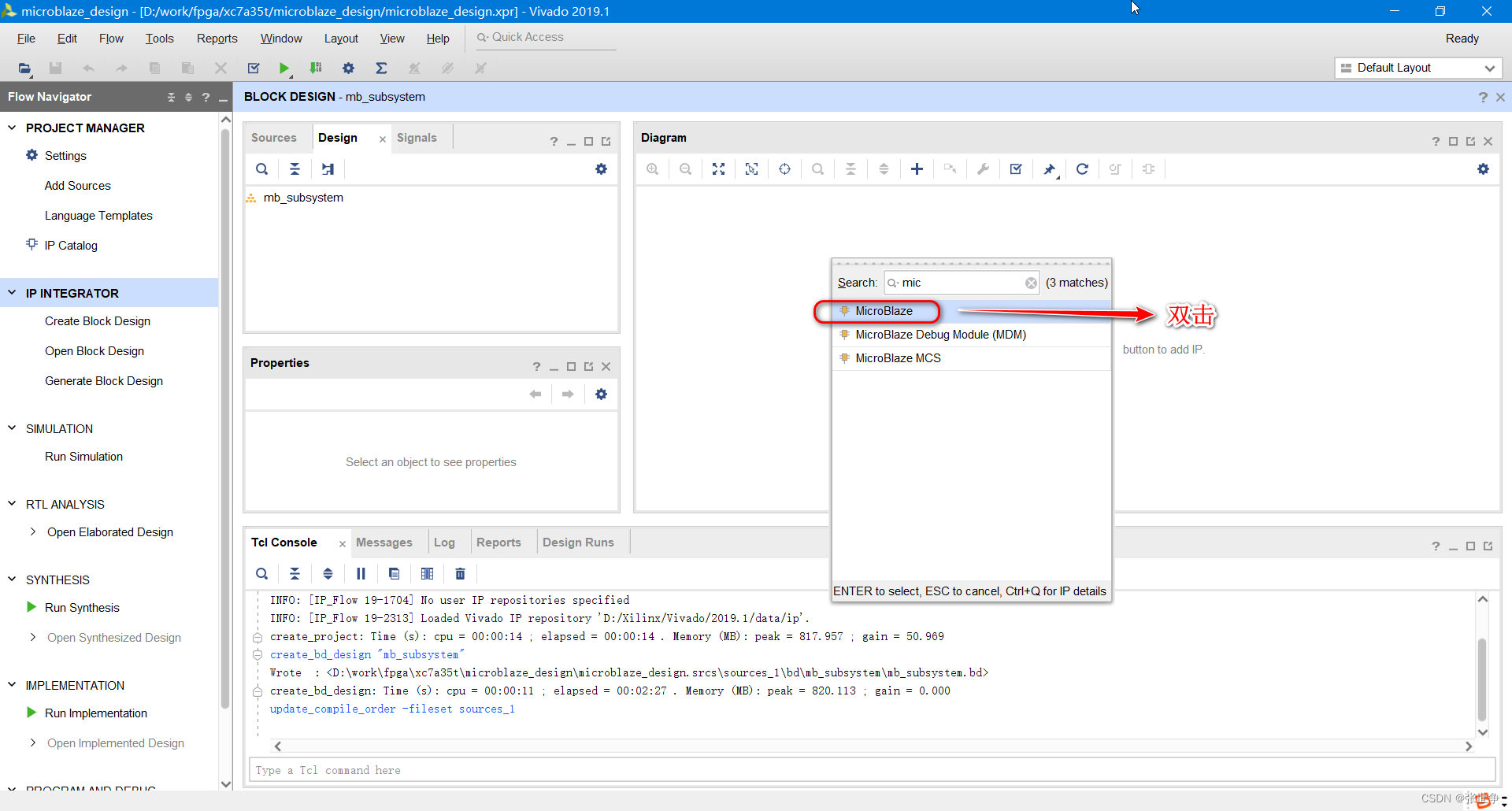

- Xilinx Of IP Many nuclei , You can enter MicroBlaze , select 【MicroBlaze】, Double click the mouse after selecting

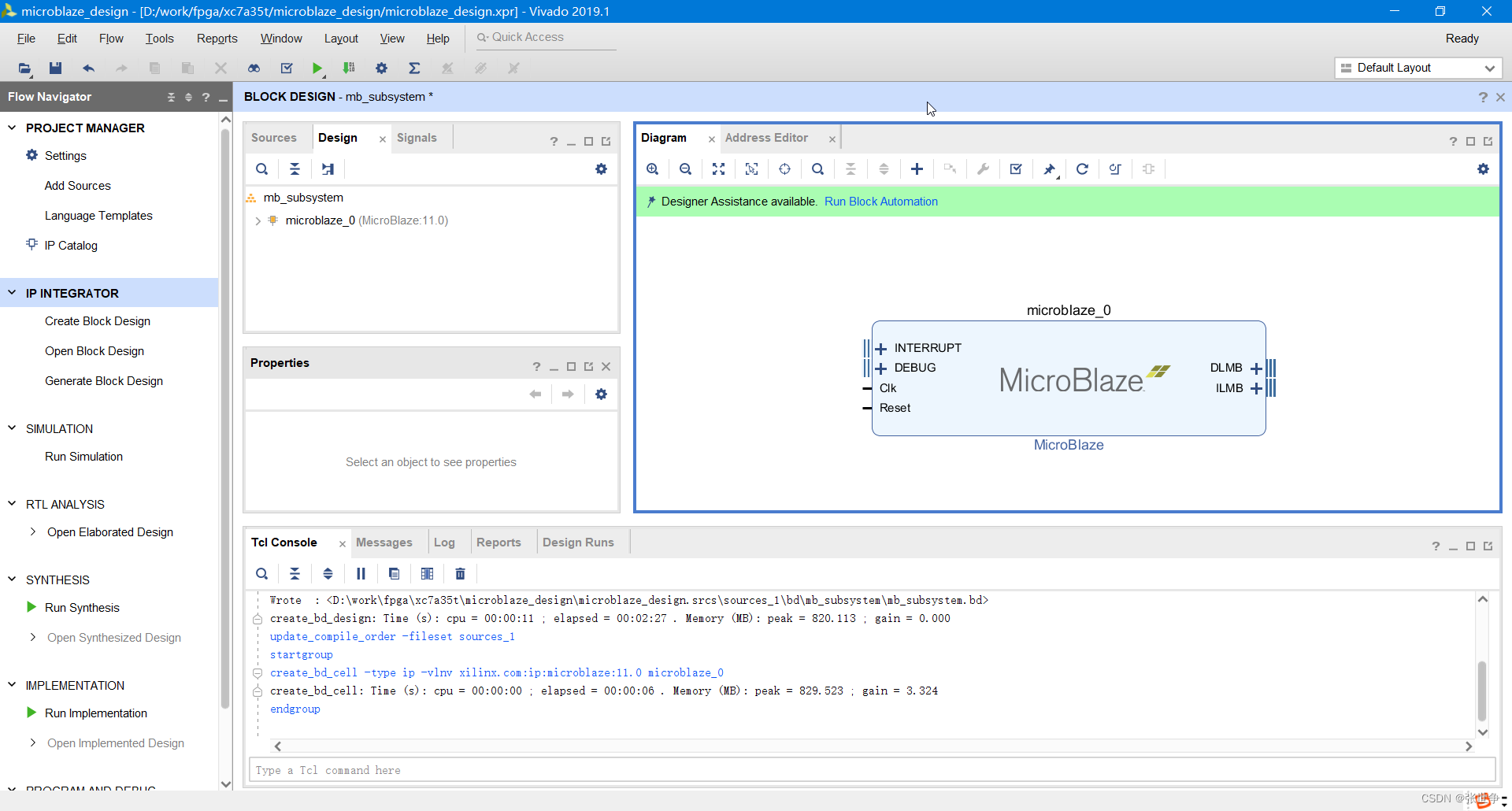

- add to MicroBlaze IP The interface behind the core , You need to add others 【 peripherals 】, Such as reset Pin Serial port and so on

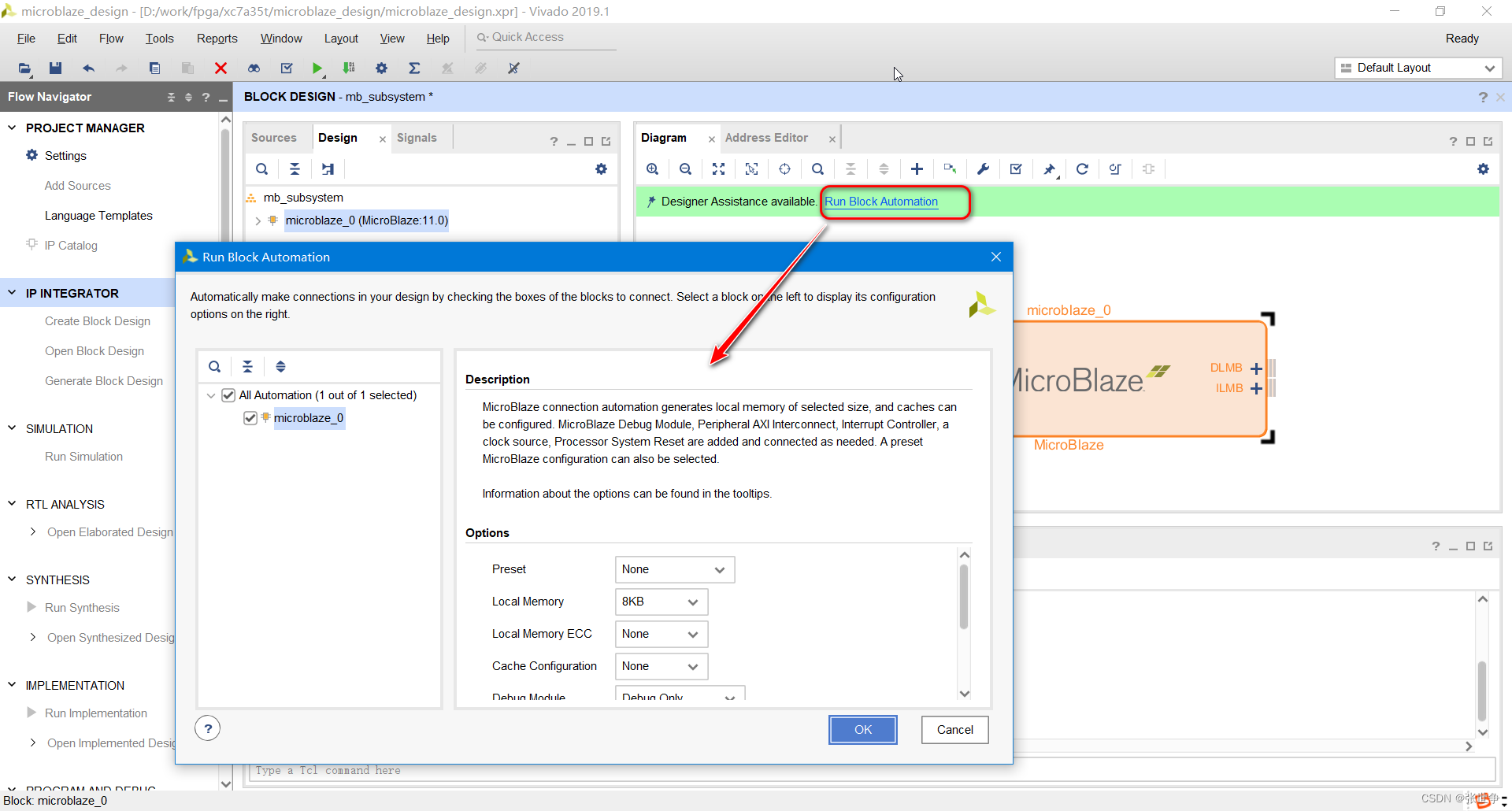

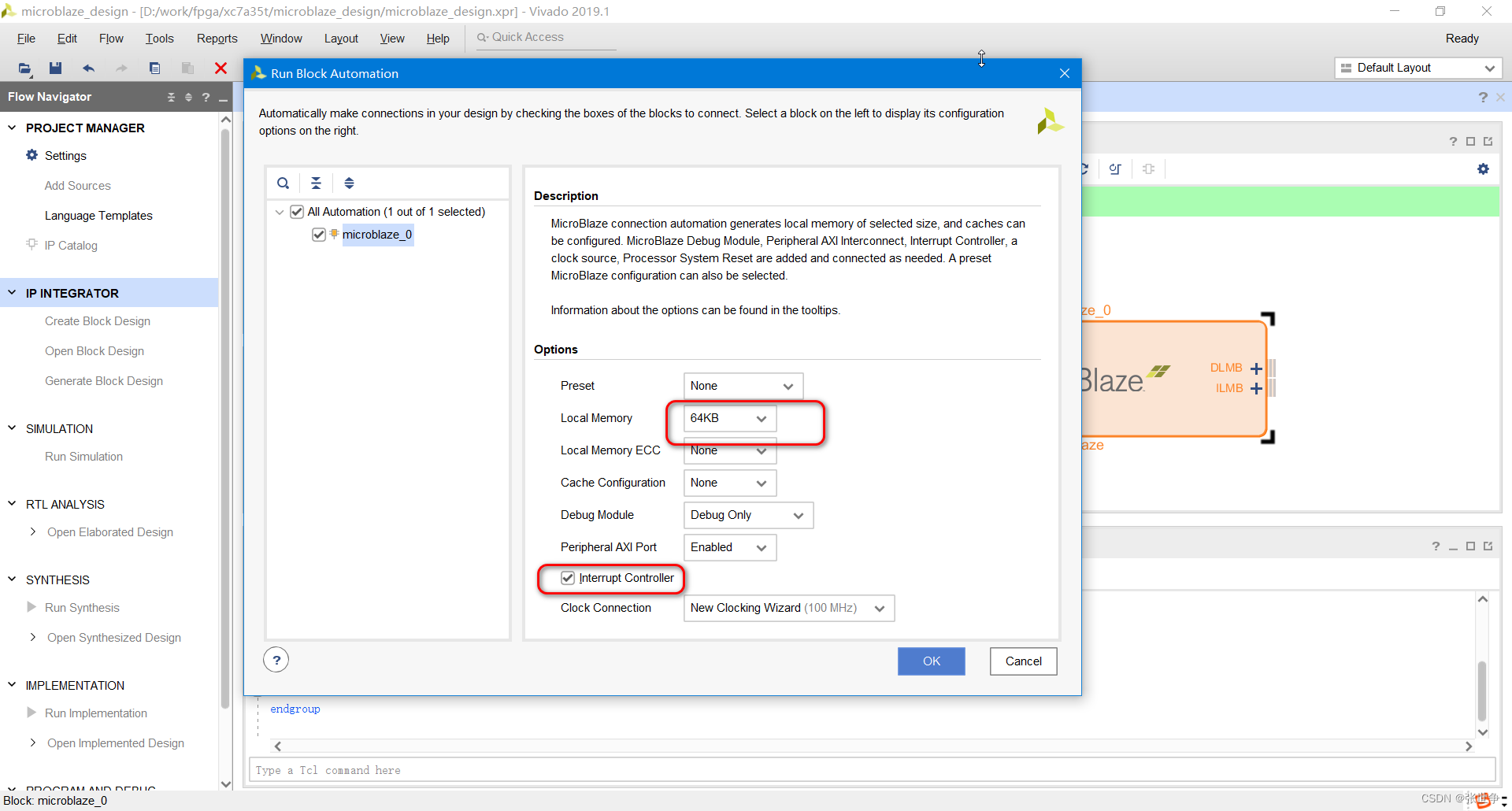

- Click on above 【Run Block Automation】

- here You can simply modify the configuration of the kernel , Such as RAM size , And so on

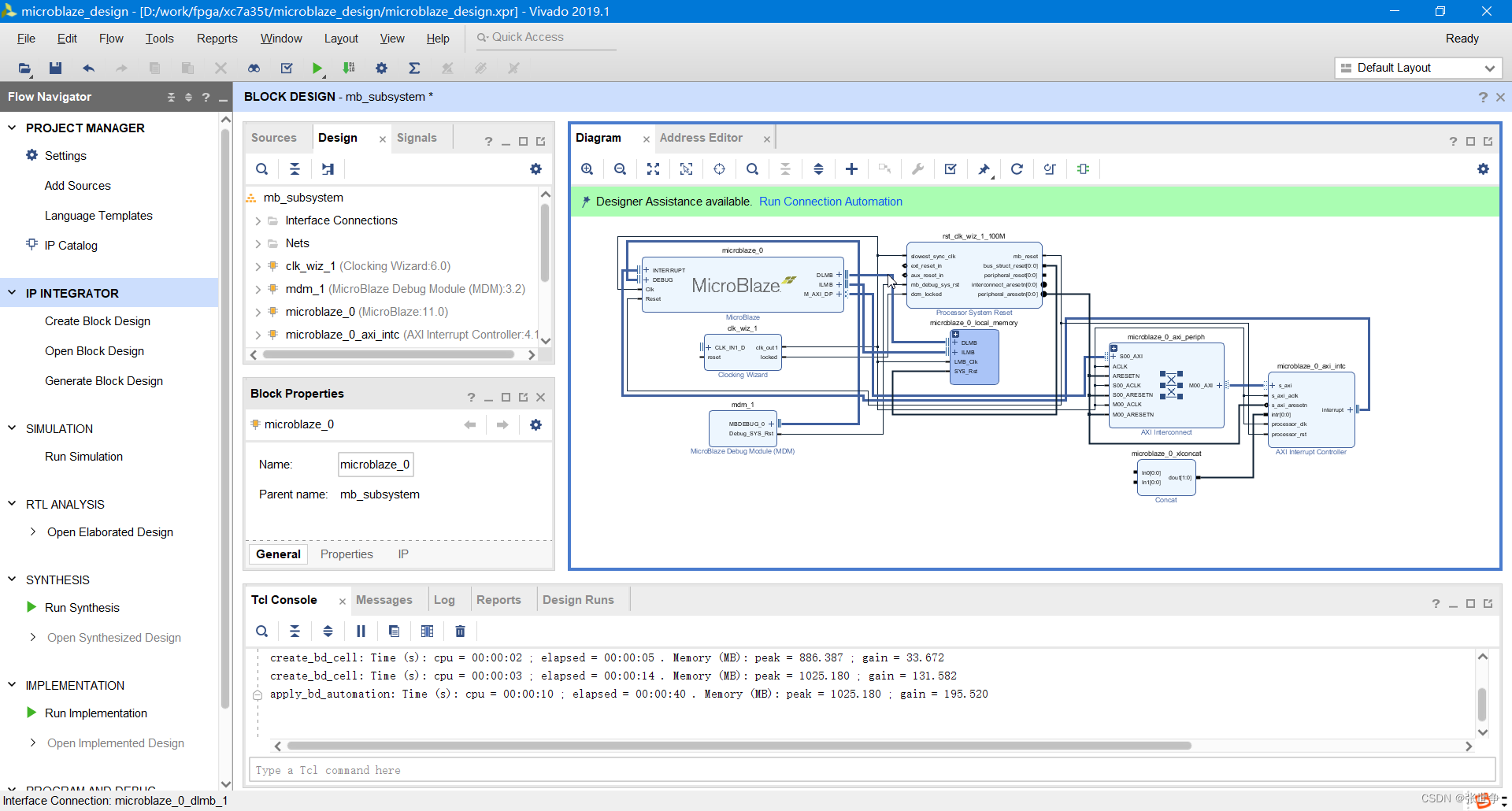

- 【Run Block Automation】 after , I found that something was added

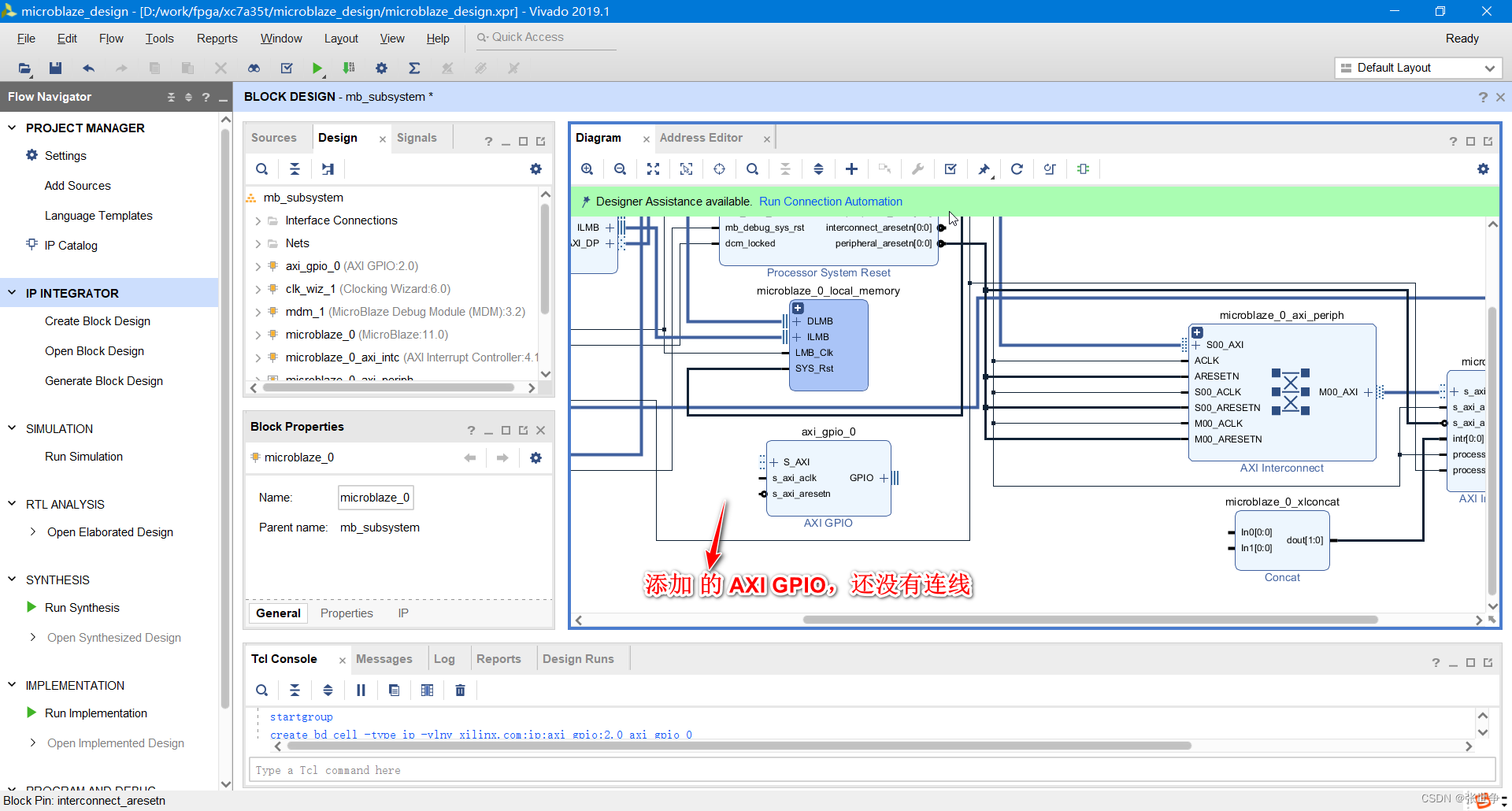

add to GPIO peripherals

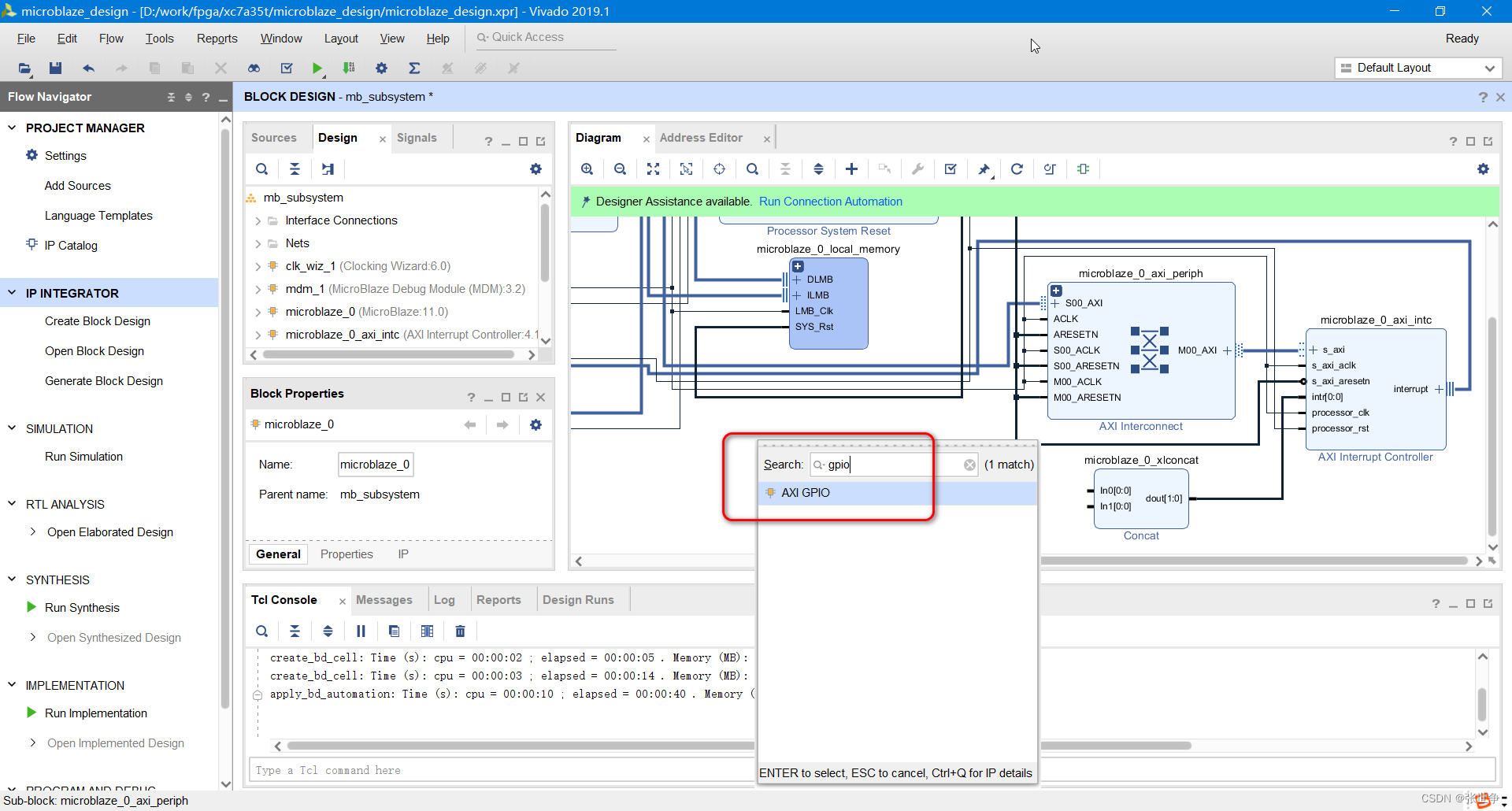

- The single chip microcomputer must have a pin control ,gpio It's also a IP nucleus , Add method and add to 【MicroBlaze】 The method is the same , choice 【AXI GPIO】

- add to 【AXI GPIO】 After the effect of , By default, there is no connection with 【MicroBlaze】 Connect

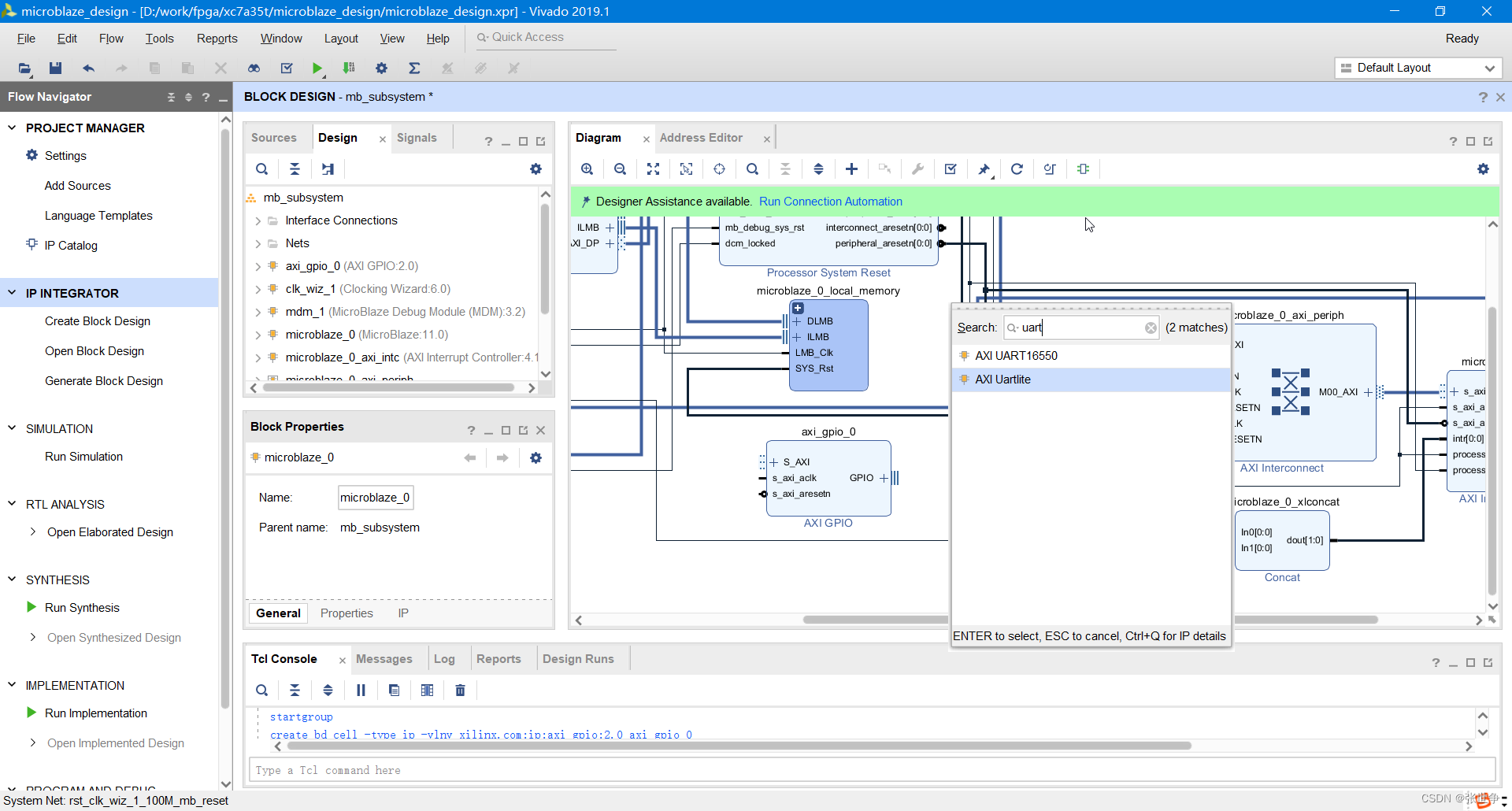

add to UART A serial port IP Core is used for serial port printout

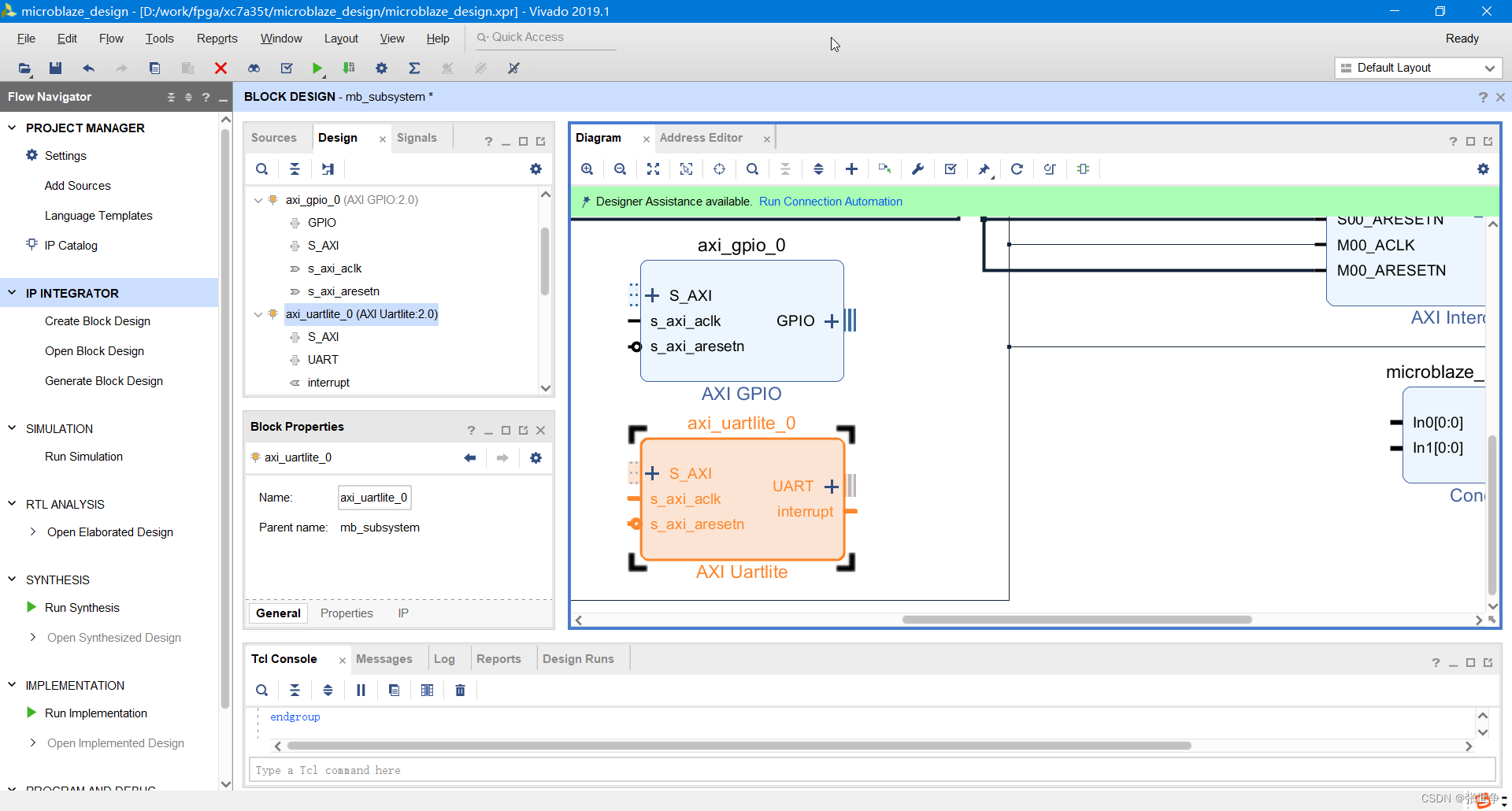

- Add method and add GPIO equally , Add here 【AXI Uartlite】

add to 【AXI Uartlite】 IP After the core , Still independent , With no 【MicroBlaze】 Connect

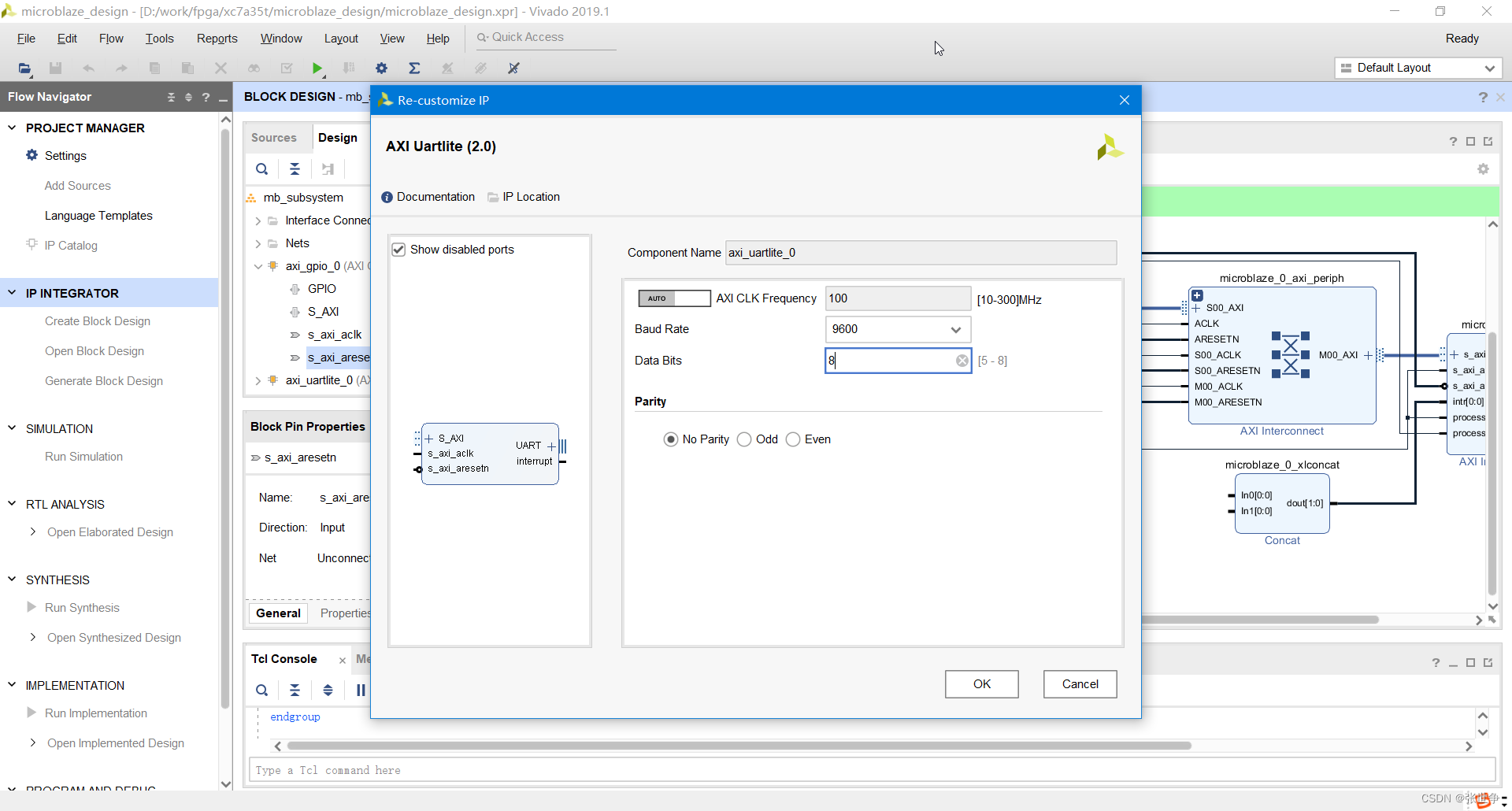

Double click on the added 【AXI Uartlite】 example , You can see uart Default properties of serial port

Summary

This paper studies how to add 【MicroBlaze】、【AXI GPIO】、【AXI Uartlite】FPGA IP Nuclear Methods

Later, we will continue to study how to integrate the above IP nucleus , Connect , Form a Embedded MCU

Keep learning 【MicroBlaze】 Development and use methods of

边栏推荐

- 蜀天梦图×微言科技丨达梦图数据库朋友圈+1

- Talk about seven ways to realize asynchronous programming

- Laravel document reading notes -mews/captcha use (verification code function)

- APICloud Studio3 WiFi真机同步和WiFi真机预览使用说明

- Reflection and imagination on the notation like tool

- 百度杯”CTF比赛 2017 二月场,Web:爆破-2

- 百日完成国产数据库opengausss的开源任务--openGuass极简版3.0.0安装教程

- OpenHarmony应用开发之Navigation组件详解

- Navigation property and entityset usage in SAP segw transaction code

- FPGA 学习笔记:Vivado 2019.1 添加 IP MicroBlaze

猜你喜欢

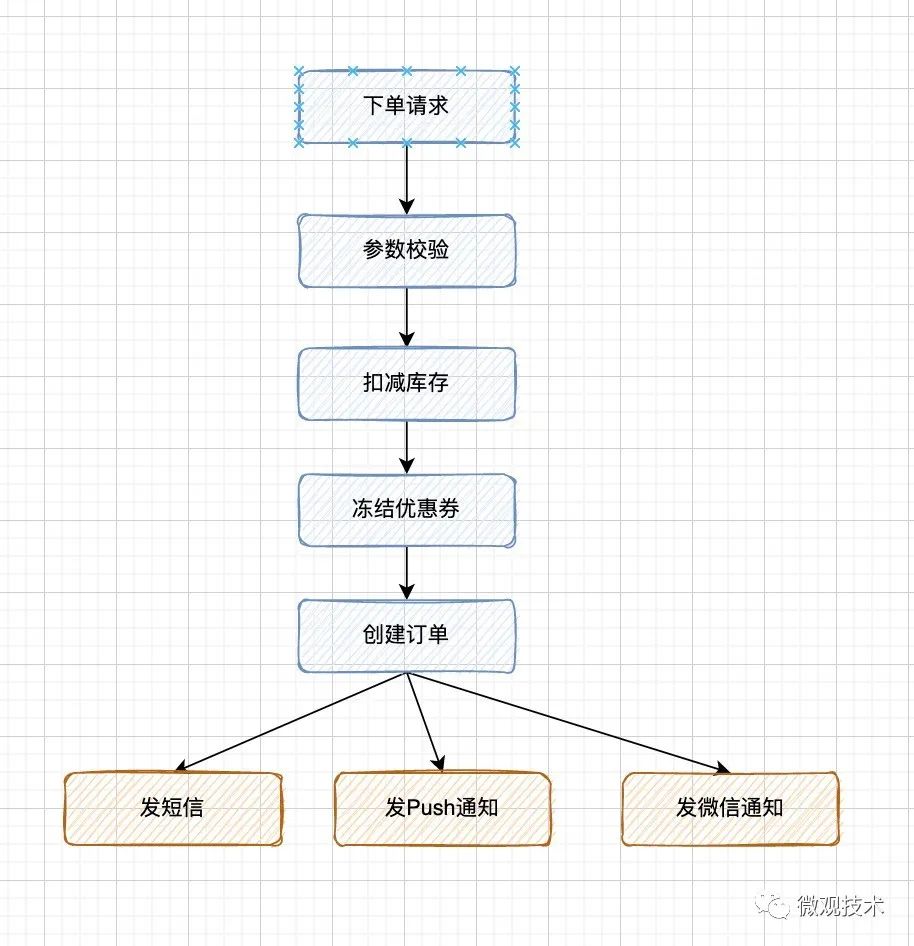

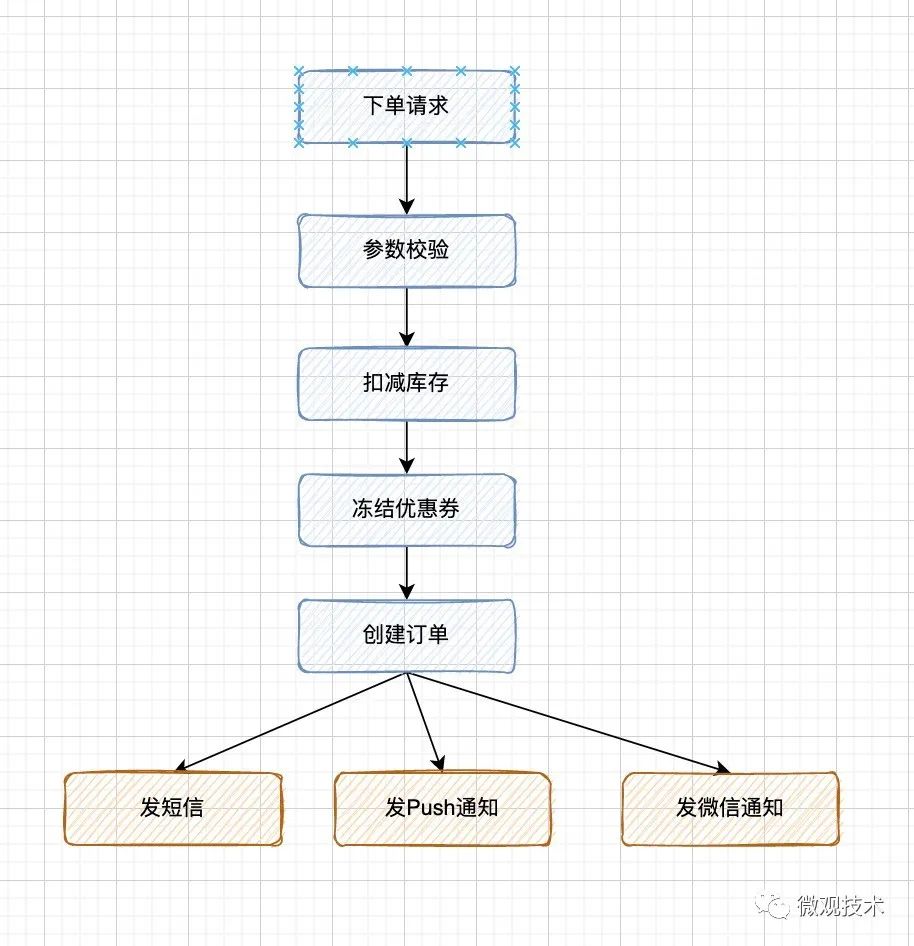

Talk about seven ways to realize asynchronous programming

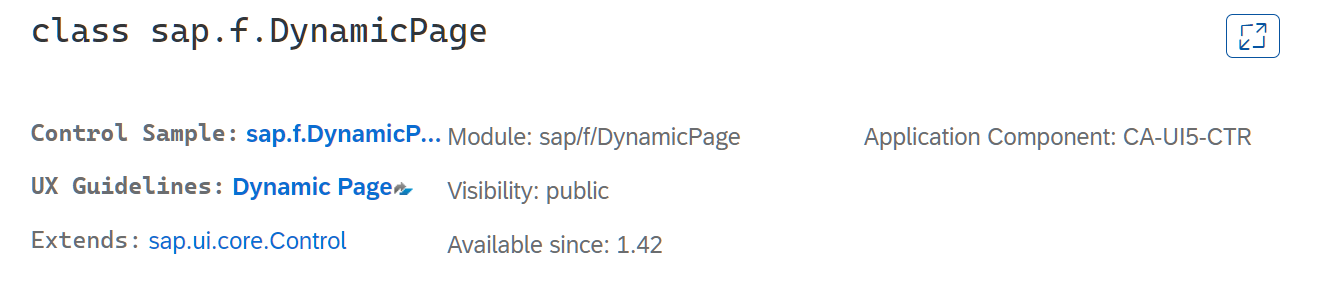

Introduction to sap ui5 dynamicpage control

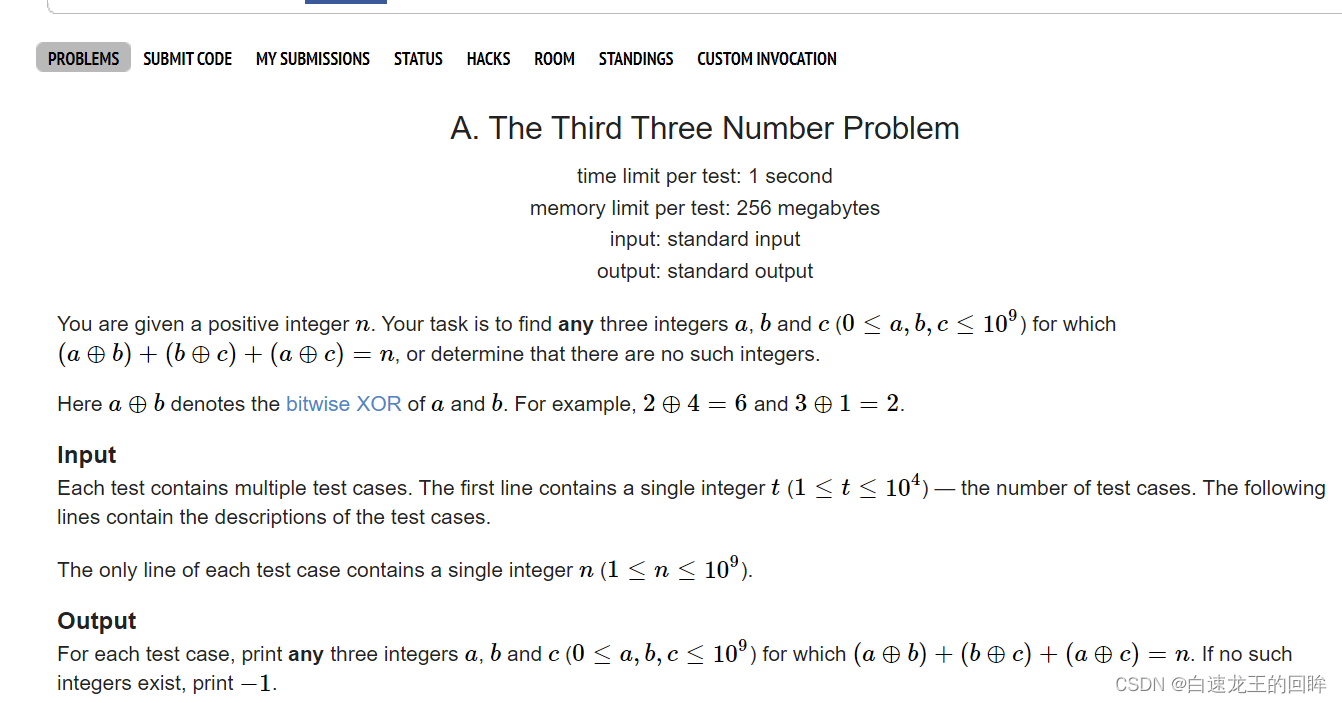

CF:A. The Third Three Number Problem【关于我是位运算垃圾这个事情】

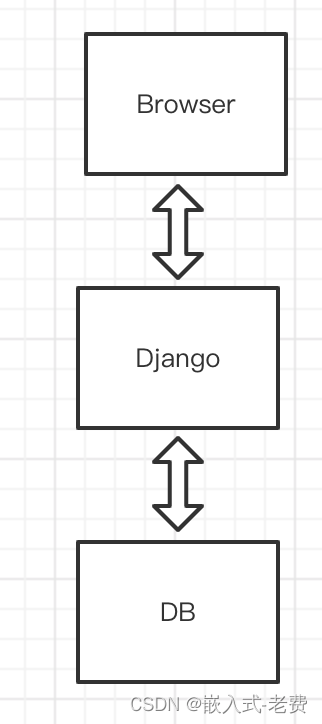

STM32 and motor development (from architecture diagram to documentation)

![leetcode:221. Maximum square [essence of DP state transition]](/img/ea/158e8659657984794c52a0449e0ee5.png)

leetcode:221. Maximum square [essence of DP state transition]

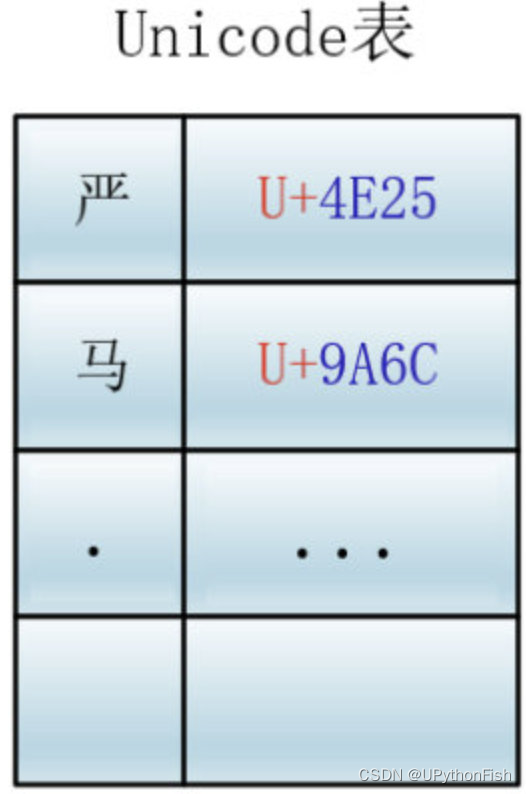

A detailed explanation of ASCII code, Unicode and UTF-8

![[深度学习论文笔记]使用多模态MR成像分割脑肿瘤的HNF-Netv2](/img/52/5e85743b1817de96a52e02b92fd08c.png)

[深度学习论文笔记]使用多模态MR成像分割脑肿瘤的HNF-Netv2

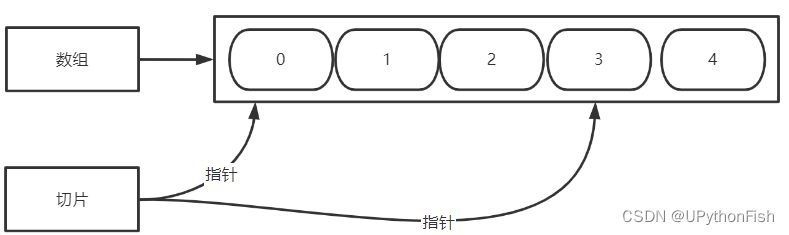

go 数组与切片

聊聊异步编程的 7 种实现方式

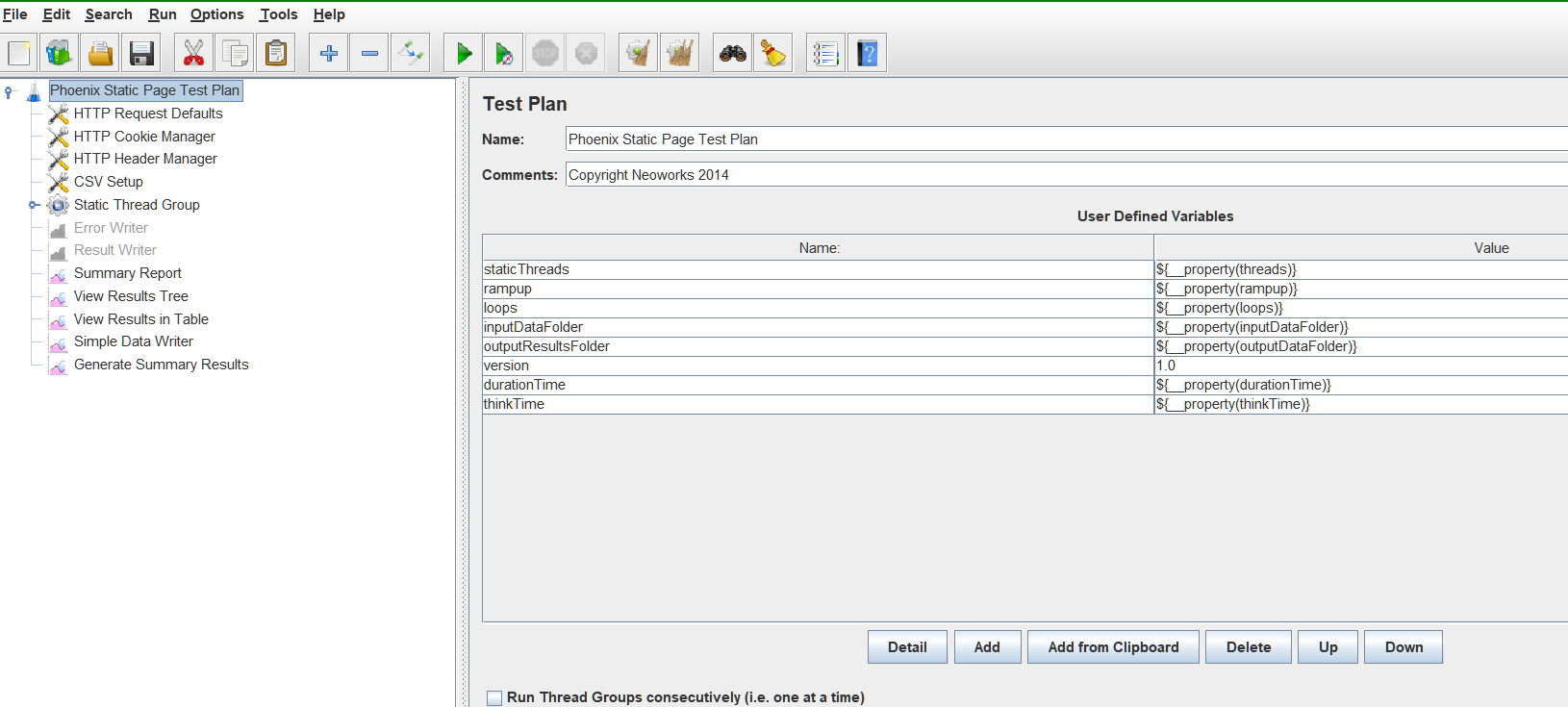

Concurrent performance test of SAP Spartacus with JMeter

随机推荐

阿里云SLB负载均衡产品基本概念与购买流程

Laravel document reading notes -mews/captcha use (verification code function)

MSTP and eth trunk

js判断数组中是否存在某个元素(四种方法)

Detailed explanation of navigation component of openharmony application development

AVC1与H264的区别

Introduction to sap ui5 flexiblecolumnlayout control

APICloud Studio3 API管理与调试使用教程

Go string operation

Natural language processing series (I) introduction overview

Lb10s-asemi rectifier bridge lb10s

蜀天梦图×微言科技丨达梦图数据库朋友圈+1

Word document injection (tracking word documents) incomplete

Go pointer

【Hot100】34. Find the first and last positions of elements in a sorted array

Fragmented knowledge management tool memos

Developers, is cloud native database the future?

Get to know linkerd project for the first time

Write macro with word

Flutter 绘制波浪移动动画效果,曲线和折线图