当前位置:网站首页>SPI master RX time out interrupt

SPI master RX time out interrupt

2022-07-07 15:56:00 【lixingdian】

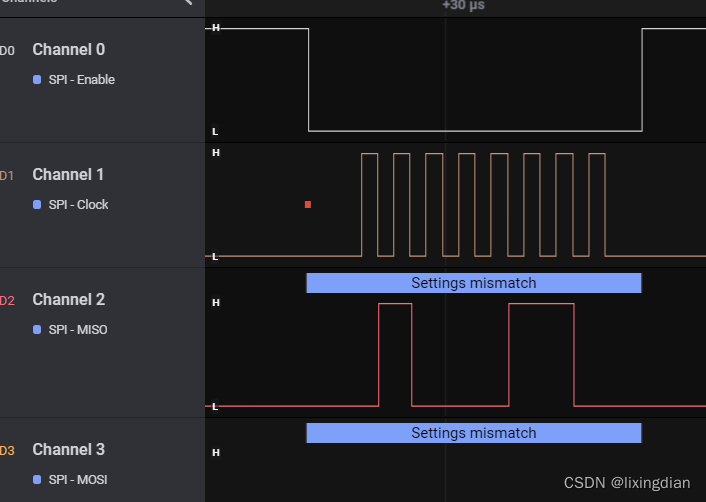

background : test spi Of time out interrupt , The board A master rx, The board B slave tx.master Set to timeout interrupt TIME OUT.

slave Send data ,master Timeout interrupt is not triggered . The image is very accurate , I began to worry that there was a problem with the function of the board , But the simulation is ok . It should be a setup problem .

The simulation told me , eliminate fifo Will clear time out register . So I cleared it once during initialization , It will not be cleared later flfo. But in fact, such waveforms are not correct , Is it slave How to send data to master. And still can't trigger interrupt , If I set it to done Interrupt can trigger . But it's not what we want time out It's broken . The simulation told me again rx trigger level It's empty , Setting data will trigger , It is also invalid after setting , Later, it was found that this bit has a numerical limit , Not too big , Turn into 0. Setting to the correct number will not trigger the interrupt . The simulation tells me again , When transmitting data, there is a lot of data to receive ,cs Keep pulling down , It will cause the board to think that it is still receiving data , Will trigger rxready interrupt , instead of time out interrupt . The reason why we need to receive a lot of data , It's because of my master Set up SPI_DataLen by 512(bits) 了 . Explain in the document :

Tx/Rx length

Spi During transmission , Effective SCK Count

It also indirectly reflects the length of data sent or received .

So when I set up datalen by 8 in the future , Can trigger normal TIME OUT It's broken .

Later on time out Interrupted document , I found that I didn't read the document in detail . In fact, the author writes very clearly .

When a transmission ends ,rx fifo There's data in , But the amount of data is not enough to trigger rx trigger level when , Over a certain period of time , It will trigger time out register . If it's cleared fifo It will definitely clear the tone time out Counter .

So to test time out, need

1、 The interval between sending data is long , Long enough to trigger after receiving data TIME OUT Then clear away fifo.

2、 The amount of data is less than rx trigger level, And will not trigger too much rx ready interrupt .

Welcome to my WeChat official account.

边栏推荐

- postman生成时间戳,未来时间戳

- Getting started with webgl (2)

- Function: JS Click to copy content function

- What is Base64?

- Three. Introduction to JS learning notes 17: mouse control of 3D model rotation of JSON file

- Annexb and avcc are two methods of data segmentation in decoding

- 融云斩获 2022 中国信创数字化办公门户卓越产品奖!

- Write sequence frame animation with shader

- Getting started with webgl (4)

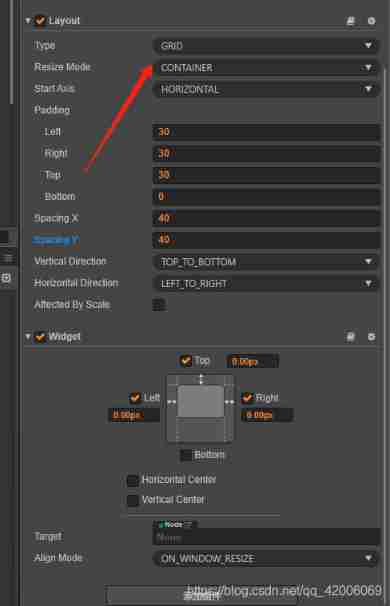

- The rebound problem of using Scrollview in cocos Creator

猜你喜欢

Syntax of generator function (state machine)

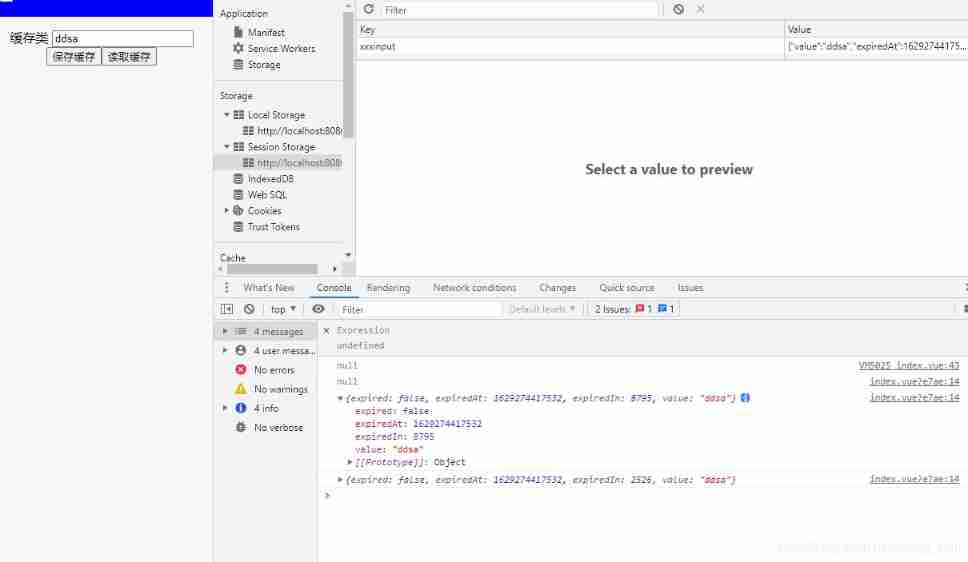

TS as a general cache method

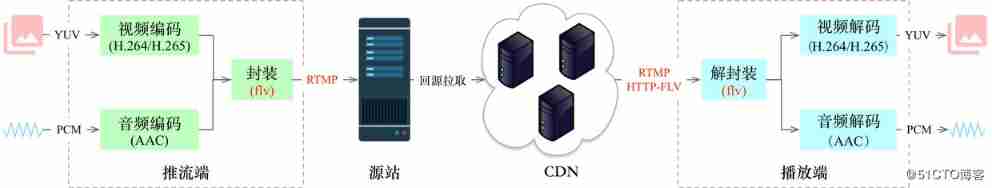

Streaming end, server end, player end

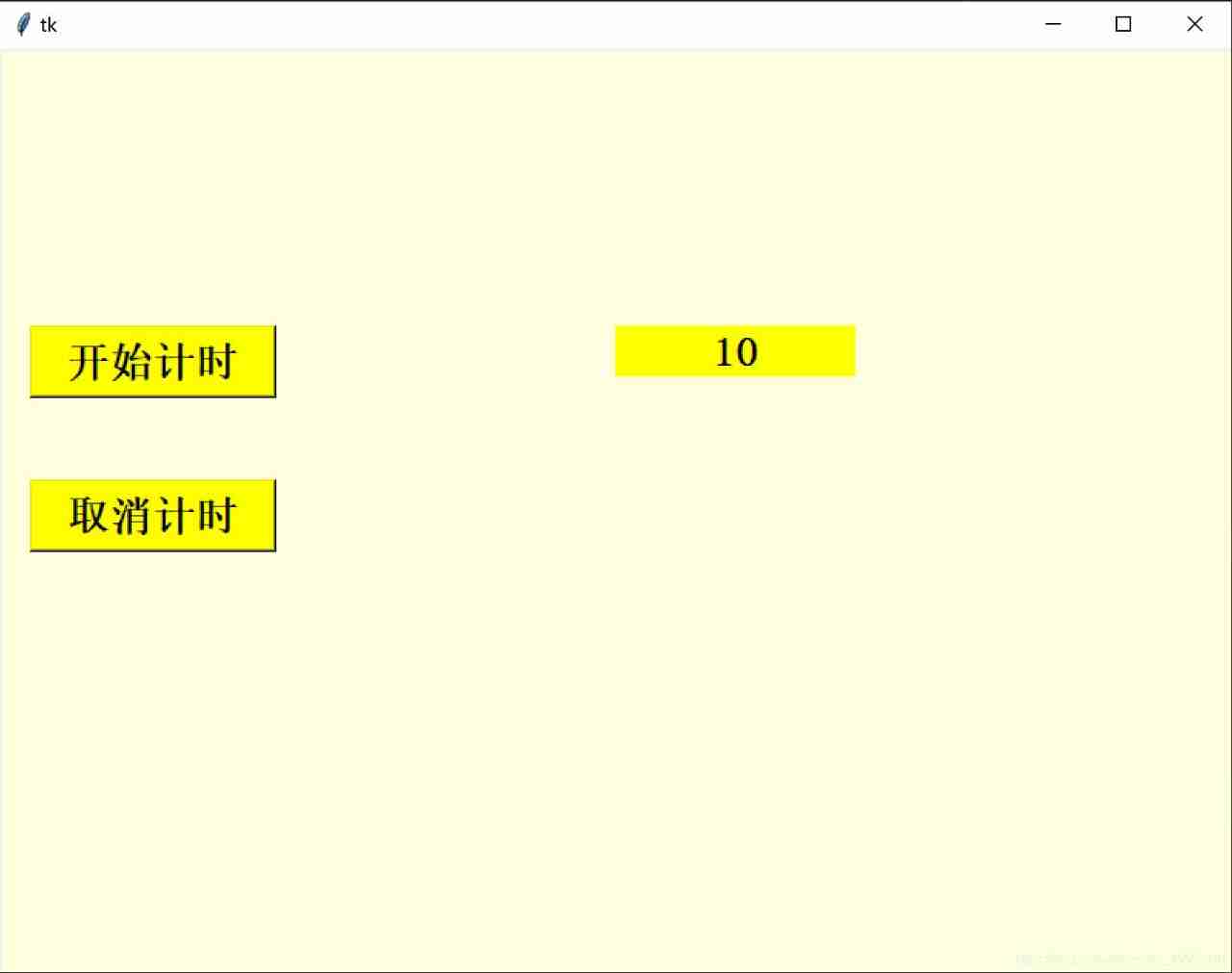

Tkinter after how to refresh data and cancel refreshing

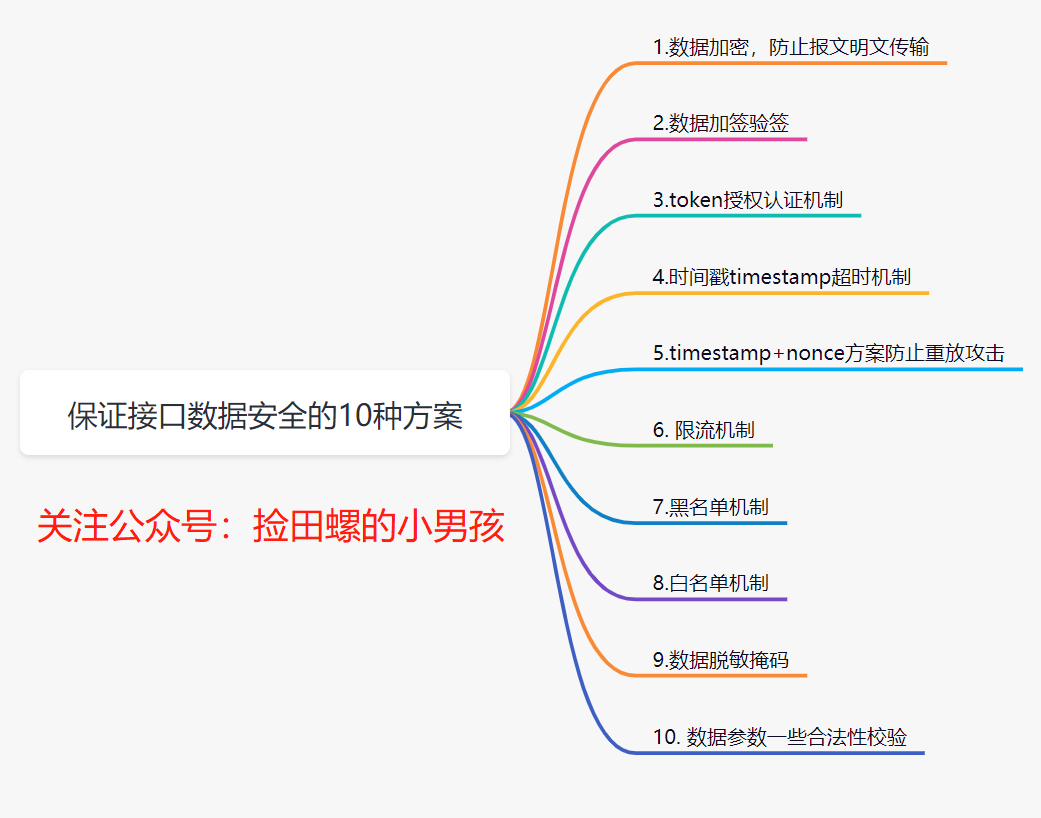

10 schemes to ensure interface data security

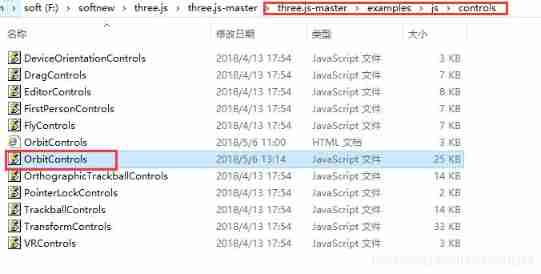

Three. JS introductory learning notes 08:orbitcontrols JS plug-in - mouse control model rotation, zoom in, zoom out, translation, etc

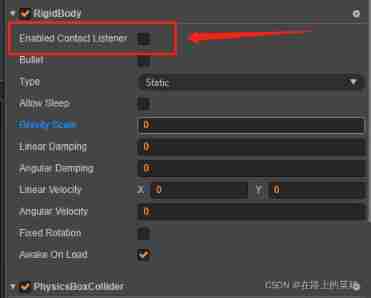

Cocos creator collision and collision callback do not take effect

The bank needs to build the middle office capability of the intelligent customer service module to drive the upgrade of the whole scene intelligent customer service

The rebound problem of using Scrollview in cocos Creator

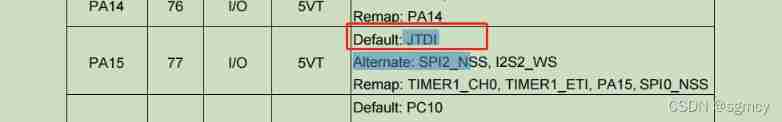

Gd32 F3 pin mapping problem SW interface cannot be burned

随机推荐

[quick start of Digital IC Verification] 19. Basic grammar of SystemVerilog learning 6 (thread internal communication... Including practical exercises)

Numpy --- basic learning notes

航运船公司人工智能AI产品成熟化标准化规模应用,全球港航人工智能/集装箱人工智能领军者CIMC中集飞瞳,打造国际航运智能化标杆

How to create Apple Developer personal account P8 certificate

安科瑞电网智能化发展的必然趋势电力系统采用微机保护装置是

C4D learning notes 2- animation - timeline and time function

【微信小程序】Chapter(5):微信小程序基础API接口

There are many ways to realize the pause function in JS

[Lanzhou University] information sharing of postgraduate entrance examination and re examination

C4D learning notes 3- animation - animation rendering process case

leetcode 241. Different ways to add parentheses design priority for operational expressions (medium)

Webcodecs parameter settings -avc1.42e01e meaning

unnamed prototyped parameters not allowed when body is present

Clang compile link ffmpeg FAQ

OpenGL common functions

postman生成时间戳,未来时间戳

【花雕体验】15 尝试搭建Beetle ESP32 C3之Arduino开发环境

nodejs package. JSON version number ^ and~

How to deploy the super signature distribution platform system?

Migration and reprint