当前位置:网站首页>复杂网络建模(三)

复杂网络建模(三)

2022-07-07 04:58:00 【坝坝头伯爵】

度中心性

度中心性分为节点度中心性和网络度中心性。前者指的是节点在其与之直接相连的邻居节点当中的中心程度,而后者则是侧重节点在整个网络的中心程度,表征的是整个网络的集中程度。

节点Vi的度中心性CD(Vi)定义为

C D ( V i ) = k i / ( N − 1 ) C_D(V_i)=k_i/(N-1) CD(Vi)=ki/(N−1)

介数中心性

介数中心性分别为节点介数中心性和网络介数中心性。

节点Vi的介数中心性CB(Vi)定义为

C B ( V i ) = 2 B i / [ ( N − 2 ) ( N − 1 ) ] C_B(V_i)=2B_i/[(N-2)(N-1)] CB(Vi)=2Bi/[(N−2)(N−1)]

接近度中心性

对于连通图来说,节点Vi的接近度中心性Cc(Vi)定义为

C c ( v i ) = ( N − 1 ) / [ ∑ j = 1 , j ≠ i N d i j ] C_c(v_i)=(N-1)/[\sum_{j=1,j\neq i}^{N}d_{ij}] Cc(vi)=(N−1)/[j=1,j=i∑Ndij]

特征向量中心性

根据网络的邻接矩阵而定义

A x = λ x Ax=\lambda x Ax=λx

只有最大的特征值对应的特征向量才是中心性测度所需要的。在得到的特征向量中,第i个分量xi就是节点Vi的特征向量中心性CE(Vi)。

有向网络的静态特征

1.入度和出度

由于与有向网络某个节点相关联的弧有指向节点的,也有背向节点向外的,因此除了可以统计与某个节点相关联的弧数(也就是度),有必要分开统计两个方向的弧数,分别成为节点的入度和出度。

加权网络的静态特征

1.点权

节点vi的点权si定义为

S j = ∑ j ∈ N i w i j S_j=\sum_{j\in N_i}^{}w_{ij} Sj=j∈Ni∑wij

式中,Ni表示节点Vi的邻点集合,wij表示连接节点vi和节点vj的边的权重。

2.单位权

节点vi的单位权Ui定义为Ui=Si/ki

3.基于节点的权-度的相关性

基于节点的权-度相关性指的是对于单个节点来说,其点权与其度之间的相关性

s ˉ ( k ) = ( ∑ i : k i = k s i ) / [ N ⋅ P ( k ) ] \bar{s}(k)=(\sum_{i:k_i=k}s_i)/[N\cdot P(k)] sˉ(k)=(i:ki=k∑si)/[N⋅P(k)]

4.权重分布差异性

节点Vi的权重分布差异性Yi表示与节点Vi相连的边权分布的离散程度,定义为

Y i = ∑ j ∈ N i ( w i j / s i ) 2 Y_i=\sum_{j\in N_i}(w_{ij}/s_i)^{2} Yi=j∈Ni∑(wij/si)2

差异性与度有如下关系:如果与节点Vi关联的边权重差异不大,则Yi正比于1/ki,如果权重差别比较大,则Yi约等于1

边栏推荐

- Linux server development, redis source code storage principle and data model

- Leetcode 43 String multiplication (2022.02.12)

- Problem solving: unable to connect to redis

- [UVM practice] Chapter 1: configuring the UVM environment (taking VCs as an example), run through the examples in the book

- Network learning (I) -- basic model learning

- PHP exports millions of data

- CTF daily question day43 rsa5

- LeetCode简单题之找到一个数字的 K 美丽值

- Paddlepaddle 29 dynamically modify the network structure without model definition code (relu changes to prelu, conv2d changes to conv3d, 2D semantic segmentation model changes to 3D semantic segmentat

- 2022 Inner Mongolia latest advanced fire facility operator simulation examination question bank and answers

猜你喜欢

海信电视开启开发者模式

2022茶艺师(初级)考试题模拟考试题库及在线模拟考试

2022焊工(初级)判断题及在线模拟考试

青龙面板-今日头条

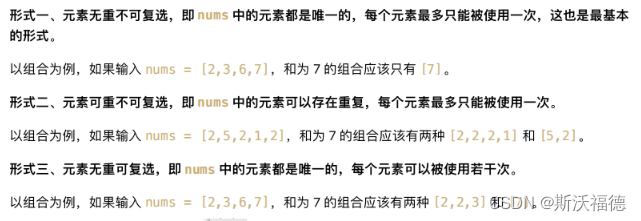

Leetcode 40: combined sum II

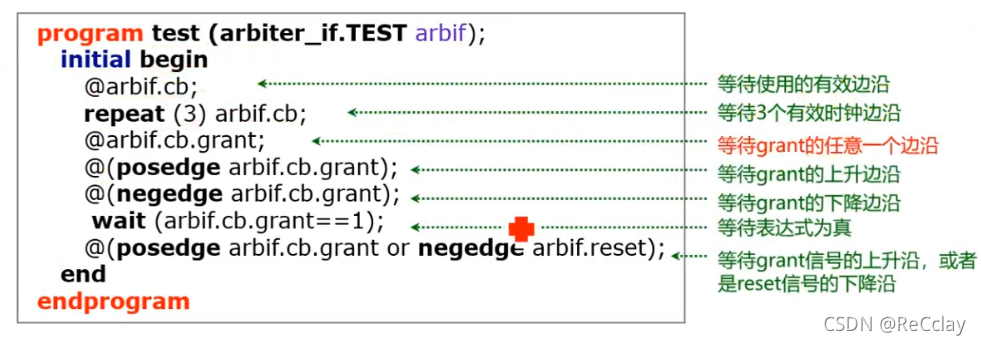

【数字IC验证快速入门】13、SystemVerilog interface 和 program 学习

LeetCode简单题之字符串中最大的 3 位相同数字

Sign up now | oar hacker marathon phase III, waiting for your challenge

Linux server development, MySQL index principle and optimization

2022 recurrent training question bank and answers of refrigeration and air conditioning equipment operation

随机推荐

[Matlab] Simulink 自定义函数中的矩阵乘法工作不正常时可以使用模块库中的矩阵乘法模块代替

Zsh shell adds automatic completion and syntax highlighting

Codeforces Global Round 19

QT learning 26 integrated example of layout management

Installing postgresql11 database under centos7

【数字IC验证快速入门】11、Verilog TestBench(VTB)入门

让Livelink初始Pose与动捕演员一致

Pytest + allure + Jenkins Environment - - achèvement du remplissage de la fosse

2022 welder (elementary) judgment questions and online simulation examination

LeetCode 90:子集 II

Empire CMS collection Empire template program general

MySQL multi column index (composite index) features and usage scenarios

Info | webrtc M97 update

芯片资料 网站 易特创芯

[UVM practice] Chapter 2: a simple UVM verification platform (2) only driver verification platform

OpenJudge NOI 2.1 1752:鸡兔同笼

Thinkcmf6.0安装教程

Ansible

Recursive construction of maximum binary tree

【踩坑系列】uniapp之h5 跨域的问题