当前位置:网站首页>Verilog realizes the calculation of the maximum common divisor and the minimum common multiple

Verilog realizes the calculation of the maximum common divisor and the minimum common multiple

2022-07-05 15:41:00 【Don't want to have PE class】

Design a sequential circuit , Input 2 An unsigned number , The bit width can be determined by the parameter DATA_W determine , Output the minimum common multiple and maximum common divisor of these two numbers .

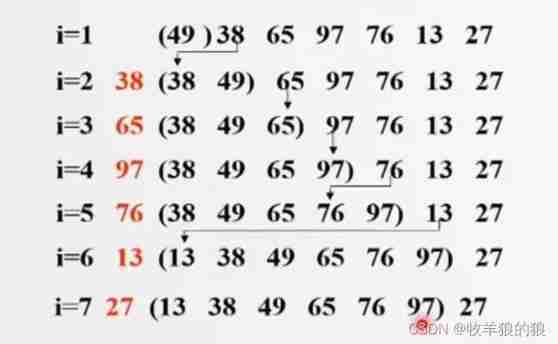

Explain : When solving the greatest common divisor and the least common multiple , The greatest common divisor is usually calculated by rolling division , Then divide the greatest common divisor by the product of two numbers to get the least common multiple ;

Examples are as follows :

34 And 20;

(1)34 - 20 = 14;

(2)20 - 14 = 6;

(3)14 - 6 = 8;

(4)8 - 6 =2;

(5)6 - 2 = 4;

(6)4 - 2 = 2;

(7)2 - 2 = 0;

So the greatest common divisor is 2;

Then the least common multiple = 34 * 20 /2 =340;

The implementation code is as follows :

`timescale 1ns/1ns

module lcm#(

parameter DATA_W = 8)

(

input [DATA_W-1:0] A,

input [DATA_W-1:0] B,

input vld_in,

input rst_n,

input clk,

output wire [DATA_W*2-1:0] lcm_out,

output wire [DATA_W-1:0] mcd_out,

output reg vld_out

);

reg [DATA_W-1:0] A_reg;

reg [DATA_W-1:0] B_reg;

reg [DATA_W*2-1:0] lcm ;

reg [DATA_W*2-1:0] lcm_reg;

reg [DATA_W-1:0] mcd_reg;

reg [1:0] state;

parameter IDLE = 2'b00;

parameter st_1 = 2'b01;

parameter st_2 = 2'b10;

[email protected](posedge clk or negedge rst_n)

if(rst_n == 1'b0)

begin

vld_out<= 1'b0;

A_reg <= 'd0;

B_reg <= 'd0;

lcm <= 'd0;

mcd_reg <= 'd0;

lcm_reg <= 'd0;

state <= IDLE;

end

else case(state)

IDLE:

begin

vld_out <= 1'b0;

if(vld_in == 1'b1)

begin

A_reg <= A;

B_reg <= B;

lcm_reg<= A*B;

state <= st_1;

end

else

begin

A_reg <= A_reg;

B_reg <= B_reg;

lcm_reg<= lcm_reg;

state <= IDLE;

end

end

st_1:

if(A_reg == B_reg)

state <= st_2;

else

begin

state <= st_1;

if(A_reg > B_reg)

A_reg <= A_reg - B_reg;

else if(A_reg < B_reg)

B_reg <= B_reg - A_reg;

end

st_2:

begin

vld_out <= 1'b1;

lcm <= lcm_reg;

mcd_reg <= A_reg;

state <= IDLE;

end

endcase

assign lcm_out = lcm / mcd_reg;

assign mcd_out = mcd_reg;

endmoduleThe simulation code is as follows :

`timescale 1ns/1ns

module tb_lcm();

parameter DATA_W = 8;

reg [DATA_W-1:0] A;

reg [DATA_W-1:0] B;

reg vld_in;

reg rst_n;

reg clk;

wire [DATA_W*2-1:0] lcm_out;

wire [DATA_W-1:0] mcd_out;

wire vld_out;

initial

begin

A <= 'd0;

B <= 'd0;

vld_in <= 1'b0;

rst_n <= 1'b0;

clk = 1'b0;

#10

rst_n <= 1'b1;

A <= 'd6;

B <= 'd7;

vld_in <= 1'b1;

#2000

A <= 'd12;

B <= 'd8;

vld_in <= 1'b1;

#1000

A <= 'd15;

B <= 'd20;

vld_in <= 1'b1;

end

always #10 clk = ~clk;

lcm

#(

.DATA_W (DATA_W)

)

lcm_u

(

.A (A ),

.B (B ),

.vld_in (vld_in ),

.rst_n (rst_n ),

.clk (clk ),

.lcm_out (lcm_out),

.mcd_out (mcd_out),

.vld_out (vld_out)

);

endmoduleThe waveform is as follows :

边栏推荐

- Interval DP (gravel consolidation)

- 超越PaLM!北大碩士提出DiVeRSe,全面刷新NLP推理排行榜

- Common MySQL interview questions (1) (written MySQL interview questions)

- Appium automation test foundation - appium basic operation API (I)

- Number protection AXB function! (essence)

- Bugku's eyes are not real

- Anti shake and throttling

- Temporary cramming before DFS examination

- Vulnhub-Moneybox

- Summary of the second lesson

猜你喜欢

Bubble sort, insert sort

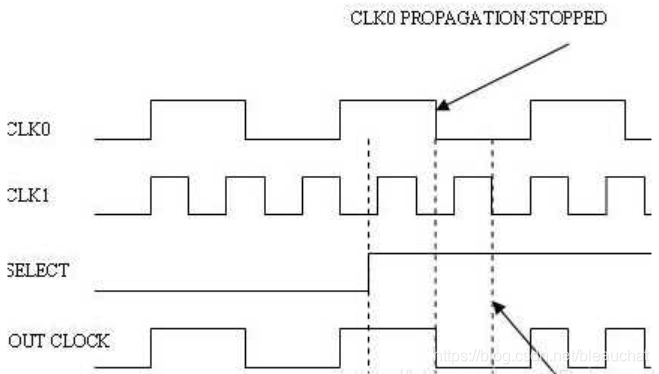

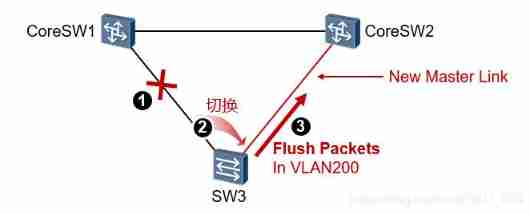

具有倍数关系的时钟切换

Common MySQL interview questions

SQL injection sqllabs (basic challenges) 1-10

JS knowledge points-01

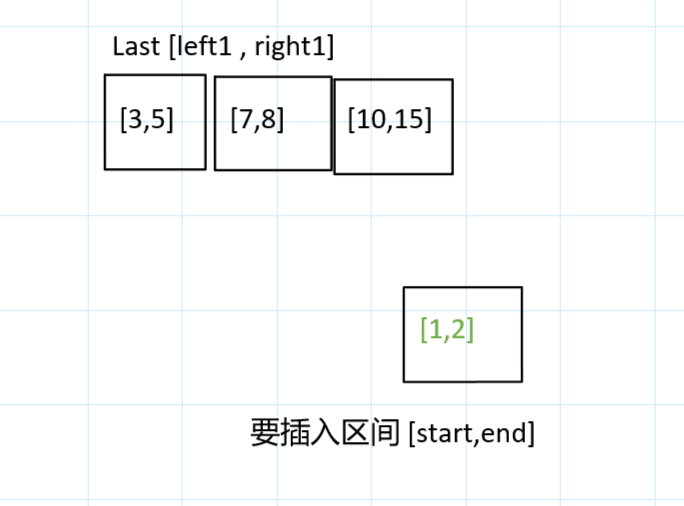

力扣今日题-729. 我的日程安排表 I

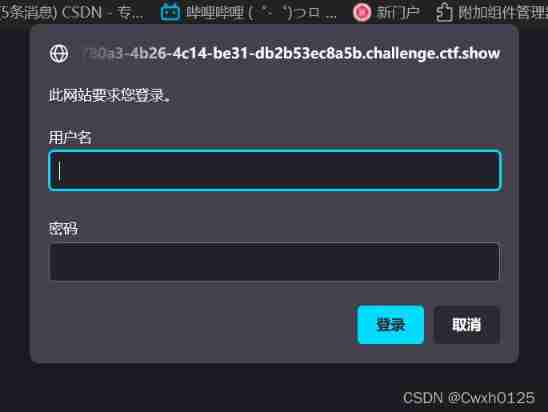

Ctfshow web entry explosion

sql server学习笔记

Detailed explanation of QT creator breakpoint debugger

Data communication foundation smart_ Link_&_ Monitor_ Link

随机推荐

ICML 2022 | 探索语言模型的最佳架构和训练方法

Bugku telnet

Where is the operation of convertible bond renewal? Is it safer and more reliable to open an account

Bubble sort, insert sort

wyt 。。

Value series solution report

修改pyunit_time使得其支持‘xx~xx月’的时间文本

OSI 七层模型

No one consults when doing research and does not communicate with students. UNC assistant professor has a two-year history of teaching struggle

Data communication foundation - route republication

String modification problem solving Report

Surpass palm! Peking University Master proposed diverse to comprehensively refresh the NLP reasoning ranking

MySQL 巨坑:update 更新慎用影响行数做判断!!!

把 ”中台“ 的思想迁移到代码中去

JS topic - console log()

I include of spring and Autumn

First PR notes

I'm fat, huh

Common PHP interview questions (1) (written PHP interview questions)

CSRF, XSS science popularization and defense