当前位置:网站首页>Développement d'un module d'élimination des bavardages à clé basé sur la FPGA

Développement d'un module d'élimination des bavardages à clé basé sur la FPGA

2022-07-06 03:49:00 【FPGA et MATLAB】

1.Version logicielle

QUARTUSII8.1

Modelsim6.5d

2.Code source du système

module tops(

i_clk, //100M

i_rst, //Fonction de Réinitialisation du système,Réinitialisation de haut niveau,Si vous n'utilisez pas cet angle,Donc un niveau direct bas suffit

i_input1, //Entrée de la clé1

i_input2, //Entrée de la clé2

o_output1,//Sortie d'impulsion1

o_output2,//Sortie d'impulsion2

test_cnt1,//Compteur d'essai1

test_cnt2,//Compteur d'essai2

test_enable1,//Tester le signal d'activation

test_enable2 //Tester le signal d'activation

);

//100Mégal à10ns,Alors...1sLe milieu est10_000_000- Oui.100MCycle d'horloge

//Lors de la simulation,Pour faciliter la visualisation des résultats de la simulation,Donc10_000_000Remplacer par une valeur plus petite10_000

//parameter NUM = 32'd10000000; //Utilisation pratique

parameter NUM = 32'd100; //Pour la simulation

input i_clk;//100MPour10ns

input i_rst;

input i_input1;

input i_input2;

output o_output1;

output o_output2;

output[31:0]test_cnt1;

output[31:0]test_cnt2;

output test_enable1;

output test_enable2;

reg o_output1 = 1'b0;

reg o_output2 = 1'b0;

reg test_enable1 = 1'b0;

reg test_enable2 = 1'b0;

reg[31:0]cnt1 = 32'd0;

reg[31:0]cnt2 = 32'd0;

reg flag1 = 1'b1;

reg flag2 = 1'b1;

always @(posedge i_clk or posedge i_rst)// Processus principal de traitement

begin

if(i_rst)//Réinitialisation du système

begin

test_enable1 <= 1'b0;// Définir le signal d'activation

test_enable2 <= 1'b0;// Définir le signal d'activation

cnt1 <= 32'd0;

cnt2 <= 32'd0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

else begin

if(i_input1 == 1'b0 & i_input2 == 1'b1 & flag1 == 1'b1)//Appuyez sur la touche1, Sans appuyer sur la touche 2

begin

//1s L'horloge permet de maintenir 10_000_000Cycles d'horloge

cnt2 <= 32'd0;

if(cnt1 < NUM)//Non.1s

begin

cnt1 <= cnt1 + 32'd1;

test_enable1 <= 1'b1;//Produits1Impulsions,//Après avoir appuyé sur le bouton,En cours1sHorloge

test_enable2 <= 1'b0;

flag1 <= 1'b1;// Pour bloquer le deuxième bouton

flag2 <= 1'b0;// Pour bloquer le deuxième bouton

end

if(cnt1 == NUM)//À1s,Arrêter la sortie

begin

cnt1 <= cnt1;

test_enable1 <= 1'b0;

test_enable2 <= 1'b0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

end

if(i_input1 == 1'b1 & i_input2 == 1'b0 & flag2 == 1'b1)//Appuyez sur la touche2, Sans appuyer sur la touche 1

begin

//50s L'horloge permet de maintenir

cnt1 <= 32'd0;

if(cnt2 < 50*NUM)//Non.50s

begin

cnt2 <= cnt2 + 32'd1;

test_enable1 <= 1'b0;//Produits1Impulsions,//Après avoir appuyé sur le bouton,En cours1sHorloge

test_enable2 <= 1'b1;

flag1 <= 1'b0;// Utilisé pour bloquer les 1Les boutons

flag2 <= 1'b1;// Utilisé pour bloquer les 1Les boutons

end

if(cnt2 == 50*NUM)//À1s,Arrêter la sortie

begin

cnt2 <= cnt2;

test_enable1 <= 1'b0;

test_enable2 <= 1'b0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

end

if(i_input1 == 1'b1 & i_input2 == 1'b1)// Il n'y a pas d'opération clé

begin

cnt1 <= 32'd0;

cnt2 <= 32'd0;

end

end

end

assign test_cnt1 = cnt1;

assign test_cnt2 = cnt2;

// Voici le signal d'énergie ,Impulsion de sortie

// Définir deux compteurs d'impulsions

reg[31:0]pcnt1 = 32'd0;

reg[31:0]pcnt2 = 32'd0;

always @(posedge i_clk or posedge i_rst)// Processus principal de traitement

begin

if(i_rst)//Réinitialisation du système

begin

pcnt1 <= 32'd0;

pcnt2 <= 32'd0;

o_output1 <= 1'b0;

o_output2 <= 1'b0;

end

else begin

if(test_enable1 == 1'b1)//1s One inside 100nsImpulsions,C'est - à - dire:1s Il y a un 10MLe signal d'impulsion de

begin

pcnt1 <= pcnt1 + 32'd1;

if(pcnt1 < 32'd10)

begin

o_output1 <= 1'b1;//Produire100nsSignal de

end

else begin

o_output1 <= 1'b0;

end

end

else begin

pcnt1 <= 32'd0;

o_output1 <= 1'b0;

end

if(test_enable2 == 1'b1)//50sIntérieur50- Oui.100nsImpulsions,C'est - à - dire:1s Il y a un 10MLe signal d'impulsion de

begin

if(pcnt2 == NUM-1)

begin

pcnt2 <= 32'd0;

end

else begin

pcnt2 <= pcnt2 + 32'd1;

end

if(pcnt2 < 32'd10)

begin

o_output2 <= 1'b1;//Produire100nsSignal de

end

else begin

o_output2 <= 1'b0;

end

end

else begin

pcnt2 <= 32'd0;

o_output2 <= 1'b0;

end

end

end

endmodule 3.Conclusion de la simulation

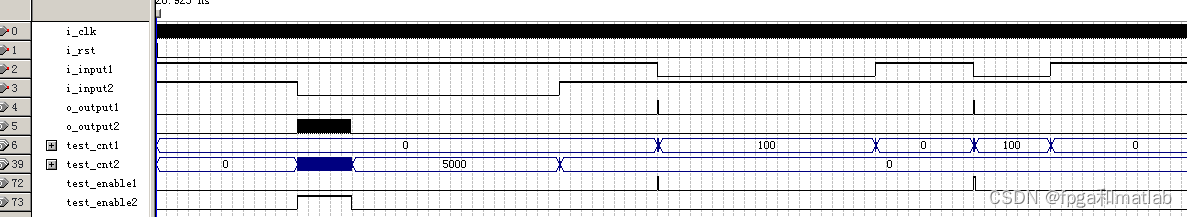

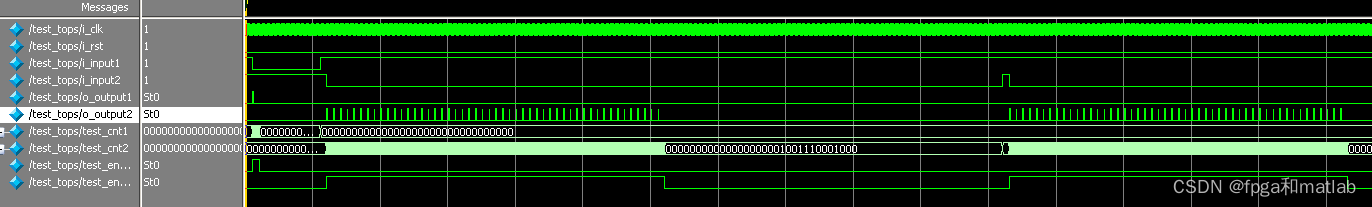

QII Avec des instructions de simulation :

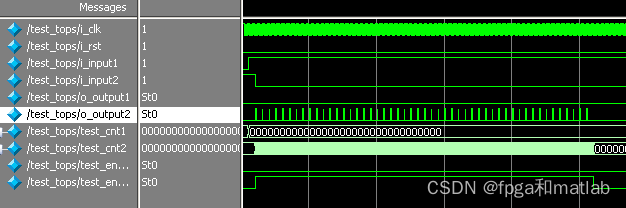

Nous avons agrandi localement la forme d'onde :

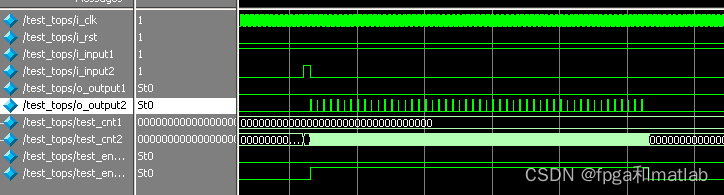

Première partie,Je vois.input1Est élevé,input2Faible,Description2C'est pressé.,Alors...output2 Produire des 50Impulsions.

Deuxième partie,input1Faible, La première touche est pressée , Il n'y a donc qu'un seul signal de haut niveau

Partie III, C'est toujours le premier bouton qui a été appuyé , Donc une seule impulsion est générée .

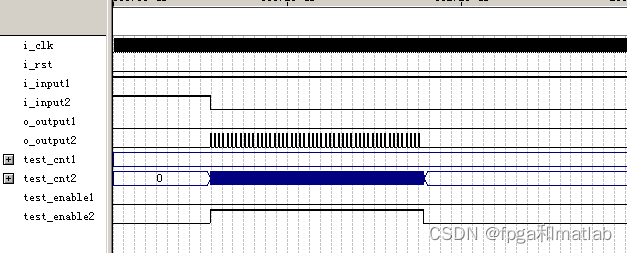

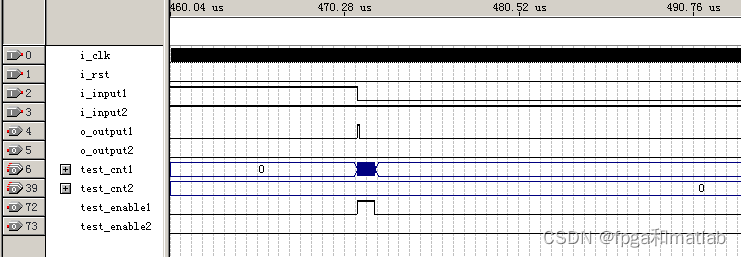

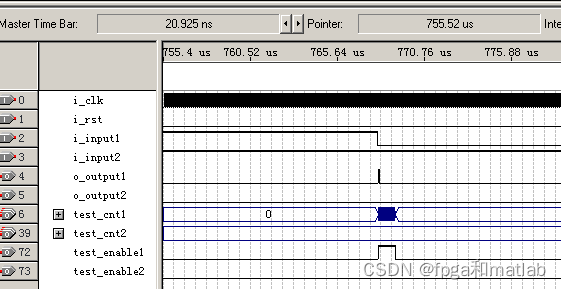

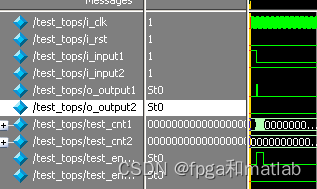

Modelsim Description de la simulation :

Nous avons agrandi localement la simulation :

Une fois la clé enfoncée :

La clé 2 est pressée ;

Ou la clé 2 est pressée .

A35-09

边栏推荐

- 【FPGA教程案例11】基于vivado核的除法器设计与实现

- 简易博客系统

- 有条件地 [JsonIgnore]

- Overview of super-resolution reconstruction of remote sensing images

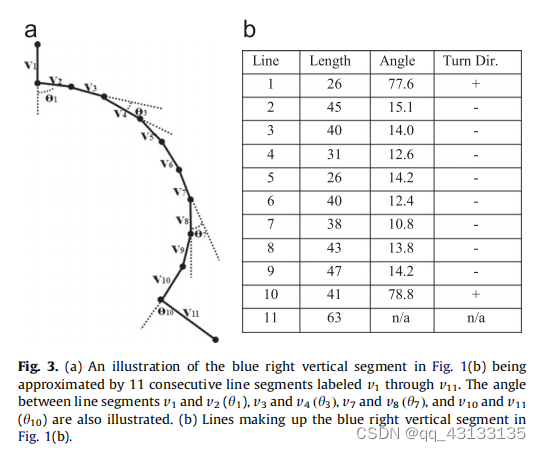

- Edcircles: a real time circle detector with a false detection control translation

- 多项目编程极简用例

- 【PSO】基于PSO粒子群优化的物料点货物运输成本最低值计算matlab仿真,包括运输费用、代理人转换费用、运输方式转化费用和时间惩罚费用

- [rust notes] 18 macro

- MySQL about self growth

- Error 1045 (28000): access denied for user 'root' @ 'localhost' (using password: no/yes

猜你喜欢

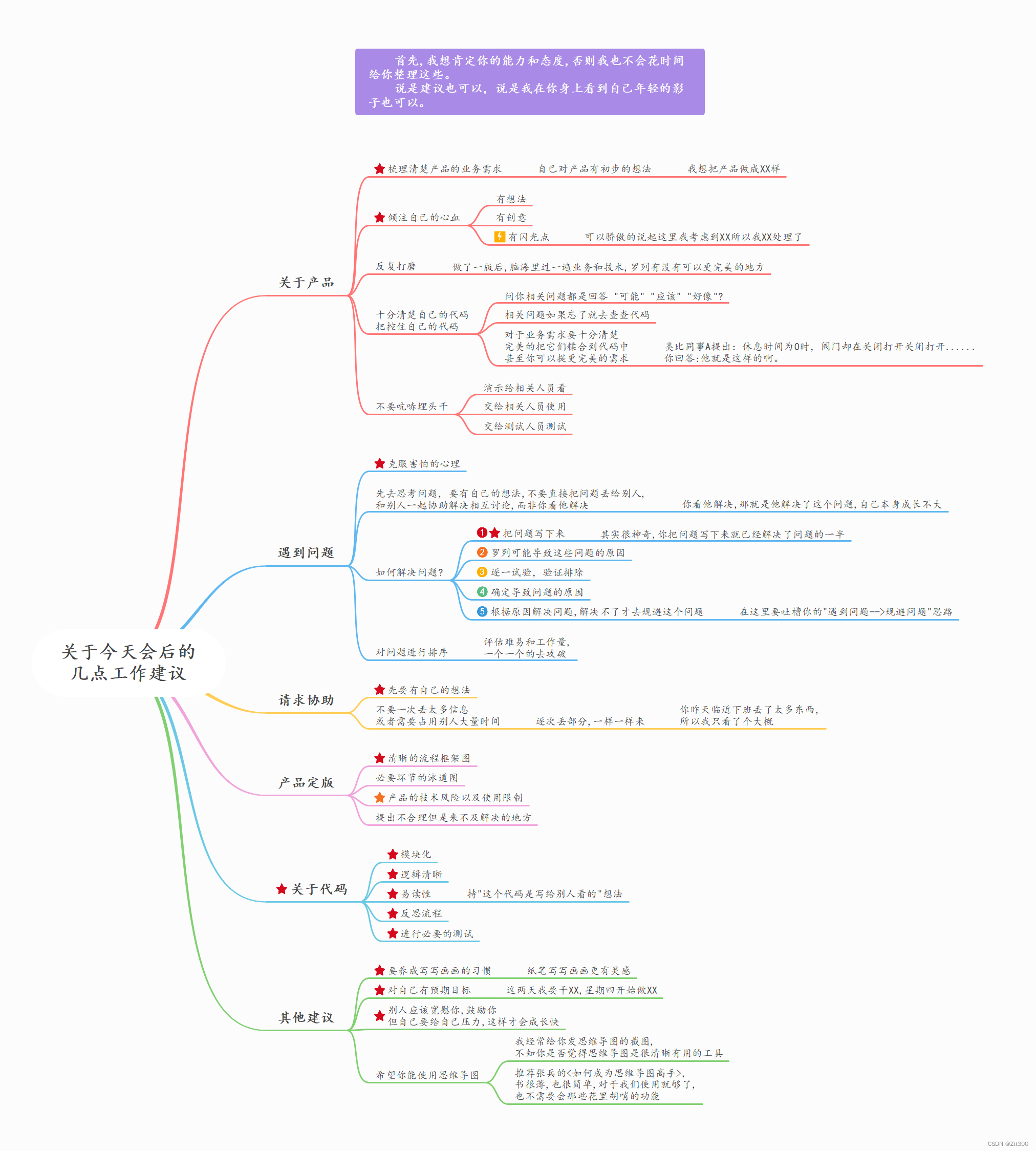

Suggestions for new engineer team members

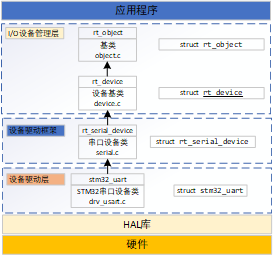

3.1 detailed explanation of rtthread serial port device (V1)

JVM的手术刀式剖析——一文带你窥探JVM的秘密

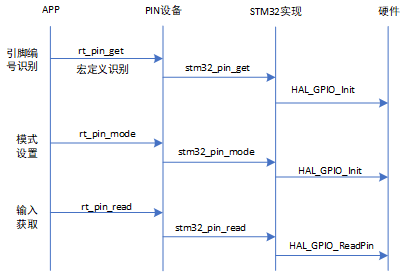

2.2 fonctionnement stm32 GPIO

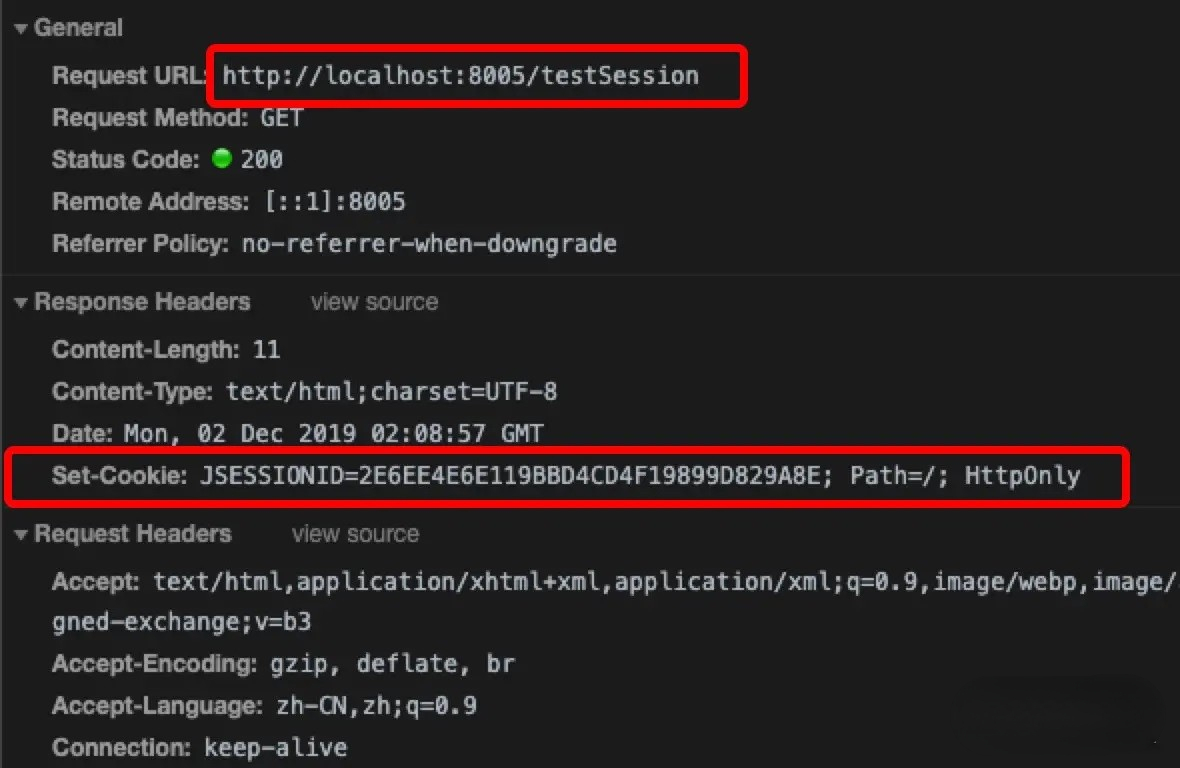

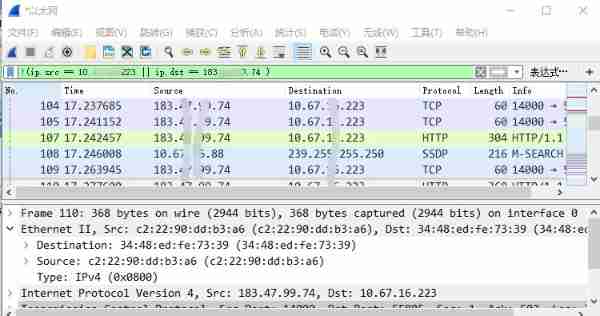

Do you know cookies, sessions, tokens?

在字节做测试5年,7月无情被辞,想给划水的兄弟提个醒

Edcircles: a real time circle detector with a false detection control translation

JS music online playback plug-in vsplayaudio js

Network security - Security Service Engineer - detailed summary of skill manual (it is recommended to learn and collect)

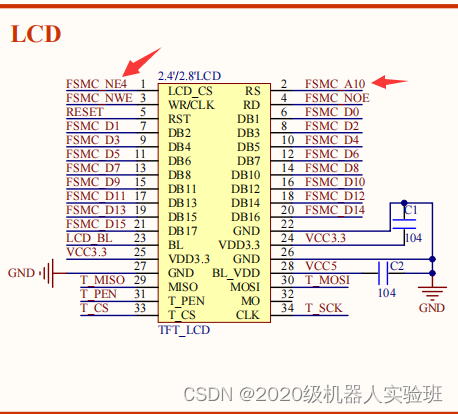

Cubemx transplantation punctual atom LCD display routine

随机推荐

Factors affecting user perception

STC8H开发(十二): I2C驱动AT24C08,AT24C32系列EEPROM存储

Facebook等大廠超十億用戶數據遭泄露,早該關注DID了

three. JS page background animation liquid JS special effect

2. GPIO related operations

自动化测试的好处

数据分析——seaborn可视化(笔记自用)

在字节做测试5年,7月无情被辞,想给划水的兄弟提个醒

Canvas cut blocks game code

Python implementation of maddpg - (1) openai maddpg environment configuration

【可调延时网络】基于FPGA的可调延时网络系统verilog开发

Differential GPS RTK thousand search

Microkernel structure understanding

User experience index system

Do you know cookies, sessions, tokens?

Ks003 mall system based on JSP and Servlet

C#(二十八)之C#鼠标事件、键盘事件

Record the process of reverse task manager

3分钟带你了解微信小程序开发

Blue Bridge Cup - Castle formula