当前位置:网站首页>input_delay

input_delay

2022-07-06 19:35:00 【qq_32752869】

0 前言

时序分析基础,底层原则:

时序要满足latch的setup&hold时间。在要求的稳定窗口内数据不能变化。

基本时序模型

Stack(setup)= T-Tsu-Tco-Tdata 相邻2个时钟

Stack(hold )= Tco + Tdata - Thd 同1个时钟

如果 Tco 和 Tdata 延迟变大,保持时间 Stack (hold) 裕度越大

当出现hold违例,可以增加Tdata走线长度来消除。

如果 Tco 和 Tdata 延迟变大,建立时间 Stack (setup) 裕度越小

1 input delay分析

FPGA管脚上的视角来看

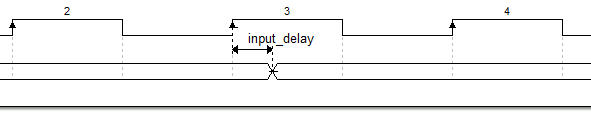

input delay 描述数据port在latch时钟沿来看,数据延后了多久才稳定。

max_delay(分析setup)

min_delay(分析hold )

1.1 input delay的分类

系统同步分为3种:(SDR上升沿、SDR下降沿、DDR)x(边沿对齐)

源同步分为6种 :(SDR上升沿、SDR下降沿、DDR)x(中心对齐、边沿对齐)

外部器件可能会提供 Tco\setup\hold\shew

需要注意的隐含点:

- 源同步边沿对齐默认在接收侧(FPGA)内存在PLL进行移相180度。

- 系统同步只有边沿对齐,没有中心对齐。

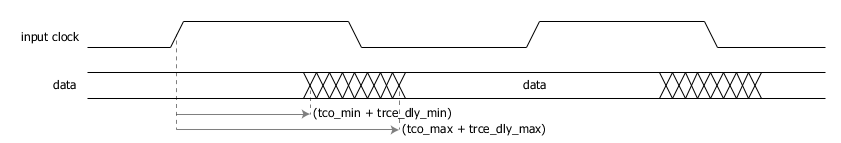

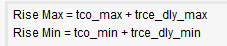

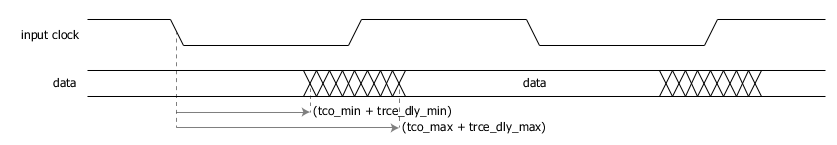

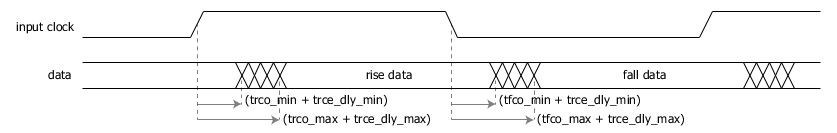

1.2 Tdly 的定义

在进行intput delay计算的时候需要考虑时钟路径的延时和数据路径的延时,

而FPGA来看,只需要知道数据相对于时钟的延时,那么可以将时钟延时看做0,

并且将时钟路径延时补偿到数据路径延时中得到Tdly,Tdly=数据路径-时钟路径。这样能够减少分析的变量。

1.3 总结

- 上升沿不添加-clock_fall ,默认就是上升沿。下降沿与上升沿的区别就在于添加-clock_fall 。

- DDR约束就多了-clock_fall -add_delay

- 描述的是坐标时间,二部是绝对差值。以latch为0时刻。

2 具体内容

2.1 系统同步

系统同步的数据都是出现在launch沿之后,latch是下一个沿

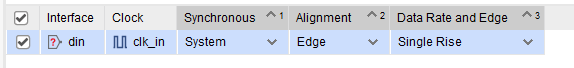

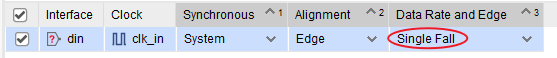

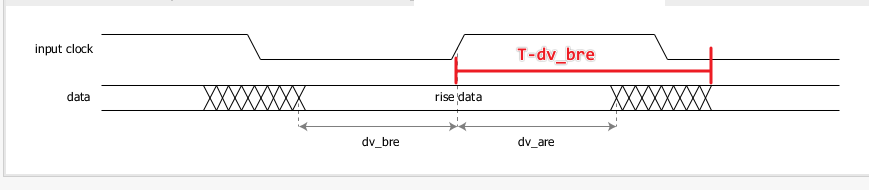

2.1.1 SDR上升沿

已知:

时钟名 : clk_in

数据port : din

T =10ns

Tco =1~2ns

Tdly=0.3~0.4ns

得到:

set_input_delay -clock clk_in -max 2.4 [get_ports din]

set_input_delay -clock clk_in -min 1.3 [get_ports din]

需要注意是 -max 2.4 而不是 -max_delay 2.4

2.1.2 SDR下降沿

已知:

时钟名 : clk_in

数据port : din

T =10ns

Tco =1.5~2ns

Tdly=0.3~0.4ns

得到:

set_input_delay -clock clk_in -max 2.4 [get_ports din] -clock_fall

set_input_delay -clock clk_in -min 1.8 [get_ports din] -clock_fall

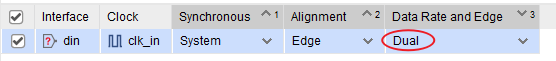

2.1.2 DDR

已知:

时钟名 : clk_in

数据port : din

T =10ns

Tco =1.0~2ns 上升沿

Tco =1.5~2ns 下降沿

Tdly=0.3~0.4ns

得到:

set_input_delay -clock clk_in -max 2.4 [get_ports din]

set_input_delay -clock clk_in -min 1.3 [get_ports din]

set_input_delay -clock clk_in -max 2.4 [get_ports din] -clock_fall -add_delay

set_input_delay -clock clk_in -min 1.8 [get_ports din] -clock_fall -add_delay

//有个知识点:下降沿发起的数据是在下个上升沿采样。所以data path是从5开始。

2.2 源同步

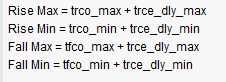

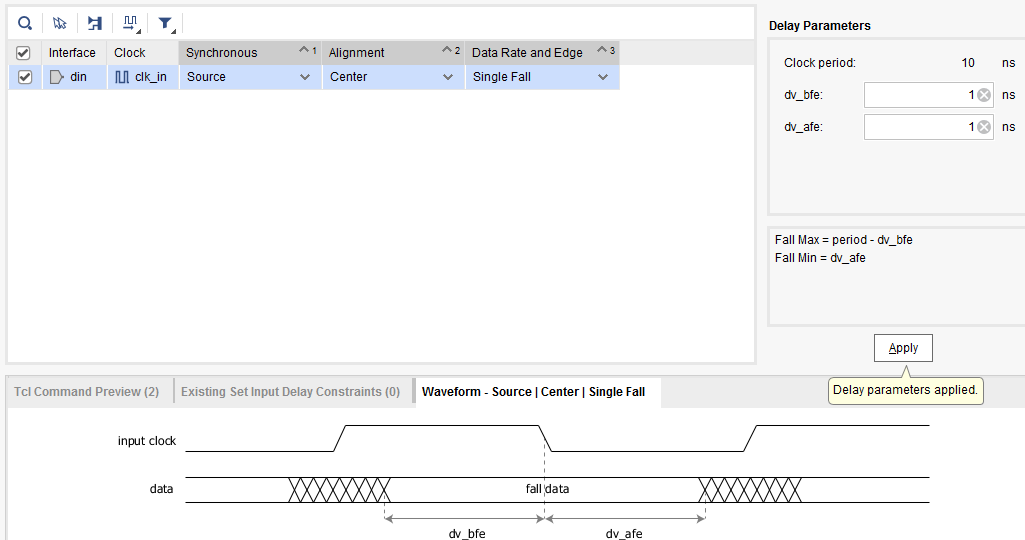

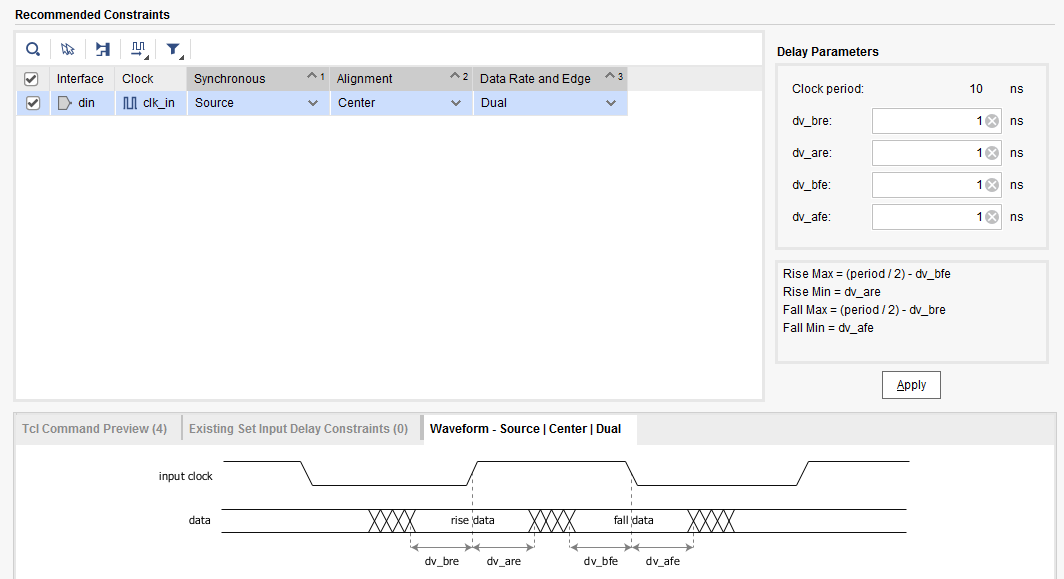

2.2.1 源同步 中心对齐

中心对齐的latch沿是是图中的上升沿的下一个上升沿。可以看到input_delay的范围是[dv_are,T-dv_bre],由于时钟是周期的。

2.2.1.1 上升沿

set_input_delay -clock [get_clocks clk_in] -min -add_delay 1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 9.0 [get_ports din]

2.2.1.2 下降沿

set_input_delay -clock [get_clocks clk_in] -clock_fall -min -add_delay 1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -clock_fall -max -add_delay 9.0 [get_ports din]

2.2.1.3 DDR

set_input_delay -clock [get_clocks clk_in] -clock_fall -min -add_delay 1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -clock_fall -max -add_delay 4.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -min -add_delay 1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 4.0 [get_ports din]

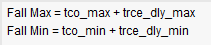

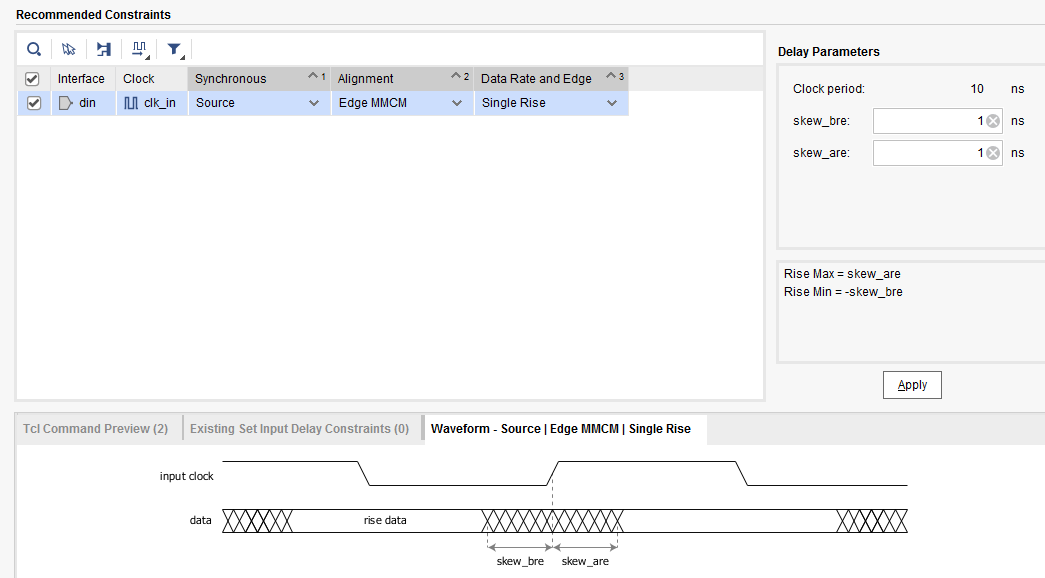

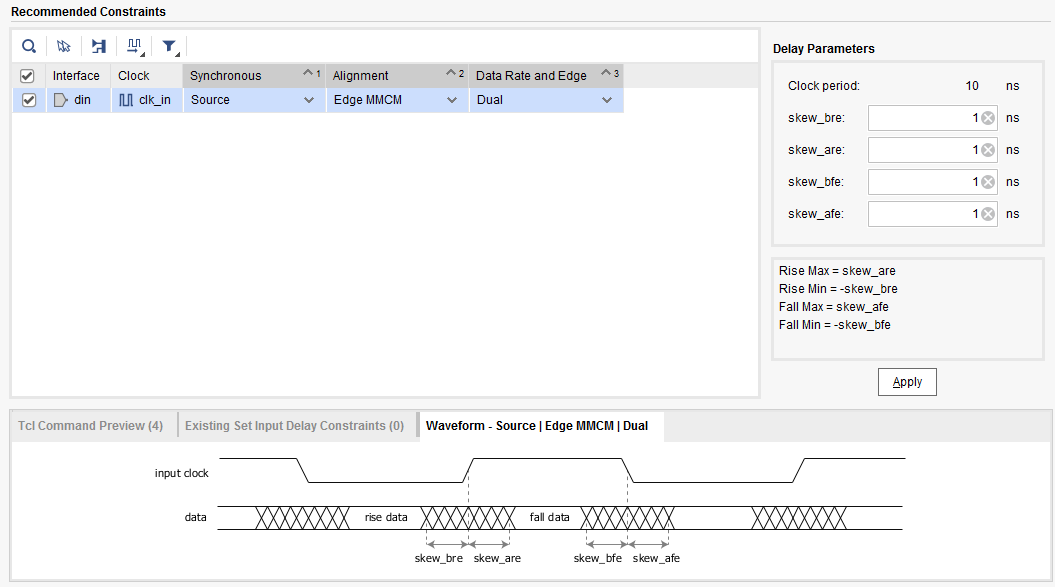

2.3.2 源同步 边沿MMCM对齐

MMCM具有调整时钟相位的功能。latch沿就是图中的上升沿,ltach的数据是上升沿之后的数据。

2.3.2.1 上升沿

set_input_delay -clock [get_clocks clk_in] -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 1.0 [get_ports din]

2.3.2.2 下降沿

-clock_fall

2.3.2.3 DDR

set_input_delay -clock [get_clocks clk_in] -clock_fall -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -clock_fall -max -add_delay 1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 1.0 [get_ports din]

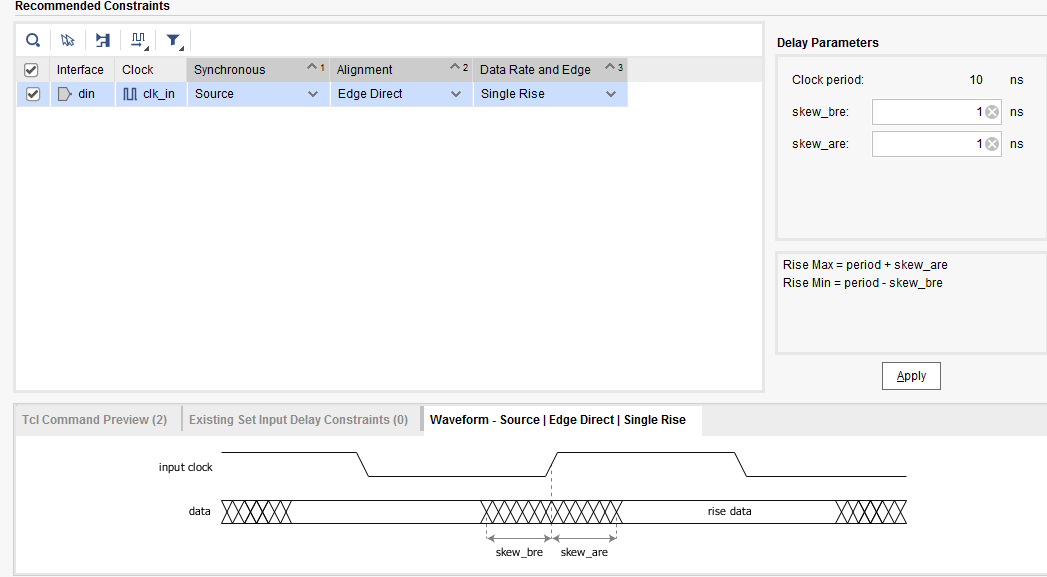

2.3.3 源同步 边沿直接对齐

2.3.3.1 上升沿

set_input_delay -clock [get_clocks clk_in] -min -add_delay 9.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 11.0 [get_ports din]

2.3.3.2 下降沿

-fall_clock

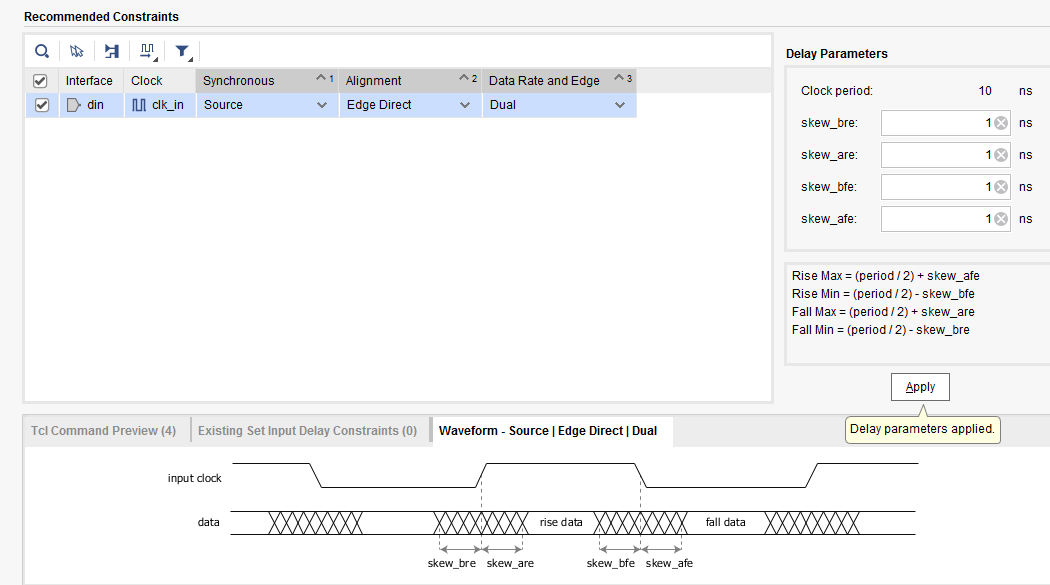

2.3.3.3 DDR

set_input_delay -clock [get_clocks clk_in] -clock_fall -min -add_delay 4.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -clock_fall -max -add_delay 6.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -min -add_delay 4.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 6.0 [get_ports din]

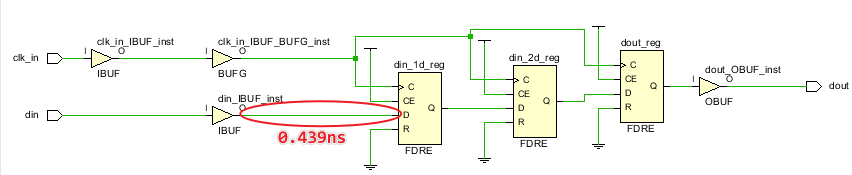

实验

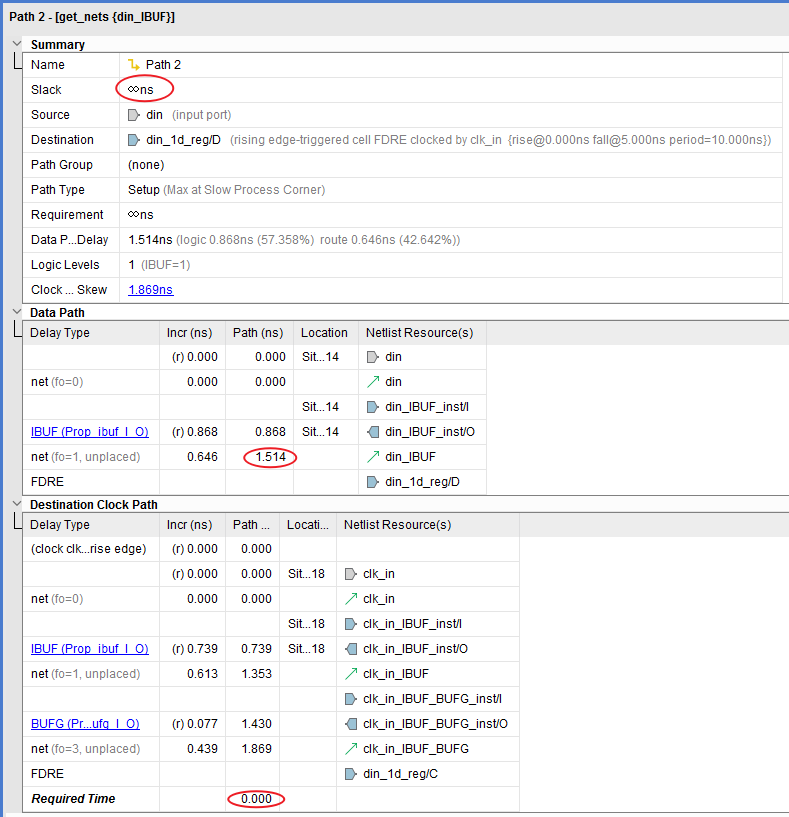

未约束input_delay 的编译结果

未添加约束,slack =无穷,也就是无法分析。

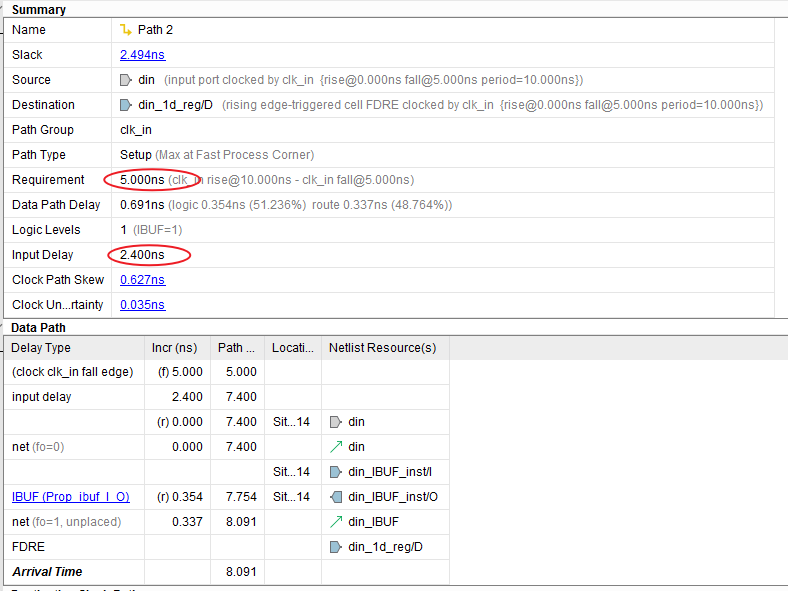

添加DDR input delay 约束

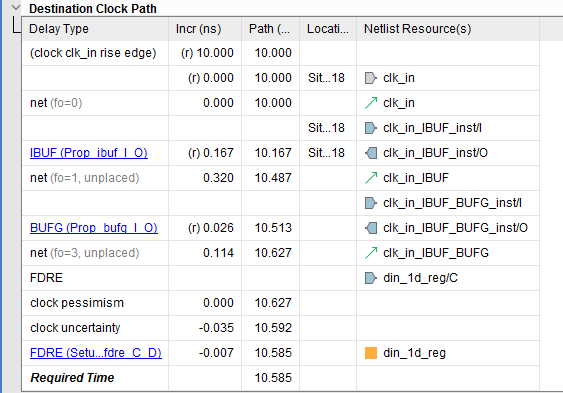

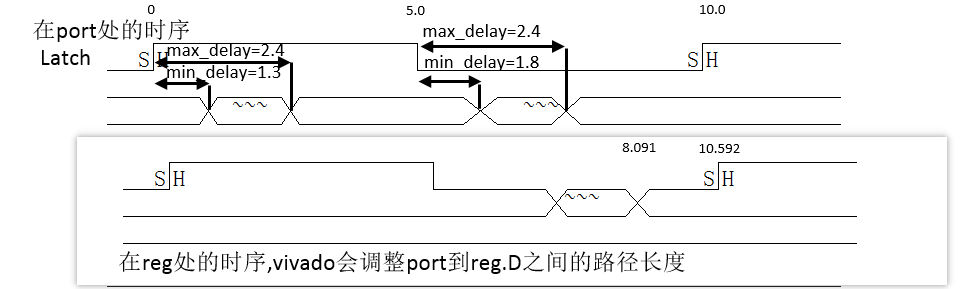

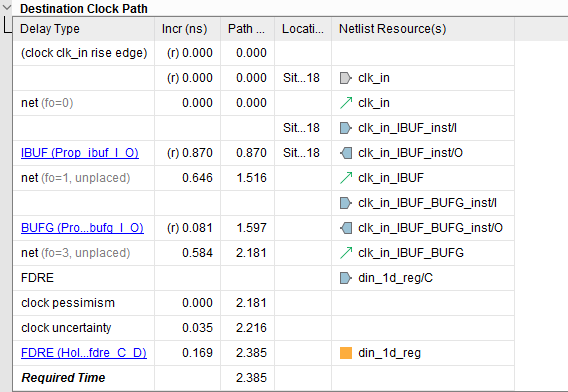

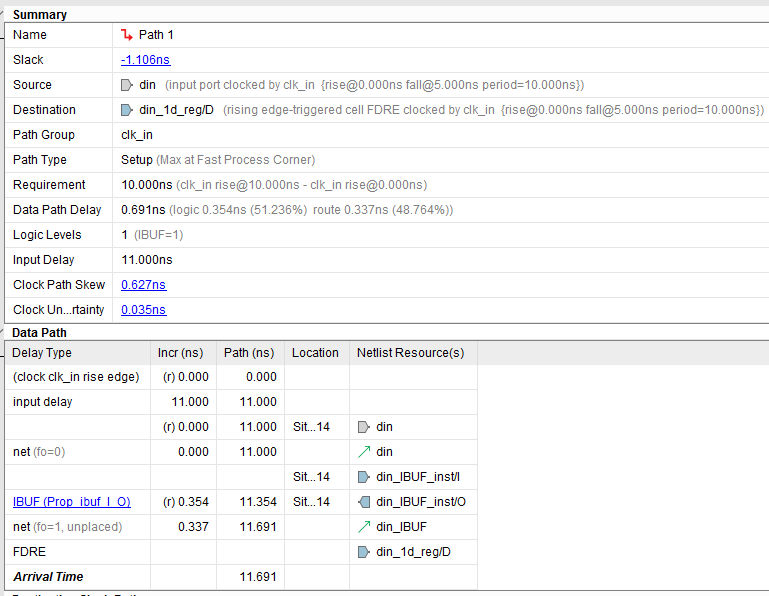

vivado分析最差路径(上升沿和下降沿的hold都能满足)也就是下降沿发送数据,上升沿采样。

data path的起点launch沿是5.0ns表示分析的是下降沿发起的数据。进过3.091ns到达reg.D

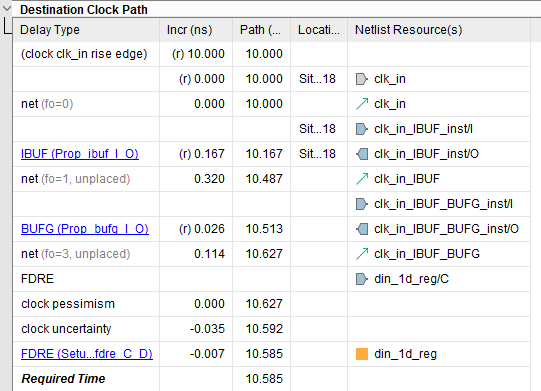

从destination clock path 窗口看到,latch沿是10.0ns,正好符合下降沿发送数据,上升沿采样。

时钟从clk_in port 经过bufg等延时,再减去setup就能得到required time。可以看到setup很小只有0.007ns。

对比

use MMCM 边沿 源同步

set_input_delay -clock [get_clocks clk_in] -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 1.0 [get_ports din]

直接 边沿 源同步

set_input_delay -clock [get_clocks clk_in] -min -add_delay 9.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 11.0 [get_ports din]

两者的区别是什么?感觉相差一个周期。

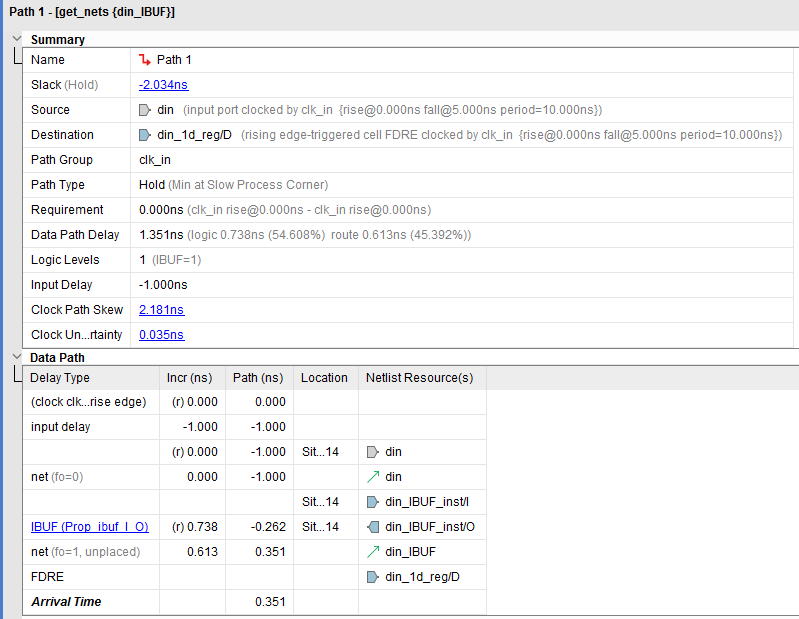

使用下面约束,不添加MMCM 会报错hold见下面截图,看到是时钟路径过长

set_input_delay -clock [get_clocks clk_in] -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 1.0 [get_ports din]

当使用下面约束,有setup报错

set_input_delay -clock [get_clocks clk_in] -min -add_delay 9.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 11.0 [get_ports din]

对比

## 约束1:

set_input_delay -clock [get_clocks clk_in] -min -add_delay -1.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 1.0 [get_ports din]

## 约束2:

set_input_delay -clock [get_clocks clk_in] -min -add_delay 9.0 [get_ports din]

set_input_delay -clock [get_clocks clk_in] -max -add_delay 11.0 [get_ports din]

约束1和约束2比较,两者的区别是什么?感觉就相差一个周期10ns。

结论:

使用约束1,vivado的默认latch沿的时钟是0ns的,时钟路径从0ns开始累积。当前launch就是当前latch,

使用约束2,vivado的默认latch沿的时钟是10ns的,时钟路径从10ns开始累积。

两者的latch时钟相差一个周期T=10ns。

参考

https://my.oschina.net/msxbo/blog/3122304

边栏推荐

- The annual salary of general test is 15W, and the annual salary of test and development is 30w+. What is the difference between the two?

- 杰理之RTC 时钟开发【篇】

- 左程云 递归+动态规划

- Summary of basic debugging steps of S120 driver

- leetcode-02(链表题)

- PSINS中19维组合导航模块sinsgps详解(初始赋值部分)

- 密码学系列之:在线证书状态协议OCSP详解

- Remember the problem analysis of oom caused by a Jap query

- Oracle connection pool is not used for a long time, and the connection fails

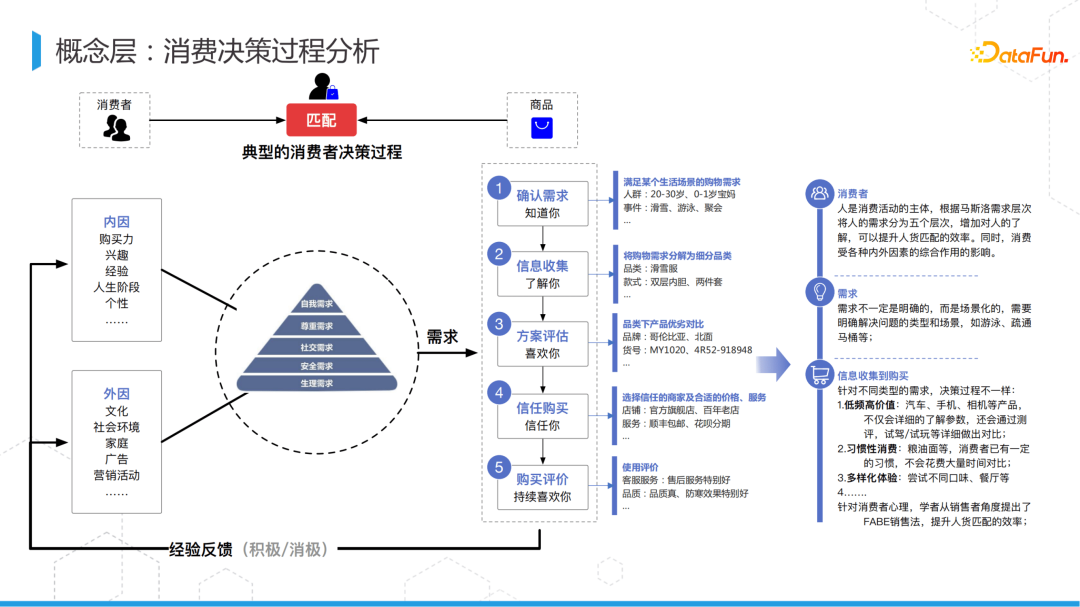

- 商城商品的知识图谱构建

猜你喜欢

wireshark安装

OC, OD, push-pull explanation of hardware

商城商品的知识图谱构建

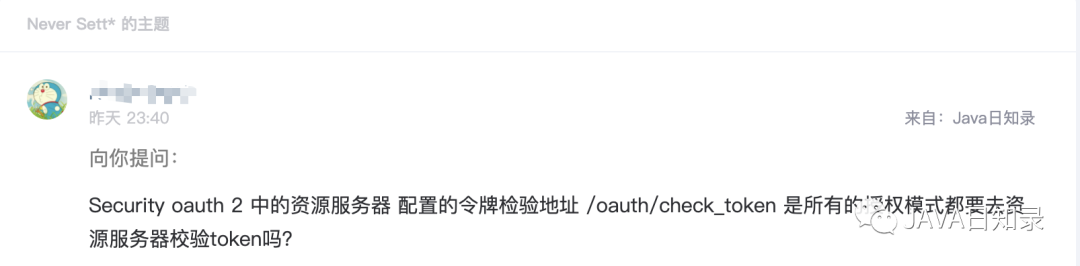

How to verify accesstoken in oauth2 protocol

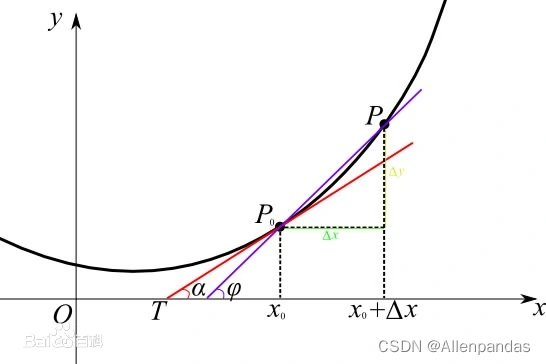

Derivative, partial derivative, directional derivative

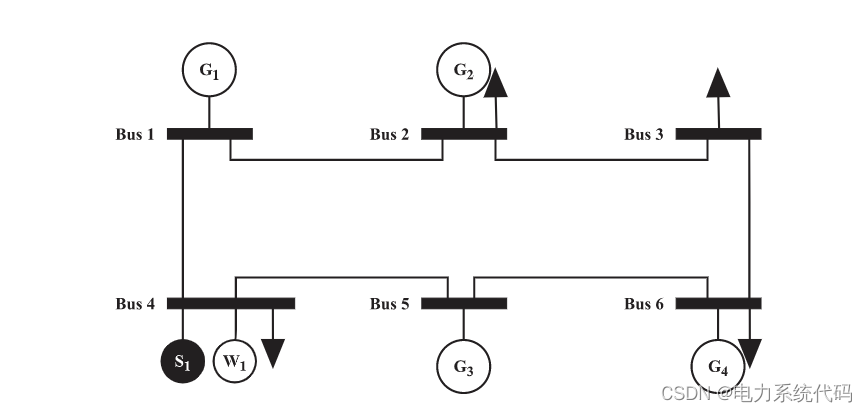

Matlb| economic scheduling with energy storage, opportunity constraints and robust optimization

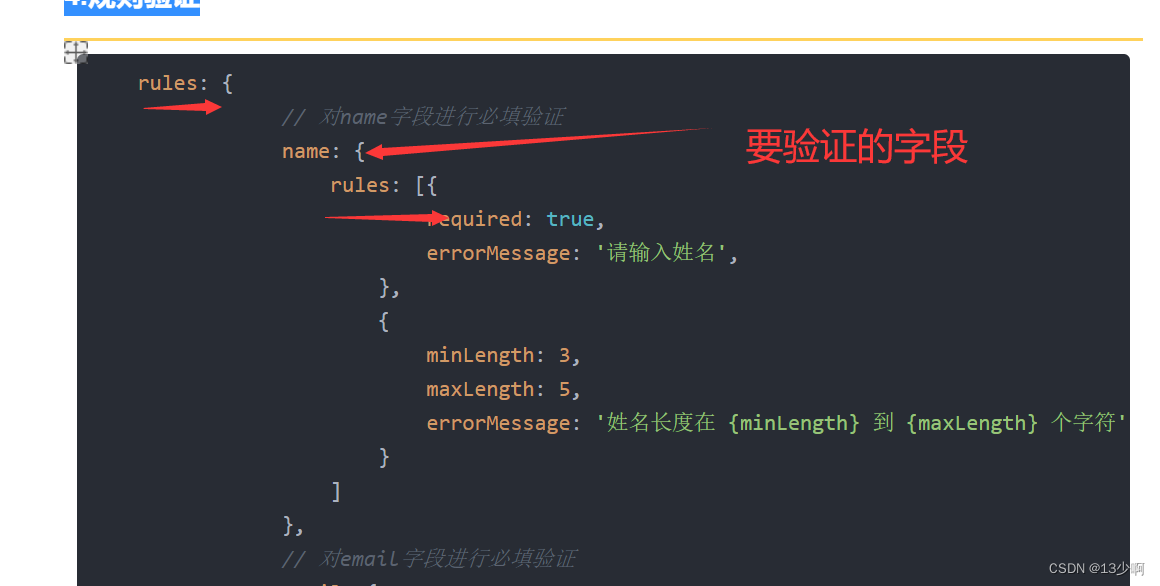

Form validation of uniapp

uniapp适配问题

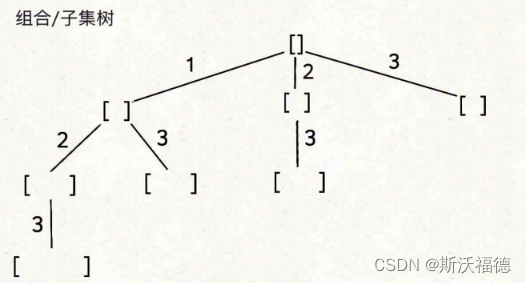

LeetCode 77:组合

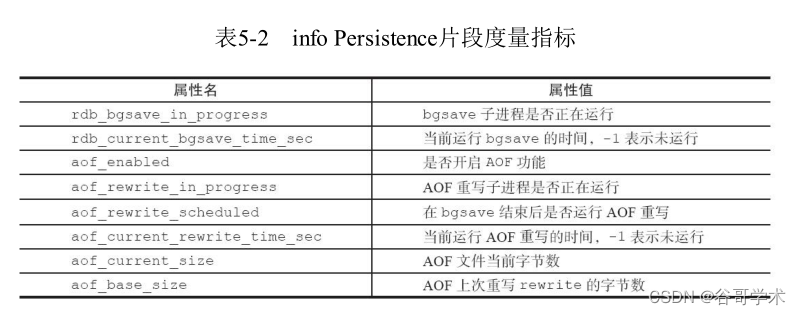

Redis入门完整教程:问题定位与优化

随机推荐

Derivative, partial derivative, directional derivative

Detailed explanation of 19 dimensional integrated navigation module sinsgps in psins (initial assignment part)

Code debugging core step memory

2022 spring recruitment begins, and a collection of 10000 word interview questions will help you

Redis入门完整教程:复制原理

Data analysis from the perspective of control theory

MySQL - common functions - string functions

PSINS中19维组合导航模块sinsgps详解(初始赋值部分)

How-PIL-to-Tensor

又一百万量子比特!以色列光量子初创公司完成1500万美元融资

Cryptography series: detailed explanation of online certificate status protocol OCSP

Mmdetection3d loads millimeter wave radar data

新标杆!智慧化社会治理

杰理之在非蓝牙模式下,手机连接蓝牙不要跳回蓝牙模式处理方法【篇】

[node learning notes] the chokidar module realizes file monitoring

uniapp适配问题

A complete tutorial for getting started with redis: problem location and optimization

Convert widerperson dataset to Yolo format

Nuggets quantification: obtain data through the history method, and use the same proportional compound weight factor as Sina Finance and snowball. Different from flush

Code line breaking problem of untiy text box