当前位置:网站首页>FSM and I2C experiment report

FSM and I2C experiment report

2022-07-06 15:24:00 【Hu Da jinshengyu】

platform 2HDL Language and verification experiment report

One 、 Self determination FSM explain

1、 State description

S0:sleep,S1: Get out of bed ,S2: breakfast ,S3: motion ,S4: attend class;class begins ,S5: Chinese food ,S6: Open pendulum ,S7: My lunch break ,S8: exercise ,S9: Self study ,S10: Take a shower ,S11: Eat midnight snack

2、 Design code description

The first is to code the state we define , The code is as follows :

state0=4'b0000,

state1=4'b0001,

state2=4'b0010,

state3=4'b0011,

state4=4'b0100,

state5=4'b0101,

state6=4'b0110,

state7=4'b0111,

state8=4'b1000,

state9=4'b1001,

state10=4'b1010,

state11=4'b1111;Next , It is the code for jumping between each state :

[email protected](*)

case(state)

state0:if(start)next_st=state1;

else next_st=state0;

state1:next_st=state2;

state2:if(skip1)next_st=state3;

else next_st=state4;

state3:next_st=state5;

state4:next_st=state5;

state5:if(play)next_st=state6;

else next_st=state7;

state6:next_st=state7;

state7:if(read)next_st=state9;

else next_st=state8;

state8:next_st=state10;

state9:if(wash)next_st=state10;

else next_st=state11;

state10:if(eat)next_st=state11;

else next_st=state0;

state11:next_st=state0;

default:next_st=state0;

endcasehere , The implementation of the code is very simple , When a state is a condition , Will jump to another condition , Here, because the picture I drew is too ugly , I won't show it here .

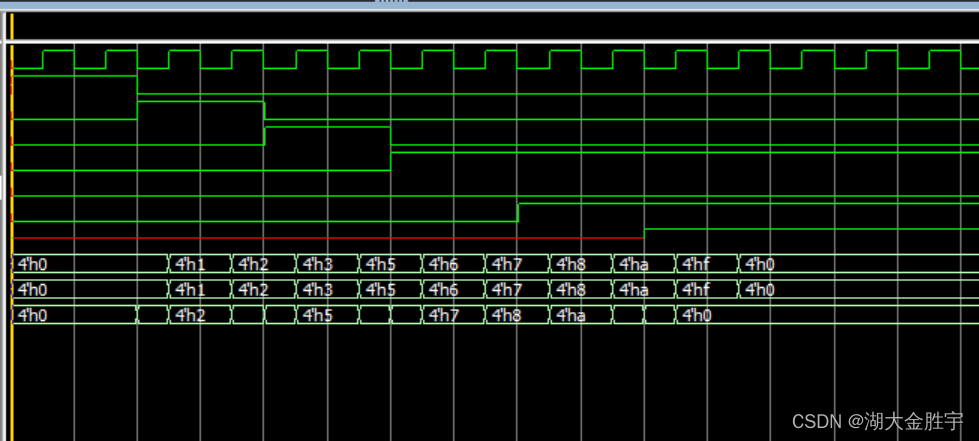

3、 Description of simulation waveform ( Screenshot + Text annotation )

Before simulation , We need to write a test file , That is, a file that specifically controls the waveform output :

initial begin

start=0; skip1=0; play=0; read=0; wash=0;

#1;

#200 start = 1;

#200 start = 0;skip1 = 1;

#200 skip1 = 0;play = 1;

#200 read = $random;wash = 1;

#200 eat=1;

wait(zot ==4'b1010)

repeat(1024)@(posedge clk);

$stop;

endhere , We define every 200ns Set a semaphore , From the code, we can infer that in 1ns It's about ,reset The signal is 1, Initialize all signals to 0.

keep 200ns after ,start The signal changes to 1( That is, the alarm clock rings , It's time to get up ), Here we speculate that the state changes to S1( That is to say 4'h1), At the same time as S1 and S2 There is no conditional judgment jump , So this period of time will eventually become S2 state ( That is, you will have breakfast anyway ).

The above situation remains 200ns after ,start The signal is set to 0,skip1 The signal is set to 1, That is to say S2 The state will become S3 state ( That is to go out for a walk after breakfast ),S3 and S5 There is also no condition to judge whether to jump , This is where you take a walk after breakfast , If you are hungry, you will naturally go to lunch .

Another time 200ns after ,skip The signal is set to 0,play The signal is set to 1 了 . This will start from S5 The status jumps to S6 state ( That is, after dinner , Naturally, we need to play games ). It's also impossible to play games all the time , After a period of time, it will automatically jump to S7 state , Here is after a while , Naturally, we need to take a lunch break .

Again 200ns,read The signal is set to a random value ( That is, after the lunch break , Maybe go to self-study , Or maybe not ), meanwhile wash The signal is set to 1, That is, whether it's self-study or not , if read The signal is 1 Words , I will take a bath after self-study , if read The signal is 0 Words , You won't go to self-study , But to exercise , Take a bath after exercise .

Last 200ns after ,eat The signal is set to 1, That is, after taking a bath , We are going to have supper, that is S11 state , Finally, we will sleep 了 , The day is over .

Through the waveform , Verify that our analysis is correct . The above analysis is the analysis of the simulation waveform .

Two 、EEPROM Read and write code design and simulation

1、 Code instructions

port

`timescale 1ns / 1ps // Time unit 1ns, precision 1ps

module i2c(

input clk, // The clock

input rstn, // Reset

input write_op, // Write operations

input [7:0]write_data, // Data to be written

input read_op, // Read operations

output reg [7:0]read_data, // Read out data

input [7:0]addr, // Data address

output op_done, // End of operation

output reg scl, //scl

inout sda //sda

);state

Byte Write : START + DEVICE +ACK + ADDR + ACK + DATA + ACK + STOP

Random Read : START + DEVICE + ACK +ADDR + ACK+START + DEVICE + DATA + NO ACK + STOP

Each state uses 8 position 16 A decimal number means , Compare with the figure above SDA Data transmission on , Each bit of data transmission has a corresponding state , There are more waiting States .

parameter IDLE =8'h00,

WAIT_WTICK0=8'h01,

WAIT_WTICK1=8'h02,

W_START=8'h03,

W_DEVICE7=8'h04,

W_DEVICE6=8'h05,

W_DEVICE5=8'h06,

W_DEVICE4=8'h07,

W_DEVICE3=8'h08,

W_DEVICE2=8'h09,

W_DEVICE1=8'h0a,

W_DEVICE0=8'h0b,

W_DEVACK=8'h0c,

W_ADDRES7=8'h0d,

W_ADDRES6=8'h0e,

W_ADDRES5=8'h0f,

W_ADDRES4=8'h10,

W_ADDRES3=8'h11,

W_ADDRES2=8'h12,

W_ADDRES1=8'h13,

W_ADDRES0=8'h14,

W_AACK=8'h15,

W_DATA7=8'h16,

W_DATA6=8'h17,

W_DATA5=8'h18,

W_DATA4=8'h19,

W_DATA3=8'h1a,

W_DATA2=8'h1b,

W_DATA1=8'h1c,

W_DATA0=8'h1d,

W_DACK=8'h1e,

WAIT_WTICK3=8'h1f,

R_START=8'h20,

R_DEVICE7=8'h21,

R_DEVICE6=8'h22,

R_DEVICE5=8'h23,

R_DEVICE4=8'h24,

R_DEVICE3=8'h25,

R_DEVICE2=8'h26,

R_DEVICE1=8'h27,

R_DEVICE0=8'h28,

R_DACK=8'h29,

R_DATA7=8'h2a,

R_DATA6=8'h2b,

R_DATA5=8'h2c,

R_DATA4=8'h2d,

R_DATA3=8'h2e,

R_DATA2=8'h2f,

R_DATA1=8'h30,

R_DATA0=8'h31,

R_NOACK=8'h32,

S_STOP=8'h33,

S_STOP0=8'h34,

S_STOP1=8'h35,

W_OPOVER=8'h36;

reg [7:0]i2c,next_i; // current state , Next state SCL Sync

The frequency of the clock is very high , Reading and writing data cannot be carried out in a clock cycle , The time required for the device to respond and read and write is much longer than the clock cycle , Therefore use SCL The synchronization mode is the same Step timing .SCL The cycle is realized through the clock cycle .

One scl Period is 30 Clock cycles . Use div_cnt To record the number of clock cycles ,30 One cycle . The following are only time units Statement ,SCL The specific implementation of is shown below ↓.

SCL cycle :

|——————————

| ———————— |

clk0 clk7 clk15 clk22 clk29

scl_ls scl_lc scl_hs scl_hc scl_tick

reg [7:0]div_cnt; // Clock counter

wire scl_tick;

// Count , One clock cycle div_cnt+1

always @(posedge clk or negedge rstn)

if(!rstn) div_cnt <=8'd0;

else if((i2c==IDLE)|scl_tick) div_cnt <=8'd0;

else div_cnt<=div_cnt+1'b1;

//scl Time

wire scl_ls =(div_cnt==8'd0); //scl low

wire scl_lc = (div_cnt==8'd7); //scl low center

wire scl_hs =(div_cnt==8'd15); //scl high

wire scl_hc = (div_cnt==8'd22); //scl high center

assign scl_tick = (div_cnt==8'd29); // The end of a cycle

Status update

// state

always @(posedge clk or negedge rstn)

if(!rstn) i2c <=0;

else i2c <= next_i;Judgment of read and write commands

The read-write command is input through the port write_op and read_op affirmatory , These two signals are active at low level , It was used wr_op and rd_op Two registers put the input write_op and read_op Take the opposite , So if there is a read or write command ,wr_op or rd_op by 1, Reset and operation end (wr_opover) It should be cleared every time , Next use wr_op and rd_op Judge whether to read Yes , Here is just to replace the original low-level effective signal with two high-level effective signals .

reg wr_op,rd_op; // Read and write operations

always @ (posedge clk or negedge rstn)

if(!rstn) wr_op <= 0;

else if (i2c==IDLE) wr_op <= ~write_op;

else if(i2c==W_OPOVER) wr_op <=1'b0;

always @(posedge clk or negedge rstn)

if(!rstn) rd_op <= 0;

else if (i2c==IDLE) rd_op <= ~read_op;

else if(i2c==W_OPOVER) rd_op <=1'b0;

wire d5ms_over; // wait for

Judgment of the next state

Byte Write : START + DEVICE +ACK + ADDR + ACK + DATA + ACK + STOP

Random Read : START + DEVICE + ACK +ADDR + ACK+START + DEVICE + DATA + NO ACK + STOP

The next status update is in scl_tick( Every time 30 individual clk), The underlined parts above are the same , No matter reading or writing , At the beginning, the status updates are in accordance with the order underlined above Update the status in sequence , At this time, the device address is 10100000(write), here we are ADDR Of ACK, namely W_AACK According to wr_op and rd_op Decide what to enter next state ,wr_op Will start to state W_DATA Reading data ;rd_op Will arrive WAIT_WTICK3, Then continue to START. Wait for a signal after the operation d5ms_over To return to Free , The frequency of the controller should not be too high .

[email protected](*)

case (i2c)

IDLE: begin next_i = IDLE;if(wr_op|rd_op) next_i = WAIT_WTICK0;end // There are read and write operations that jump out of the idle state

//wait tick

WAIT_WTICK0:begin next_i = WAIT_WTICK0;if(scl_tick) next_i=WAIT_WTICK1;end

WAIT_WTICK1:begin next_i = WAIT_WTICK1;if(scl_tick) next_i = W_START;end

//START:SCL=1,SDA=1->0(scl_lc)

W_START:begin next_i=W_START;if(scl_tick) next_i=W_DEVICE7;end

//DEVICE ADDRESS(1010_000_0(WRITE))

W_DEVICE7:begin next_i = W_DEVICE7;if(scl_tick) next_i=W_DEVICE6;end

W_DEVICE6:begin next_i = W_DEVICE6;if(scl_tick) next_i=W_DEVICE5;end

W_DEVICE5:begin next_i = W_DEVICE5;if(scl_tick) next_i=W_DEVICE4;end

W_DEVICE4:begin next_i = W_DEVICE4;if(scl_tick) next_i=W_DEVICE3;end

W_DEVICE3:begin next_i = W_DEVICE3;if(scl_tick) next_i=W_DEVICE2;end

W_DEVICE2:begin next_i = W_DEVICE2;if(scl_tick) next_i=W_DEVICE1;end

W_DEVICE1:begin next_i = W_DEVICE1;if(scl_tick) next_i=W_DEVICE0;end

W_DEVICE0:begin next_i = W_DEVICE0;if(scl_tick) next_i=W_DEVACK;end

//ACK

W_DEVACK:begin next_i=W_DEVACK;if(scl_tick) next_i=W_ADDRES7;end

//WORD ADDRESS

W_ADDRES7 :begin next_i = W_ADDRES7;if(scl_tick) next_i=W_ADDRES6;end

W_ADDRES6 :begin next_i = W_ADDRES6;if(scl_tick) next_i=W_ADDRES5;end

W_ADDRES5 :begin next_i = W_ADDRES5;if(scl_tick) next_i=W_ADDRES4;end

W_ADDRES4 :begin next_i = W_ADDRES4;if(scl_tick) next_i=W_ADDRES3;end

W_ADDRES3 :begin next_i = W_ADDRES3;if(scl_tick) next_i=W_ADDRES2;end

W_ADDRES2 :begin next_i = W_ADDRES2;if(scl_tick) next_i=W_ADDRES1;end

W_ADDRES1 :begin next_i = W_ADDRES1;if(scl_tick) next_i=W_ADDRES0;end

W_ADDRES0 :begin next_i = W_ADDRES0;if(scl_tick) next_i=W_AACK;end

//ACK

W_AACK:begin next_i = W_AACK;

if(scl_tick&wr_op) next_i=W_DATA7; //wr_op Write the command , Start writing data

else if(scl_tick&rd_op) next_i=WAIT_WTICK3; //rd_op Read command , Then the next status is WAIT_WTICK3

end

//WRITE DATA[7:0]

W_DATA7:begin next_i=W_DATA7;if(scl_tick)next_i=W_DATA6;end

W_DATA6:begin next_i=W_DATA6;if(scl_tick)next_i=W_DATA5;end

W_DATA5:begin next_i=W_DATA5;if(scl_tick)next_i=W_DATA4;end

W_DATA4:begin next_i=W_DATA4;if(scl_tick)next_i=W_DATA3;end

W_DATA3:begin next_i=W_DATA3;if(scl_tick)next_i=W_DATA2;end

W_DATA2:begin next_i=W_DATA2;if(scl_tick)next_i=W_DATA1;end

W_DATA1:begin next_i=W_DATA1;if(scl_tick)next_i=W_DATA0;end

W_DATA0:begin next_i=W_DATA0;if(scl_tick)next_i=W_DACK;end

//ACK

W_DACK:begin next_i=W_DACK; if(scl_tick) next_i=S_STOP;end

//Current Address Read

//START: SCL=1,SDA=1->0(scl_lc)

WAIT_WTICK3:begin next_i=WAIT_WTICK3; if(scl_tick) next_i=R_START;end

R_START:begin next_i=R_START; if(scl_tick)next_i=R_DEVICE7;end

//DEVICE ADDRESS(1010_000_1(READ))

R_DEVICE7:begin next_i=R_DEVICE7; if(scl_tick) next_i=R_DEVICE6;end

R_DEVICE6:begin next_i=R_DEVICE6; if(scl_tick) next_i=R_DEVICE5;end

R_DEVICE5:begin next_i=R_DEVICE5; if(scl_tick) next_i=R_DEVICE4;end

R_DEVICE4:begin next_i=R_DEVICE4; if(scl_tick) next_i=R_DEVICE3;end

R_DEVICE3:begin next_i=R_DEVICE3; if(scl_tick) next_i=R_DEVICE2;end

R_DEVICE2:begin next_i=R_DEVICE2; if(scl_tick) next_i=R_DEVICE1;end

R_DEVICE1:begin next_i=R_DEVICE1; if(scl_tick) next_i=R_DEVICE0;end

R_DEVICE0:begin next_i=R_DEVICE0; if(scl_tick) next_i=R_DACK;end

//ACK

R_DACK:begin next_i=R_DACK;if(scl_tick) next_i=R_DATA7;end

//READ DATA[7:0], SDA:input

R_DATA7:begin next_i=R_DATA7;if(scl_tick) next_i=R_DATA6;end

R_DATA6:begin next_i=R_DATA6;if(scl_tick) next_i=R_DATA5;end

R_DATA5:begin next_i=R_DATA5;if(scl_tick) next_i=R_DATA4;end

R_DATA4:begin next_i=R_DATA4;if(scl_tick) next_i=R_DATA3;end

R_DATA3:begin next_i=R_DATA3;if(scl_tick) next_i=R_DATA2;end

R_DATA2:begin next_i=R_DATA2;if(scl_tick) next_i=R_DATA1;end

R_DATA1:begin next_i=R_DATA1;if(scl_tick) next_i=R_DATA0;end

R_DATA0:begin next_i=R_DATA0;if(scl_tick) next_i=R_NOACK;end

//NO ACK

R_NOACK:begin next_i=R_NOACK;if(scl_tick) next_i=S_STOP;end

//STOP

S_STOP:begin next_i=S_STOP;if(scl_tick) next_i=S_STOP0;end

S_STOP0:begin next_i=S_STOP0;if(scl_tick) next_i=S_STOP1;end

S_STOP1:begin next_i=S_STOP1;if(scl_tick) next_i=W_OPOVER;end

//WAIT write_op=0,read_op=0;

W_OPOVER:begin next_i = W_OPOVER;if(d5ms_over)next_i=IDLE;end // The operation ends and returns to the idle state

default:begin next_i= IDLE;end

endcaseSCL Synchronous implementation

Free , wait for , End of operation ,start Start waiting SCL It's all high , So you don't need clr_scl Yes SCL Zero clearing . in addition clr_scl Only in scl_ls(scl The low level of starts ) It's about Only place 1, hold scl clear 0, stay 15 individual clk Periodic scl_hs It's about , And then scl pull up , And that's what happened SCL cycle .

//SCL

assign clr_scl=scl_ls&(i2c!=IDLE)&(i2c!=WAIT_WTICK0)& //clr_scl,scl Set up 0 The signal

(i2c != WAIT_WTICK1)&(i2c!=W_START)&(i2c!=R_START)

&(i2c!=S_STOP0)&(i2c!=S_STOP1)&(i2c!=W_OPOVER);

always @(posedge clk or negedge rstn)

if(!rstn) scl <= 1'b1; // Reset ,scl High level

else if(clr_scl) scl <= 1'b0; //scl 1->0

else if(scl_hs) scl <=1'b1; //scl 0->1,high start,clk15SDA Realization

The second half of the code is SDA Part of the implementation , Because it's too long, analyze it paragraph by paragraph .

The following paragraph is to realize SDA Control signal declaration of , These signals are in the corresponding state and scl Set at the center of low level 1, tell SDA What to do ,i2c_reg For temporary storage scl On The data of ,i2c_rlf It is used when reading and writing data , The part to be used is in the next code .

//SDA

reg [7:0]i2c_reg;

assign start_clr = scl_lc &((i2c==W_START)|(i2c==R_START)); // stay scl low center Start reading and writing

assign ld_wdevice = scl_lc&(i2c==W_DEVICE7); // Load device address

assign ld_waddres = scl_lc&(i2c==W_ADDRES7); // Load data address

assign ld_wdata= scl_lc&(i2c==W_DATA7); // Load data

assign ld_rdevice = scl_lc&(i2c==R_DEVICE7); // Read the device address of the operation

assign noack_set = scl_lc&(i2c==R_NOACK) ; // Read operation finished , The host sends a response

assign stop_clr = scl_lc&(i2c==S_STOP);

assign stop_set = scl_lc&((i2c==S_STOP0)|(i2c==WAIT_WTICK3));

assign i2c_rlf =scl_lc&( // If there is reading and writing i2c_rlf

(i2c == W_DEVICE6)|

(i2c == W_DEVICE5)|

(i2c == W_DEVICE4)|

(i2c == W_DEVICE3)|

(i2c == W_DEVICE2)|

(i2c == W_DEVICE1)|

(i2c == W_DEVICE0)|

(i2c == W_ADDRES6)|

(i2c == W_ADDRES5)|

(i2c == W_ADDRES4)|

(i2c == W_ADDRES3)|

(i2c == W_ADDRES2)|

(i2c == W_ADDRES1)|

(i2c == W_ADDRES0)|

(i2c == W_DATA6)|

(i2c == W_DATA5)|

(i2c == W_DATA4)|

(i2c == W_DATA3)|

(i2c == W_DATA2)|

(i2c == W_DATA1)|

(i2c == W_DATA0)|

(i2c == R_DEVICE6)|

(i2c == R_DEVICE5)|

(i2c == R_DEVICE4)|

(i2c == R_DEVICE3)|

(i2c == R_DEVICE2)|

(i2c == R_DEVICE1)|

(i2c == R_DEVICE0));

The next step is to operate according to the control signal , Put the data of the corresponding operation into i2c_reg in , Prepare to SDA Online transmission ,i2c_rlf by 1 when i2creg Will move one bit to the left , because sda It is unit wide , Every time i2creg To sda On , So shift left is to send data one by one sda On .

[email protected](posedge clk or negedge rstn)

if(!rstn) i2c_reg <= 8'hff; // Reset , High level

else if(start_clr) i2c_reg <= 8'h00; // Start reading and writing ,sda Output

else if(ld_wdevice) i2c_reg <= {4'b1010,3'b000,1'b0}; //10100000 Write

else if(ld_waddres) i2c_reg <= addr; // Load data address

else if(ld_wdata) i2c_reg <= write_data; // Load the written data

else if(ld_rdevice) i2c_reg <= {4'b1010,3'b000,1'b1}; //10100001 read

else if(noack_set) i2c_reg <= 8'hff; //NOACK

else if(stop_clr) i2c_reg <= 8'h00;

else if(stop_set) i2c_reg <= 8'hff;

else if(i2c_rlf) i2c_reg <= {i2c_reg[6:0],1'b0}; // Move left Next is sda Output control ,sda Enable to write data address on the host , Data is 1, Enabling for 1 Time device depends on sda Output i2creg At the top of the table .NOACK Other than response signal , And read data , From the machine to sda Online , At this time, the host computer sda Enabling for 0, Data cannot be sent .2、TestBench Code instructions

assign sda_o = i2c_reg[7]; //sda

assign clr_sdaen = (i2c==IDLE)| //sda Enable set 0 The signal

(scl_lc&(

(i2c==W_DEVACK)|

(i2c==W_AACK)|

(i2c==W_DACK)|

(i2c==R_DACK)|

(i2c==R_DATA7)));

assign set_sdaen = scl_lc&( //sda Enable set 1 The signal

(i2c==WAIT_WTICK0)|

(i2c==W_ADDRES7)|

(i2c==W_DATA7)|

(i2c==WAIT_WTICK3)|

(i2c==S_STOP)|

(i2c==R_NOACK));

reg sda_en;

always @(posedge clk or negedge rstn)

if(!rstn) sda_en <= 0;

else if (clr_sdaen) sda_en <=0;

else if(set_sdaen) sda_en <= 1'b1;

assign sda= sda_en?sda_o: 1'bz; //sda Enabling for 1 when sda Can work

The following is the operation of reading data , use sda_wr control , stay scl Center of high level ( When the data is stable ) Go to read_data Read in the data , Move left to make up sda, One by one sda The hair Data updated read_data, At this time sda It's the slave sending data .

assign sda_wr = scl_hc &( // Reading data

(i2c==R_DATA7)|

(i2c==R_DATA6)|

(i2c==R_DATA5)|

(i2c==R_DATA4)|

(i2c==R_DATA3)|

(i2c==R_DATA2)|

(i2c==R_DATA1)|

(i2c==R_DATA0));

[email protected](posedge clk or negedge rstn)

if(!rstn) read_data <= 0;

else if(sda_wr) read_data <= {read_data[6:0],sda}; // Move left to read data

End of operation , wait for

The last is the waiting time after the operation ,d5ms_cnt Used to record the clock cycle , If you remember it, you will d5ms_over Set up 1, In the above part of state transition , The last to enter STOP shape What the state waits for is this signal , Wait until this signal ,I2C It's back to idle .

//op_done

assign op_done = (i2c == W_OPOVER); // End of operation

//Write Cycle(5ms)

//6MHZ = 166ns,5ms/166ns = 31

reg [12:0] d5ms_cnt;

always @(posedge clk or negedge rstn)

if(!rstn) d5ms_cnt <= 8'd0;

else if(i2c==IDLE) d5ms_cnt <= 8'd0;

else if(i2c==W_OPOVER) d5ms_cnt <= d5ms_cnt + 1'b1;

assign d5ms_over = (d5ms_cnt==13'h1FFF);Last , There is no ACK Part of the deal , Just when you should receive ACK From sda Read the signal , There was no judgment , Maybe it's left to the host .

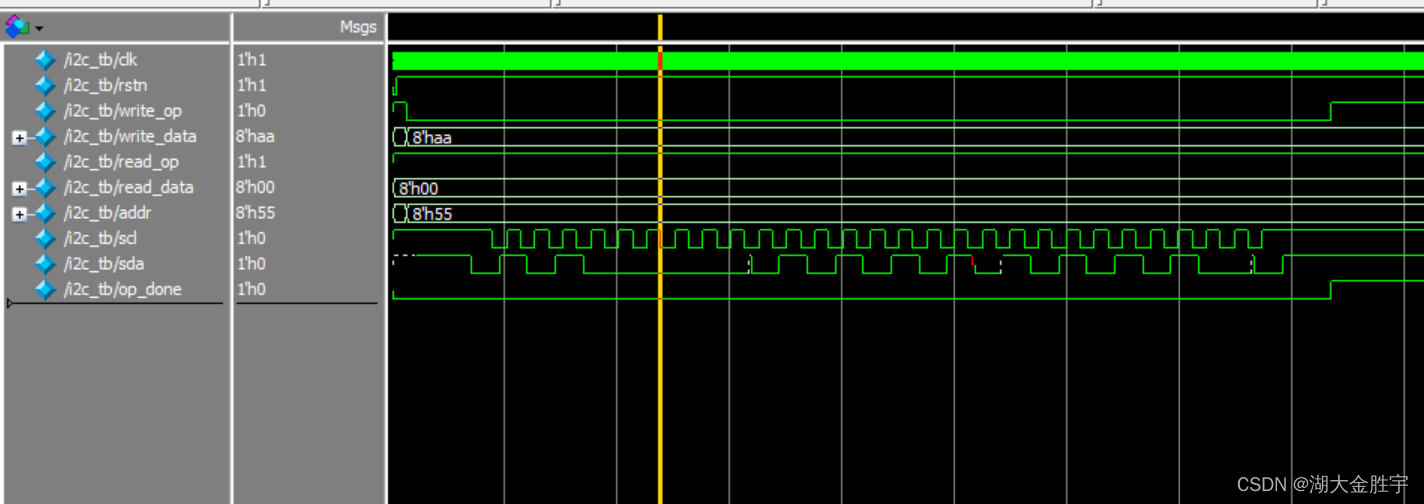

2、TestBench Code instructions

TestBench The main codes are as follows :

initial

begin

clk = 0;

rstn = 0;

write_op=1'b1;

write_data=8'h00;

read_op=1'b1;

addr=0;

repeat(5) @(posedge clk);

rstn = 1'b1;

end

initial

begin

wait(rstn);

repeat(10) @(posedge clk);

write_op=1'b0;

addr = 8'h55;

write_data= 8'haa;

wait(op_done);

write_op=1'b1;

$display ($stime/1,"ns","Write:Addr(%h)=(%h)\n",addr,write_data);

repeat(100)@(posedge clk);

read_op=1'b0;

addr = 8'h55;

wait(op_done);

read_op=1'b1;

$display ($stime/1,"ns","Write:Addr(%h)=(%h)\n",addr,read_data);

repeat(1000) @(posedge clk);

$stop;

endAccording to the code above , We can know that the read-write command is input through the port write_op and read_op affirmatory . So the program is written first and then read , The waveform should be the same .

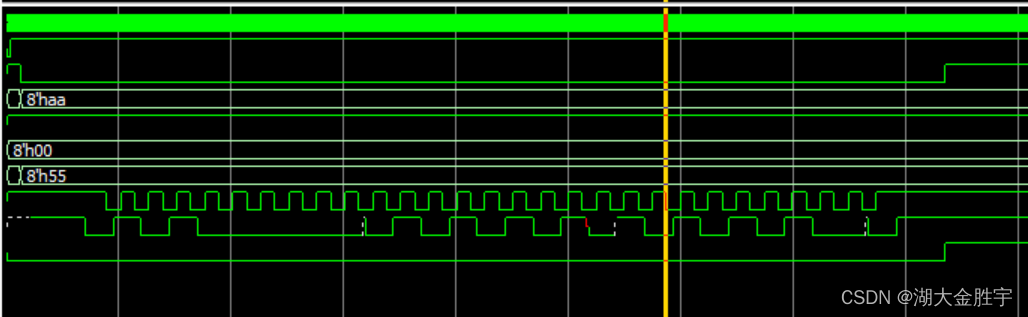

3、 Description of simulation waveform ( Screenshot + Text annotation )

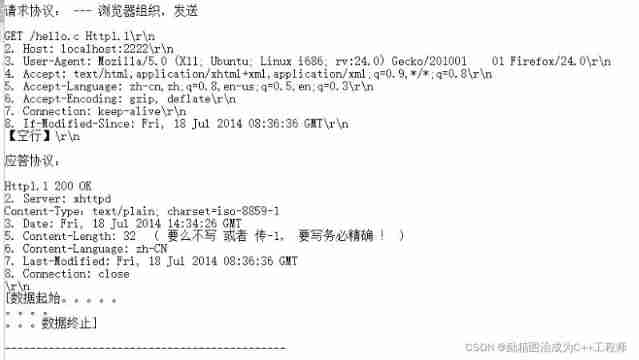

SCL For the high time ,SDA When it is the falling edge , The equipment starts working . First write the device address by the host , Then write the data address , After each write, the slave will reply with a ACK The signal indicates receipt . The device address is slave EEPROM The address of 1010000X,X by 0 Said to write ,1 Express reading , When writing the device address at the beginning ,X All are 0. Write operation , Next, you only need to send data from the host , From the machine ACK Response reply received .

Read it , Rewrite the device address , This time, X Namely 1 了 , It means that the data will be read next , Read data from the computer , The host will reply after receiving the data NOACK Send the data to the slave .

3、 ... and 、 Summary of the experiment

Through this experiment, I learned the following knowledge points :

- Master the description method of state machine ;

- Can write TestBench;

- It works ModelSim Conduct simulation ;

- master I2C Interface protocol ;

- Be able to better understand the reference design documents and test documents ;

- It works ModelSim Conduct simulation , Reasonably explain the function of each signal ;

- Use Quartus establish “EEPROM Read and write code ” engineering ;

Download validation "EEPROM Read and write code " function ;

After several experiments , Not only honed my will , Strengthened my faith , I believe we can also gain a lot in future experiments .

边栏推荐

- Mysql的事务

- MySQL development - advanced query - take a good look at how it suits you

- LeetCode#62. Different paths

- Global and Chinese market for antiviral coatings 2022-2028: Research Report on technology, participants, trends, market size and share

- Stc-b learning board buzzer plays music

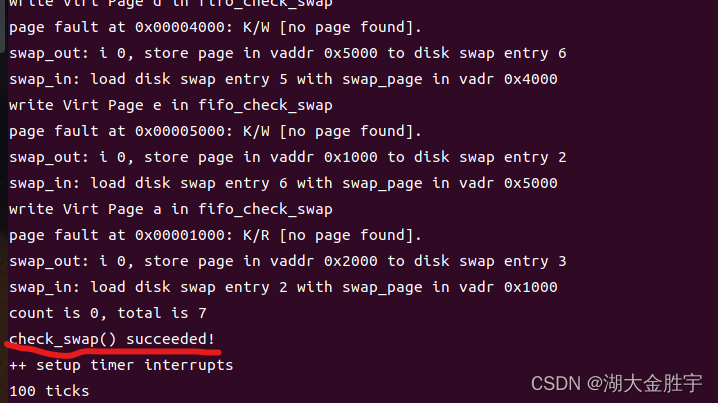

- ucore lab7

- CSAPP homework answers chapter 789

- ArrayList集合

- 安全测试入门介绍

- Rearrange spaces between words in leetcode simple questions

猜你喜欢

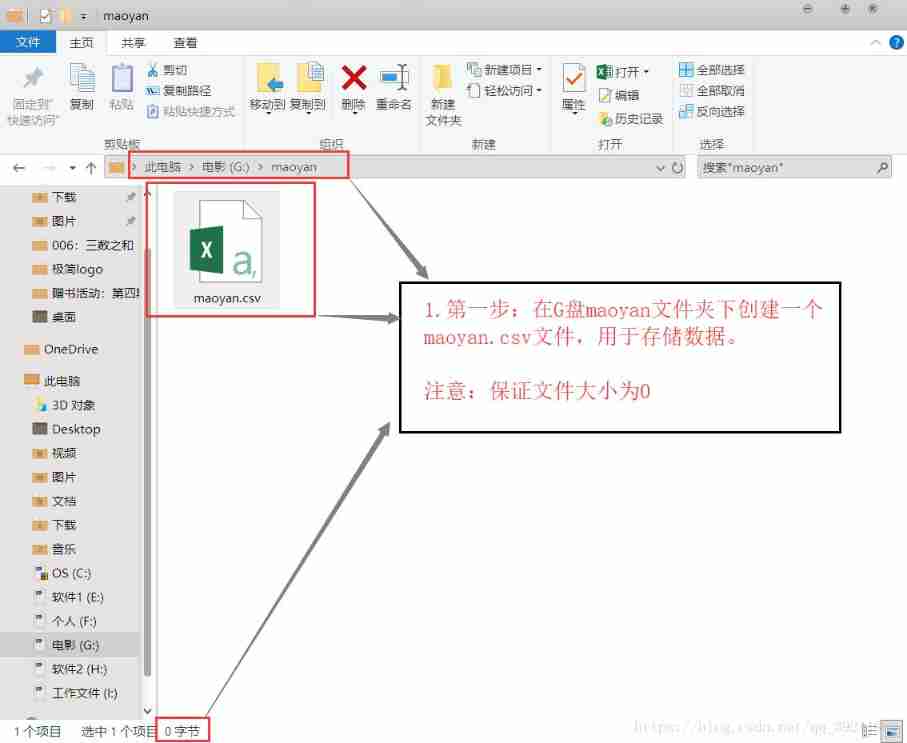

Crawling cat's eye movie review, data visualization analysis source code operation instructions

How to build a nail robot that can automatically reply

Leetcode simple question: check whether two strings are almost equal

遇到程序员不修改bug时怎么办?我教你

Want to change jobs? Do you know the seven skills you need to master in the interview software test

转行软件测试必需要知道的知识

软件测试有哪些常用的SQL语句?

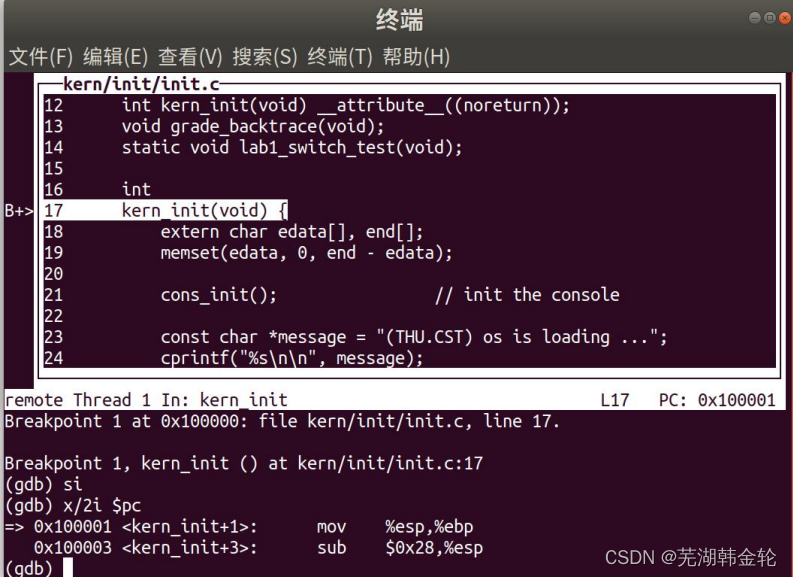

UCORE lab1 system software startup process experimental report

ucorelab3

Brief introduction to libevent

随机推荐

几款开源自动化测试框架优缺点对比你知道吗?

What is "test paper test" in software testing requirements analysis

Mysql database (II) DML data operation statements and basic DQL statements

[C language] twenty two steps to understand the function stack frame (pressing the stack, passing parameters, returning, bouncing the stack)

Stc-b learning board buzzer plays music

Collection collection and map collection

Take you to use wxpy to create your own chat robot (plus wechat interface basic data visualization)

Global and Chinese market of goat milk powder 2022-2028: Research Report on technology, participants, trends, market size and share

In Oracle, start with connect by prior recursive query is used to query multi-level subordinate employees.

What are the software testing methods? Show you something different

转行软件测试必需要知道的知识

MySQL transactions

Servlet

LeetCode#237. Delete nodes in the linked list

CSAPP家庭作業答案7 8 9章

Global and Chinese markets for GaN on diamond semiconductor substrates 2022-2028: Research Report on technology, participants, trends, market size and share

Practical cases, hand-in-hand teaching you to build e-commerce user portraits | with code

Leetcode notes - dynamic planning -day7

STM32学习记录:输入捕获应用

Crawler series (9): item+pipeline data storage