当前位置:网站首页>SPI and IIC communication protocol

SPI and IIC communication protocol

2022-07-05 02:53:00 【NaCl fish wulala】

One 、IIC

3.I2C agreement

I2C There are three status signals : Start signal 、 End signal and answer signal

Start signal :SCL For high voltage ,SDA Jump from high level to low level , Indicates the start of communication .

End signal :SCL For high voltage ,SDA Jump from low level to high level , End communication .

Answer signal : Receiving data IC After receiving a byte of data , Send data to IC To emit a specific low-level pulse , Indicates that data has been received .

In the process of data transmission ,SCL The clock is controlled by the main device ,SCL Read data when it is high SDA The data of ,SCL When it's low , Main equipment changes SDA The data of is ready to be transmitted to the next bit . Data is transmitted from high order , When transmitting 8 Behind you , The master device will release SDA Bus . If the data is received correctly from the device , Then the slave device will be pulled down SDA Bus , Then a reply signal is generated . If the slave device makes an error , Do not lower SDA Bus , Because of the pull-up resistance ,SDA The level of will become high , It is a non reply signal . Data transmission always starts with a start signal , Terminate the transmission with an end signal , Multiple bytes of data can be transmitted in the middle .

Two 、SPI

MOSI: Main device data output , Input data from the device .

SCK: Clock signal , It is controlled by the master .

NSS(CS): Select the signal from the device , Controlled by the main equipment . When NSS For low level, select slave device .

As follows, the master device communicates with multiple slave devices , among SCK,MOSI,MISO It's connected ,NSS Receive different IO Pin control . If the master device wants to communicate with the slave device, first pull down the corresponding slave device NSS Pin enable . Default state IO1,IO2,IO3 All high level , When master and slave devices 1 When communication , Pull it down IO1 Pin enable slave device 1. And slave devices 2,3 Do not enable , No response .

2.SPI Sequence diagram

Every time the transmission starts , The master device first pulls down the chip selection signal line of the slave device NSS, Select the slave device to be transmitted .SCK The clock line transmits one bit of data after sending a clock cycle .MOSI Main out from in , The data is controlled and sent by the main device , Receive from the device .MISO The data of is sent by the slave device , The main device receives . therefore SPI Transmitting a byte is equivalent to exchanging a byte between the master device and the slave device .

SPI There are only master mode and slave mode , There is no saying about reading and writing , Because essentially every time SPI It's the master-slave device exchanging data . in other words , If you send a data, you will receive a data ; If you want to receive a data, you must also send a data first .

According to the clock polarity (CPOL) And phase (CPHA) Different ,SPI There are four working modes .

Clock polarity (CPOL) Defines the clock idle state level :

CPOL=0 Low level when the clock is idle

CPOL=1 High level when the clock is idle

Clock phase (CPHA) Define the data collection time .

CPHA=0: At the first jump edge of the clock ( A rising or falling edge ) Data sampling .

CPHA=1: At the second jump edge of the clock ( A rising or falling edge ) Data sampling .

边栏推荐

- From task Run get return value - getting return value from task Run

- PHP cli getting input from user and then dumping into variable possible?

- el-select,el-option下拉选择框

- Elfk deployment

- SFTP cannot connect to the server # yyds dry goods inventory #

- Pytest (4) - test case execution sequence

- 看 TDengine 社区英雄线上发布会,听 TD Hero 聊开发者传奇故事

- Design and practice of kubernetes cluster and application monitoring scheme

- 返回二叉树中两个节点的最低公共祖先

- Yuan universe also "real estate"? Multiple second-hand trading websites block metauniverse keywords

猜你喜欢

Elk log analysis system

Character painting, I use characters to draw a Bing Dwen Dwen

为什么腾讯阿里等互联网大厂诞生的好产品越来越少?

Devtools的简单使用

![Moco V2 literature research [self supervised learning]](/img/bd/79b7b203ea064c65d143116c9f4dd0.jpg)

Moco V2 literature research [self supervised learning]

Elfk deployment

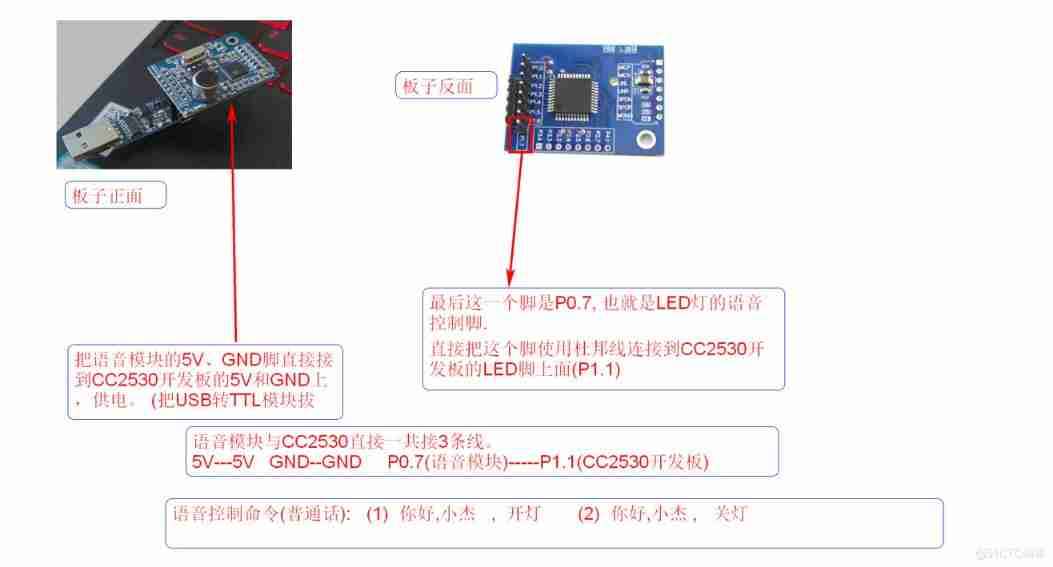

Yyds dry goods inventory intelligent fan based on CC2530 design

Pat class a 1160 forever (class B 1104 forever)

![[200 opencv routines] 99 Modified alpha mean filter](/img/df/1b7beb6746f416198fc405249852f8.jpg)

[200 opencv routines] 99 Modified alpha mean filter

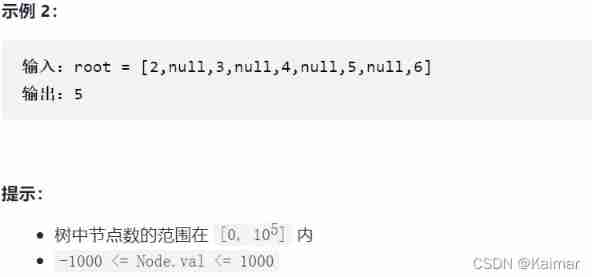

【LeetCode】111. Minimum depth of binary tree (2 brushes of wrong questions)

随机推荐

Daily question 2 12

【LeetCode】110. Balanced binary tree (2 brushes of wrong questions)

Sqoop command

Flume配置4——自定义MYSQLSource

The perfect car for successful people: BMW X7! Superior performance, excellent comfort and safety

ASP. Net core 6 framework unveiling example demonstration [01]: initial programming experience

Single box check box

Kotlin - coroutine

Anchor free series network yolox source code line by line explanation four (a total of ten, ensure line by line explanation, after reading, you can change the network at will, not just as a participan

d3js小记

1. Five layer network model

2.常见的请求方法

LeetCode146. LRU cache

【LeetCode】404. Sum of left leaves (2 brushes of wrong questions)

【LeetCode】98. Verify the binary search tree (2 brushes of wrong questions)

Azkaban actual combat

Anchor free series network yolox source code line by line explanation Part 2 (a total of 10, ensure to explain line by line, after reading, you can change the network at will, not just as a participan

openresty ngx_lua執行階段

The perfect car for successful people: BMW X7! Superior performance, excellent comfort and safety

[Yu Yue education] National Open University spring 2019 0505-22t basic nursing reference questions