当前位置:网站首页>SD_ DATA_ RECEIVE_ SHIFT_ REGISTER

SD_ DATA_ RECEIVE_ SHIFT_ REGISTER

2022-07-07 18:58:00 【Eight four one one】

Catalog

1. Interface

- Clock reset soft reset

- Status signals in_current_state

- sd The data signal from the card in_serial_data

- Data bit width in_data_width, decision 1 Line or 4 Line transmission

- accepted bit Count in_has_receive_bit

- sd The data signal sent sd_fifo_wdata,

- fifo Enable signal sd_fifo_we, At the end of collection 32bit Given after the parameter of

- crc Report an error out_receive_data_crc_error

input in_sd_clk; //clock for sd card

input hrst_n;

input in_soft_reset; //software reset

input [3:0] in_current_state; //surrent state of data fsm

input [3:0] in_serial_data; //data input from sd card

input in_data_width; //data width 1:4bit 0:1bit

input [13:0] in_has_receive_bit; //has received data bits

output [31:0] sd_fifo_wdata; //output parallel data to rx fifo

output sd_fifo_we; //host writes rx_fifo

output out_receive_data_crc_error; //receive data crc error flag

2. Internal signals

I 'll talk about it later

reg out_receive_data_crc_error;

reg sd_fifo_we;

reg [15:0] crc_reg0;

reg [15:0] crc_reg1;

reg [15:0] crc_reg2;

reg [15:0] crc_reg3;

reg [15:0] generate_crc_reg0;

reg [15:0] generate_crc_reg1;

reg [15:0] generate_crc_reg2;

reg [15:0] generate_crc_reg3;

reg [31:0] shift_reg;

reg out_write_receive_fifo;

3. Conversion of data bits

I think there are differences in the high and low positions , Here we need to bit Change the order of counting

assign sd_fifo_wdata = {

shift_reg[7:0],shift_reg[15:8],shift_reg[23:16],shift_reg[31:24]};

4.fifo Can make sd_fifo_we

- from out_write_receive_fifo One beat output

- When receiving parameters (32 position ) The following is given , It is equivalent to the operation of serial to parallel

always @(posedge in sd_clk or negedhe hrst_n) begin

if (!hrst_n)

sd_fifo_we <= 1'b0;

else if (!in_soft_reset)

sd_fifo_we <= 1'b0;

else

sd_fifo_we <= out_write_receive_fifo;

end

/----------------------------------------------------------

always @(*) begin

out_write_receive_fifo = 1'b0;

if (!in_data_width)

begin

if ((in_current_state == `DATA_STATE_RECEIVE) && (in_has_receive_bit[4:0] == 5'b11111))

out_write_receive_fifo = 1'b1;

end

else begin

if((in_current_state == `DATA_STATE_RECEIVE) && (in_has_receive_bit[2:0] == 3'b111))

out_write_receive_fifo = 1'b1;

end

end

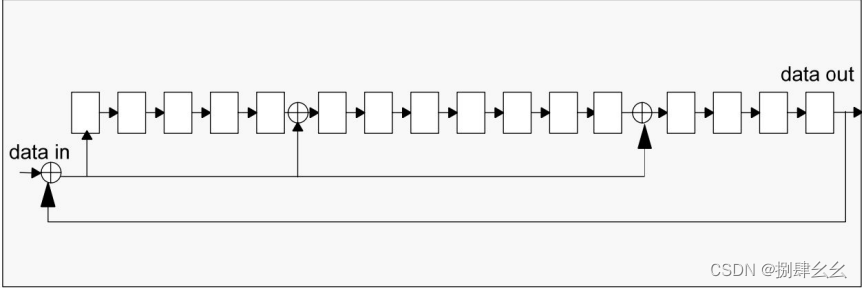

5. Parallel to serial

- Two cases , One line and four line transmission have different shifts

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

shift_reg <= 32'b0;

else if (!in_soft_reset)

shift_reg <= 32'b0;

else begin

if (in_current_state == `DATA_STATE_RECEIVE)

begin

if(!in_data_width)

shift_reg <= {

shift_reg[30:0],in_serial_data[0]};

else

shift_reg <= {

shift_reg[27:0],in_serial_data};

end

end

end

6. receive crc16

- Receive after receiving parameters crc16, It is also a series to parallel operation

always @(posedge in_sd_clk or negedge hrst_n)

if (!hrst_n)

begin

crc_reg0 <= 16'b0;

crc_reg1 <= 16'b0;

crc_reg2 <= 16'b0;

crc_reg3 <= 16'b0;

end

else if (in_soft_reset)

begin

crc_reg0 <= 16'b0;

crc_reg1 <= 16'b0;

crc_reg2 <= 16'b0;

crc_reg3 <= 16'b0;

end

else if ((in_current_state == `DATA_STATE_RECEIVE_END_BIT))

begin

crc_reg0 <= 16'b0;

crc_reg1 <= 16'b0;

crc_reg2 <= 16'b0;

crc_reg3 <= 16'b0;

end

else if (in_current_state == `DATA_STATE_RECEIVE_CRC)

begin

if(in_data_width == 1'b0)

crc_reg0 <= {

crc_reg0[14:0],in_serial_data[0]};

else begin

crc_reg0 <= {

crc_reg0[14:0],in_serial_data[0]};

crc_reg1 <= {

crc_reg1[14:0],in_serial_data[1]};

crc_reg2 <= {

crc_reg2[14:0],in_serial_data[2]};

crc_reg3 <= {

crc_reg3[14:0],in_serial_data[3]};

end

end

end

7. Calculate for yourself crc16

- The method is the same as before cmd Module crc7 similar

- Mainly doing XOR operations

- Remember to count together while receiving crc16

always @(posedge in_sd_clk or negedge hrst_n) begin

if (!hrst_n)

begin

generate_crc_reg0 <= 16'b0;

generate_crc_reg1 <= 16'b0;

generate_crc_reg2 <= 16'b0;

generate_crc_reg3 <= 16'b0;

end

else if (!in_soft_reset)

begin

generate_crc_reg0 <= 16'b0;

generate_crc_reg1 <= 16'b0;

generate_crc_reg2 <= 16'b0;

generate_crc_reg3 <= 16'b0;

end

else if ((in_current_state == `DATA_STATE_RECEIVE_END_BIT))

begin

generate_crc_reg0 <= 16'b0;

generate_crc_reg1 <= 16'b0;

generate_crc_reg2 <= 16'b0;

generate_crc_reg3 <= 16'b0;

end

else if (in_current_state == `DATA_STATE_RECEIVE)

begin

if (in_data_width == 1'b0)

begin

generate_crc_reg0[0] <= in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[1] <= generate_crc_reg0[0];

generate_crc_reg0[2] <= generate_crc_reg0[1];

generate_crc_reg0[3] <= generate_crc_reg0[2];

generate_crc_reg0[4] <= generate_crc_reg0[3];

generate_crc_reg0[5] <= generate_crc_reg0[4] ^ in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[6] <= generate_crc_reg0[5];

generate_crc_reg0[7] <= generate_crc_reg0[6];

generate_crc_reg0[8] <= generate_crc_reg0[7];

generate_crc_reg0[9] <= generate_crc_reg0[8];

generate_crc_reg0[10] <= generate_crc_reg0[9];

generate_crc_reg0[11] <= generate_crc_reg0[10];

generate_crc_reg0[12] <= generate_crc_reg0[11] ^ in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[13] <= generate_crc_reg0[12];

generate_crc_reg0[14] <= generate_crc_reg0[13];

generate_crc_reg0[15] <= generate_crc_reg0[14];

end

else begin

generate_crc_reg0[0] <= in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[1] <= generate_crc_reg0[0];

generate_crc_reg0[2] <= generate_crc_reg0[1];

generate_crc_reg0[3] <= generate_crc_reg0[2];

generate_crc_reg0[4] <= generate_crc_reg0[3];

generate_crc_reg0[5] <= generate_crc_reg0[4] ^ in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[6] <= generate_crc_reg0[5];

generate_crc_reg0[7] <= generate_crc_reg0[6];

generate_crc_reg0[8] <= generate_crc_reg0[7];

generate_crc_reg0[9] <= generate_crc_reg0[8];

generate_crc_reg0[10] <= generate_crc_reg0[9];

generate_crc_reg0[11] <= generate_crc_reg0[10];

generate_crc_reg0[12] <= generate_crc_reg0[11] ^ in_serial_data[0] ^ generate_crc_reg0[15];

generate_crc_reg0[13] <= generate_crc_reg0[12];

generate_crc_reg0[14] <= generate_crc_reg0[13];

generate_crc_reg0[15] <= generate_crc_reg0[14];

generate_crc_reg1[0] <= in_serial_data[1] ^ generate_crc_reg1[15];

generate_crc_reg1[1] <= generate_crc_reg1[0];

generate_crc_reg1[2] <= generate_crc_reg1[1];

generate_crc_reg1[3] <= generate_crc_reg1[2];

generate_crc_reg1[4] <= generate_crc_reg1[3];

generate_crc_reg1[5] <= generate_crc_reg1[4] ^ in_serial_data[1] ^ generate_crc_reg1[15];

generate_crc_reg1[6] <= generate_crc_reg1[5];

generate_crc_reg1[7] <= generate_crc_reg1[6];

generate_crc_reg1[8] <= generate_crc_reg1[7];

generate_crc_reg1[9] <= generate_crc_reg1[8];

generate_crc_reg1[10] <= generate_crc_reg1[9];

generate_crc_reg1[11] <= generate_crc_reg1[10];

generate_crc_reg1[12] <= generate_crc_reg1[11] ^ in_serial_data[1] ^ generate_crc_reg1[15];

generate_crc_reg1[13] <= generate_crc_reg1[12];

generate_crc_reg1[14] <= generate_crc_reg1[13];

generate_crc_reg1[15] <= generate_crc_reg1[14];

generate_crc_reg2[0] <= in_serial_data[2] ^ generate_crc_reg2[15];

generate_crc_reg2[1] <= generate_crc_reg2[0];

generate_crc_reg2[2] <= generate_crc_reg2[1];

generate_crc_reg2[3] <= generate_crc_reg2[2];

generate_crc_reg2[4] <= generate_crc_reg2[3];

generate_crc_reg2[5] <= generate_crc_reg2[4] ^ in_serial_data[2] ^ generate_crc_reg2[15];

generate_crc_reg2[6] <= generate_crc_reg2[5];

generate_crc_reg2[7] <= generate_crc_reg2[6];

generate_crc_reg2[8] <= generate_crc_reg2[7];

generate_crc_reg2[9] <= generate_crc_reg2[8];

generate_crc_reg2[10] <= generate_crc_reg2[9];

generate_crc_reg2[11] <= generate_crc_reg2[10];

generate_crc_reg2[12] <= generate_crc_reg2[11] ^ in_serial_data[2] ^ generate_crc_reg2[15];

generate_crc_reg2[13] <= generate_crc_reg2[12];

generate_crc_reg2[14] <= generate_crc_reg2[13];

generate_crc_reg2[15] <= generate_crc_reg2[14];

generate_crc_reg3[0] <= in_serial_data[3] ^ generate_crc_reg3[15];

generate_crc_reg3[1] <= generate_crc_reg3[0];

generate_crc_reg3[2] <= generate_crc_reg3[1];

generate_crc_reg3[3] <= generate_crc_reg3[2];

generate_crc_reg3[4] <= generate_crc_reg3[3];

generate_crc_reg3[5] <= generate_crc_reg3[4] ^ in_serial_data[3] ^ generate_crc_reg3[15];

generate_crc_reg3[6] <= generate_crc_reg3[5];

generate_crc_reg3[7] <= generate_crc_reg3[6];

generate_crc_reg3[8] <= generate_crc_reg3[7];

generate_crc_reg3[9] <= generate_crc_reg3[8];

generate_crc_reg3[10] <= generate_crc_reg3[9];

generate_crc_reg3[11] <= generate_crc_reg3[10];

generate_crc_reg3[12] <= generate_crc_reg3[11] ^ in_serial_data[3] ^ generate_crc_reg3[15];

generate_crc_reg3[13] <= generate_crc_reg3[12];

generate_crc_reg3[14] <= generate_crc_reg3[13];

generate_crc_reg3[15] <= generate_crc_reg3[14];

end

end

end

8. Compare crc16

- stay DATA_STATE_RECEIVE_END_BIT state , To receive crc16 And calculated by yourself crc16 Contrast

- Different is wrong

always @(*) begin

out_receive_data_crc_error = 1'b0;

if(!in_data_width)

begin

if ((in_current_state == `DATA_STATE_RECEIVE_END_BIT) && !(crc_reg0 == generate_crc_reg0))

out_receive_data_crc_error = 1'b1;

end

else begin

if((in_current_state == `DATA_STATE_RECEIVE_END_BIT) &&

(!(crc_reg0 == generate_crc_reg0) ||

!(crc_reg1 == generate_crc_reg1) ||

!(crc_reg2 == generate_crc_reg2) ||

!(crc_reg3 == generate_crc_reg3) )

out_receive_data_crc_error = 1'b1;

end

end

边栏推荐

- [unity shader] insert pass to realize the X-ray perspective effect of model occlusion

- Tsinghua, Cambridge and UIC jointly launched the first Chinese fact verification data set: evidence-based, covering many fields such as medical society

- Continuous test (CT) practical experience sharing

- Three forms of multimedia technology commonly used in enterprise exhibition hall design

- Summary of debian10 system problems

- Complete e-commerce system

- 体总:安全有序恢复线下体育赛事,力争做到国内赛事应办尽办

- Interview vipshop internship testing post, Tiktok internship testing post [true submission]

- socket编程之常用api介绍与socket、select、poll、epoll高并发服务器模型代码实现

- Will domestic software testing be biased

猜你喜欢

6.关于jwt

![Learn open62541 -- [67] add custom enum and display name](/img/98/e5e25af90b3f98c2be11d7d21e5ea6.png)

Learn open62541 -- [67] add custom enum and display name

C语言中匿名的最高境界

Summary of debian10 system problems

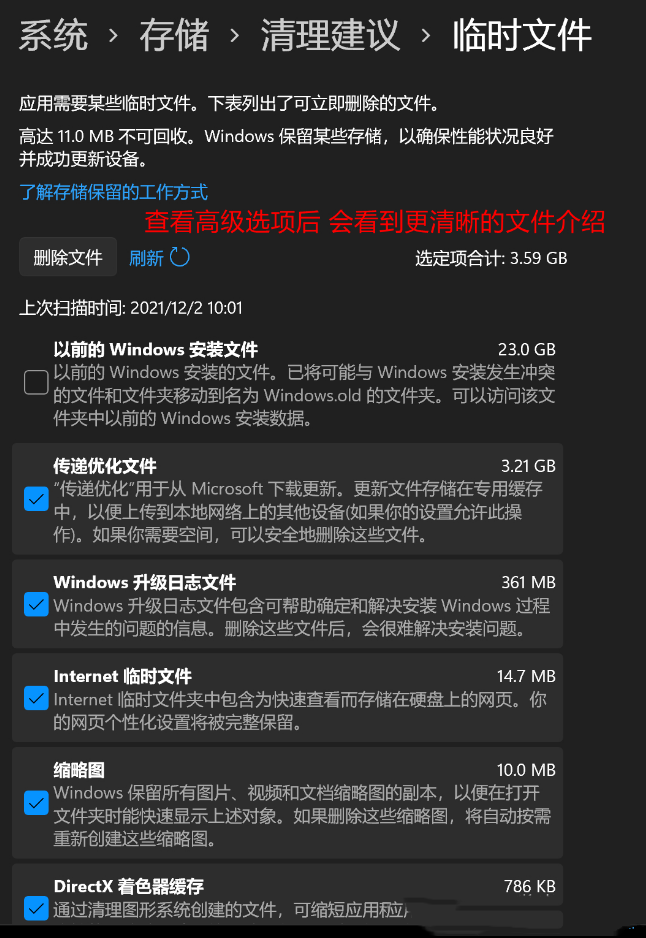

How to clean when win11 C disk is full? Win11 method of cleaning C disk

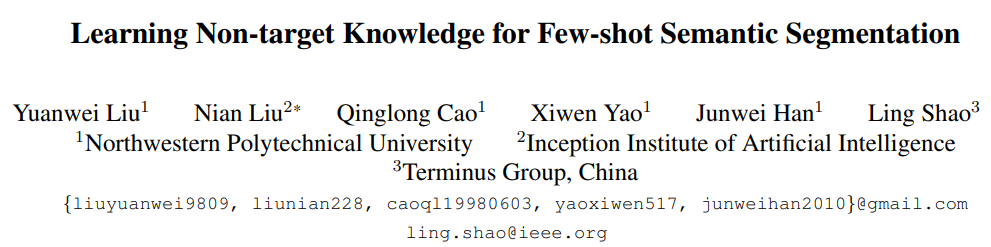

CVPR 2022 - learning non target knowledge for semantic segmentation of small samples

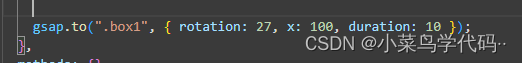

GSAP animation library

![[Tawang methodology] Tawang 3W consumption strategy - U & a research method](/img/63/a8c08ac6ec7d654159e5fc8b4423e4.png)

[Tawang methodology] Tawang 3W consumption strategy - U & a research method

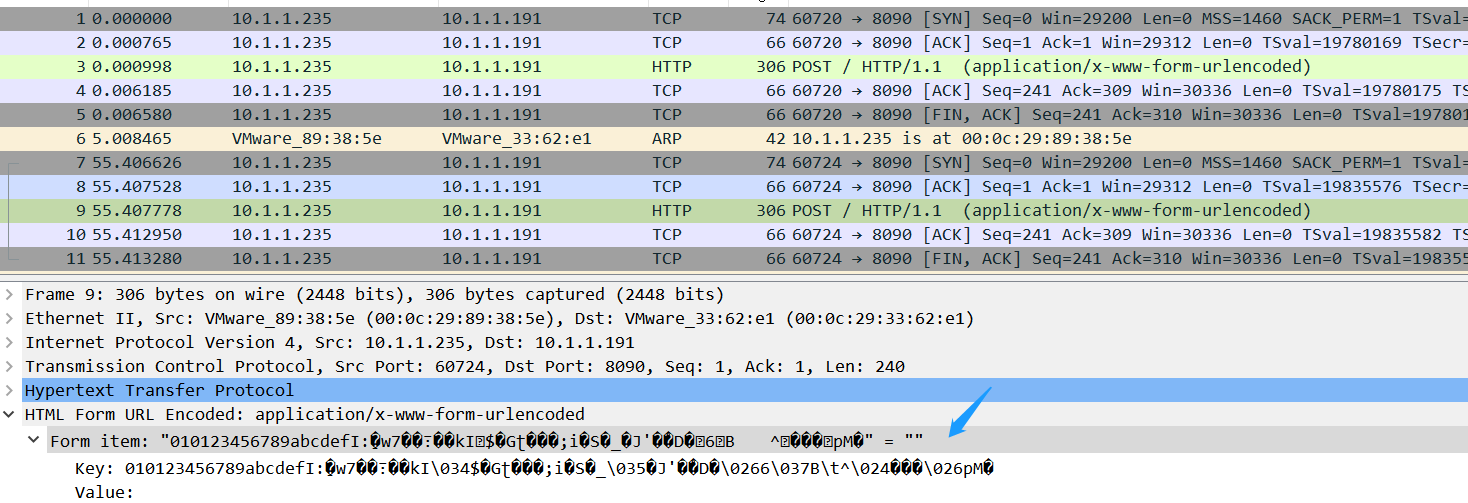

Wireshark分析抓包数据*.cap

【C语言】字符串函数

随机推荐

socket編程之常用api介紹與socket、select、poll、epoll高並發服務器模型代碼實現

Recommend free online SMS receiving platform in 2022 (domestic and foreign)

云安全日报220707:思科Expressway系列和网真视频通信服务器发现远程攻击漏洞,需要尽快升级

线程池中的线程工厂

2022-07-04 matlab读取视频帧并保存

The moveposition function of rigidbody2d of unity2d solves the problem of people or screen jitter when moving

单臂路由和三层交换的简单配置

Yunjing network technology interview question [Hangzhou multi tester] [Hangzhou multi tester _ Wang Sir]

Desci: is decentralized science the new trend of Web3.0?

2022年理财产品的一般收益率是多少?

C语言中匿名的最高境界

Wechat web debugging 8.0.19 replace the X5 kernel with xweb, so the X5 debugging method can no longer be used. Now there is a solution

Calculation of torque target value (ftorque) in servo torque control mode

Nunjuks template engine

Idea completely uninstalls installation and configuration notes

PIP related commands

强化学习-学习笔记8 | Q-learning

Kirk Borne的本周学习资源精选【点击标题直接下载】

嵌入式面试题(算法部分)

【Unity Shader】插入Pass实现模型遮挡X光透视效果