当前位置:网站首页>Basic analysis of IIC SPI protocol

Basic analysis of IIC SPI protocol

2022-07-05 04:20:00 【Number and form】

IIC Protocol Brief

IIC Protocol is a kind of communication protocol , Serial communication protocol , Half duplex communication , It can make mcu Communicate with other peripherals , It can be attached to multiple hosts and slaves , Only one master and one slave can communicate each time .iic There are two buses ,SCL Bus ( Serial clock line ) Used for clock synchronization sending and receiving ,SDA Bus ( Bidirectional serial data line ) Used for sending and receiving data . To realize the communication of equipment, we must first know the independent address of the equipment , Generally, this address is in the equipment manual. You can know by referring to the equipment manual , The address is 7 Bit address and 10 Bit address , In general, it is 7 Bit address ,IIC Device reading and writing ( Transmission direction selection bit ) With equipment 7 The bit address forms a new 8 Bit address , Reading is 1, Write is 0. for example ,EEPROM The device address format of is 1010XXX, If the address of a device is 1010 000 namely 0x50, And the transmission direction selection bit form a new 8 Bit address .1010 0000 (0xA0) Device address ,1010 0001(0xA1) Device read address .

IIC The pin mode of must use open drain mode GPIO_Mode_AF_OD

IIC Basic process of reading and writing

1: Generate the starting signal (SCL Keep it high ,SDA After changing from high level to low level , Time delay (>4.7us),SCL change Low level )

2: Address of broadcasting equipment + Transmission direction selection bit

3: Wait for the answer signal .

4: send data ( byte )(1 Bytes to 8bit)

5: Wait for the answer signal

6: Repeat sending data (4,5)

7: Stop signal (SCL Keep it high .SDA Change from low level to high level )

Transmission rate : Configure in initialization ,

Yes in standard mode 100kbit/s,

In fast mode 400kbit/s,

High speed mode 3.4Mbit/s

IIC The advantages of the agreement :

You can add multiple slave devices ( Connected to the same bus IC The number is affected by the maximum capacitance of the bus 400pF Limit . ), Only two buses occupy less resources , Fault diagnosis and debugging are simple

SPI Introduction to communication protocol :

A serial peripheral interface , It is a high-speed full duplex communication bus , It is widely used in ADC、LCD And so on MCU between , Where high communication speed is required . There is usually only one host , There are multiple slaves , There are three buses between master and slave , A piece of film chooses a line . Three buses are connected in parallel between various devices , The chip selection line is connected in series between the master and the slave .

The three buses are :

SCK( Clock signal line ): For communication data synchronization , Generated by the communication host , Determines the rate of communication .

MOSI( Main device output / Input from the device ): The data of the host is output by this line , The data of the slave is input by this line

MISO( Master input / Output from the device ): The host reads data from this signal line , The data of the slave is output to the host by this signal line

Film selection line :CS/NSS

How many slave devices are connected to the host , How many film selection lines are there , Each device has an independent film selection line ,spi The device has no device address , By pulling down CS As the start signal of device communication ,CS Pull up as the end signal of equipment communication .

SPI There are four communication modes (SPI0,SPI1,SPI2,SPI3), The main difference between them is that when the bus is idle SCK The clock state and the sampling time of data , Through different clock polarities CPOL And clock phase CPHA To set up

Clock polarity CPOL Refer to SPI When the communication device is idle ,SCK The level signal of the signal line , namely SPI Before communication starts 、 NSS The line is at high level SCK The state of ,SCK Low level in idle state ,CPOL=1 when , contrary .

Clock phase CPHA It refers to the sampling time of data , When CPHA=0 when ,MOSI or MISO The signal on the data line will be SCK Clock line “ Odd edge ” Be sampled . When CPHA=1 when , The data line is in SCK Of “ Even edge ” sampling

SPI Main mode receiving and sending process

1: control NSS The signal line , Generate the starting signal

2: Write the data to be sent to “ Data register DR” in , The data is stored in the send buffer

3: Communication begins ,SCK The clock starts to run .MOSI The data in the transmit buffer is transmitted bit by bit ;MISO The data is stored bit by bit in the receive buffer ;

4: When one frame of data is sent ,“ Status register SR” Medium “TXE Sign a ” Will be placed 1, It means that one frame has been transmitted , Send buffer is empty ; Similarly , When receiving a frame of data ,“RXNE Sign a ” Will be placed 1, It means that one frame has been transmitted , The receive buffer is not empty ;

5: Waiting to arrive “TXE Sign a ” by 1 when , To continue sending data , Then go to “ Data register DR” Write data ; Waiting to arrive “RXNE Sign a ” by 1 when , By reading the “ Data register DR” You can get the contents of the receive buffer .

SPI The transmission rate of is affected by

1:SPI Maximum clock frequency

2:CPU Handle SPI The power of data

3:pcb The maximum transmission rate allowed

SPI The maximum clock frequency of is spi Set in initialization SPI_BaudRatePrescaler , Set baud rate frequency division factor , The clock after frequency division is SPI Of SCK Clock frequency of signal line . This member parameter can be set to fpclk Of 2、4、6、8、16、32、64、128、256 frequency division . The biggest is 2 Frequency division clock frequency , Accessible 50Mbps.stm32f103ve The serial clock frequency is 72M

So the biggest spi Transmission rate up to 36Mbit/s

边栏推荐

猜你喜欢

SPI read / write flash principle + complete code

如何实现实时音视频聊天功能

On the day 25K joined Tencent, I cried

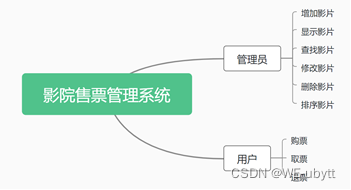

C language course setting: cinema ticket selling management system

How to get the first few pieces of data of each group gracefully

![[phantom engine UE] only six steps are needed to realize the deployment of ue5 pixel stream and avoid detours! (the principles of 4.26 and 4.27 are similar)](/img/eb/a93630aff7545c6c3b71dcc9f5aa61.png)

[phantom engine UE] only six steps are needed to realize the deployment of ue5 pixel stream and avoid detours! (the principles of 4.26 and 4.27 are similar)

如何优雅的获取每个分组的前几条数据

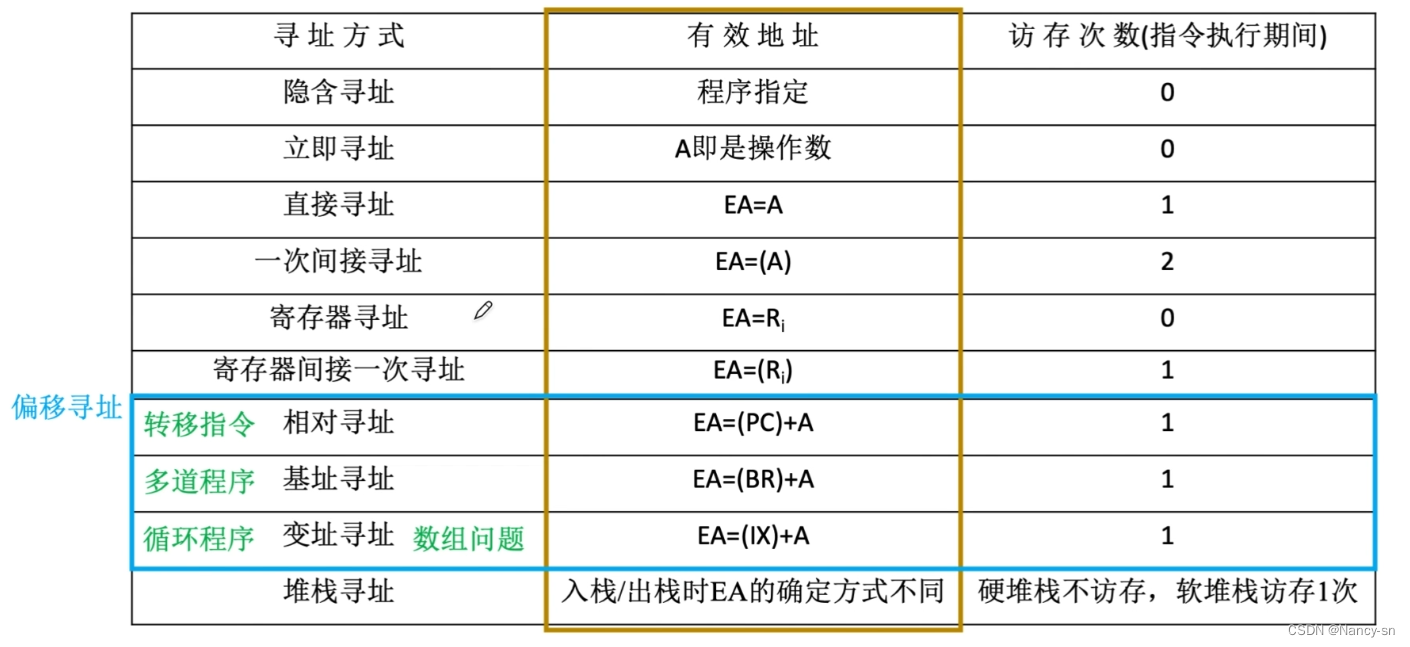

10种寻址方式之间的区别

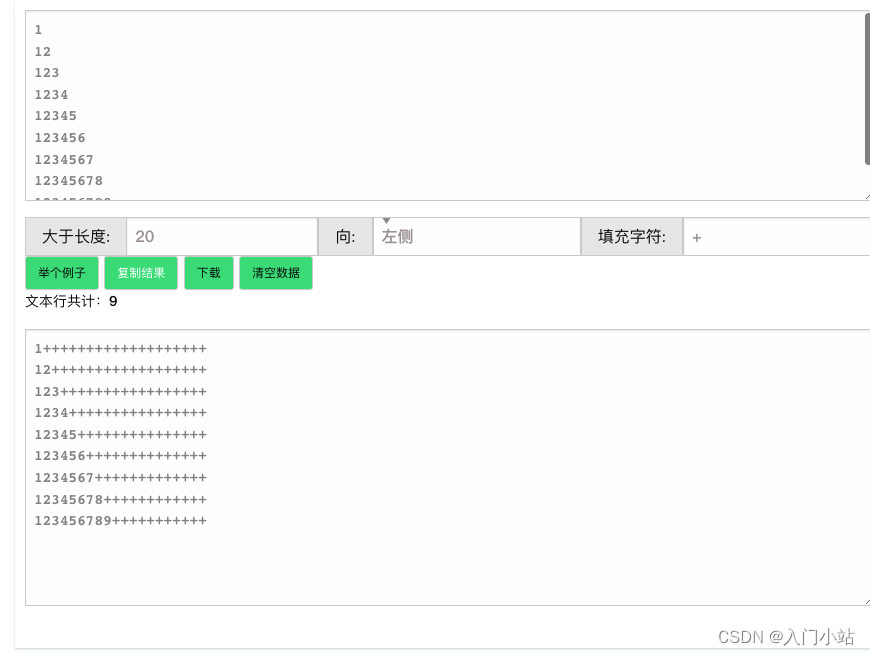

Online text line fixed length fill tool

Uni app change the default component style

随机推荐

防护电路中的元器件

Here comes the Lantern Festival red envelope!

Technical tutorial: how to use easydss to push live streaming to qiniu cloud?

Alibaba cloud ECS uses cloudfs4oss to mount OSS

[brush questions] BFS topic selection

Sequelize. JS and hasmany - belongsto vs hasmany in serialize js

Convert Boolean to integer value PHP - Convert Boolean to integer value PHP

Decimal to hexadecimal

How to solve the problem that easycvr changes the recording storage path and does not generate recording files?

【thingsboard】替换首页logo的方法

A应用唤醒B应该快速方法

kubernetes集群之调度系统

【虚幻引擎UE】打包报错出现!FindPin错误的解决办法

How to get the first few pieces of data of each group gracefully

level18

JVM garbage collection

Behavior perception system

C language course setting: cinema ticket selling management system

open graph协议

[phantom engine UE] only six steps are needed to realize the deployment of ue5 pixel stream and avoid detours! (the principles of 4.26 and 4.27 are similar)