当前位置:网站首页>Arm pc=pc+8 is the most understandable explanation

Arm pc=pc+8 is the most understandable explanation

2022-07-06 12:01:00 【csdndulala】

https://www.cnblogs.com/douzi2/p/4934202.html

Why is “PC = PC + 8”;

“PC = PC + 8” In fact, it's easy to get confused by writing like this .“PC = PC + 8” The real meaning should be :

Code address of execution place = PC - 8;

in other words ,”PC Address to “ leading “ Code address of execution place ”8 Bytes ;

in other words “PC = PC + 8” Second of PC, Actually, it means “ Code address of execution place ”

then , Understand why 8?

First ,arm The address width of is 4 Bytes , So every instruction executed ,PC It will add itself 4.

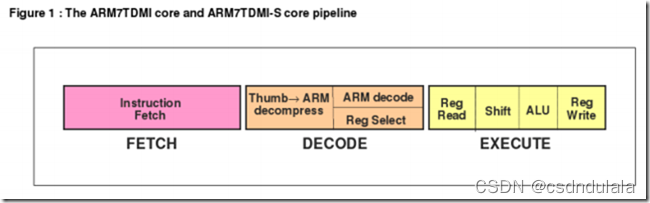

And an instruction must be completely arm absorption , It takes multiple steps , take arm7 For example, it adopts 3 Stage assembly line technology .

Assembly line , For our kind of play FPGA I can't be more familiar with , With 3 For the stage assembly line , Is to divide one thing into 3 A step , Each step is processed at the same time ,

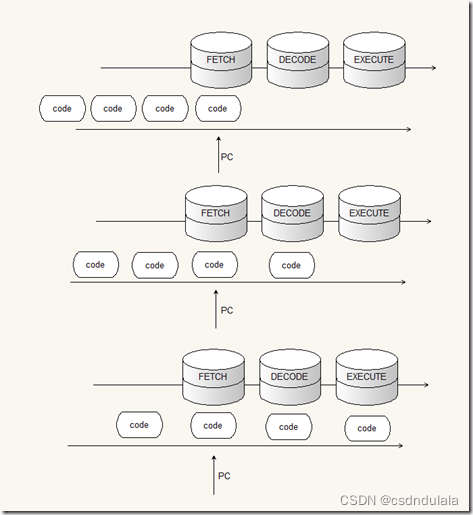

The first two cycles are incubation period , Unable to produce results , After that, the results will continue to output .

Imagine , Instructions , Like products waiting to be processed , Running on the conveyor belt , and “FETCH”,“DECODE”,“EXECUTE”, Namely 3 A processing procedure .

1、 In the first cycle ,PC Point to the first program instruction , Carry out the value (FETCH),DECODE, and EXECUTE step “ In the air ”

2、 In the second cycle , next PC + 4,PC Point to the second program instruction to take value (FETCH),DECODE Processed in one cycle ,FETCH Instructions to ,EXECUTE Throw yourself into the air again .

3、 In the third cycle , still PC + 4,PC Point to the third program instruction to take value (FETCH),DECODE Processed in two cycles ,FETCH Instructions to ,

EXECUTE At this time , Processing in one cycle FETCH Instructions to , This instruction is also in the second cycle DECODE Instructions .

4、 Then every clock cycle ,EXECUTE It can be processed twice code, however PC Always ahead of it , That is to say : Code address of execution place = PC - 8;

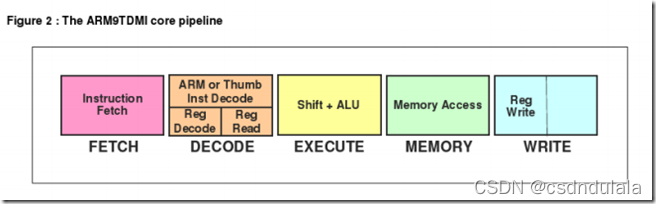

and ARM9 By increasing the number of assembly lines , It simplifies the logic at all levels of the pipeline , Further improve the performance of the processor . use 5 Stage assembly line technology , But it's also “PC = PC + 8”,

Why is that ? Let's take a look at the picture :

We found that EXECUTE Still in the third step , And conform to : Code address of execution place = PC - 8; As long as you understand this, it's enough to read the code .

边栏推荐

猜你喜欢

Gallery之图片浏览、组件学习

Fashion-Gen: The Generative Fashion Dataset and Challenge 论文解读&数据集介绍

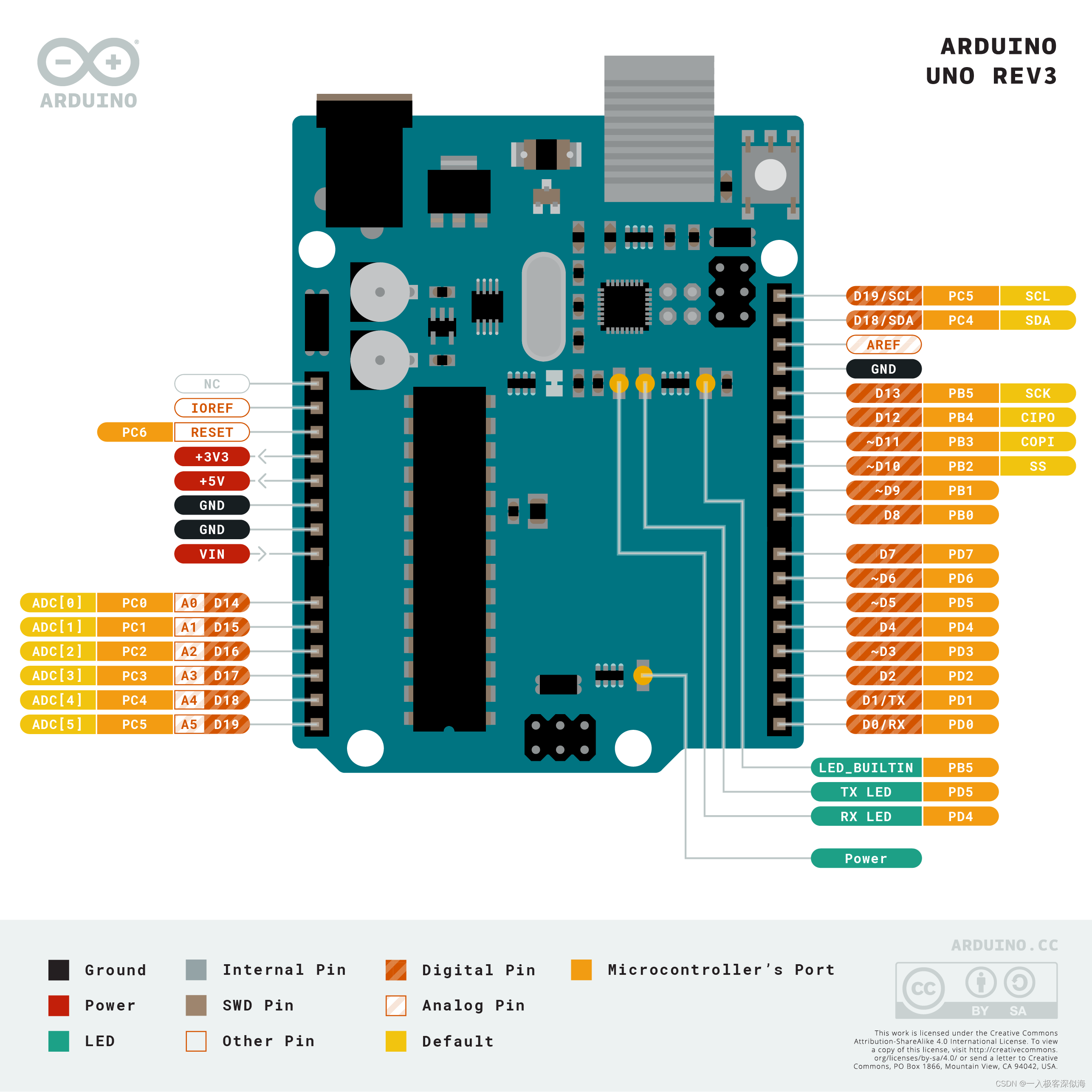

arduino UNO R3的寄存器写法(1)-----引脚电平状态变化

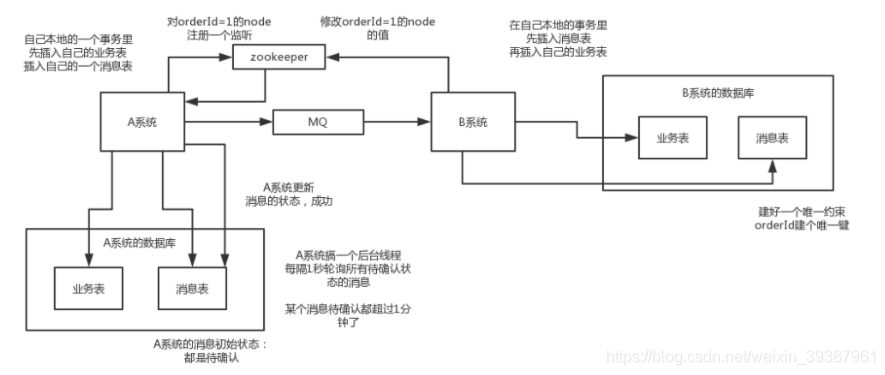

Implementation scheme of distributed transaction

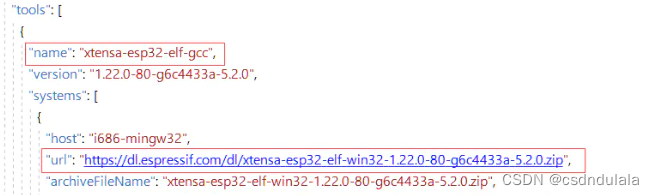

【ESP32学习-1】Arduino ESP32开发环境搭建

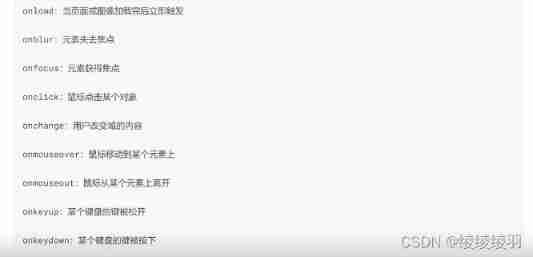

JS object and event learning notes

IOT system framework learning

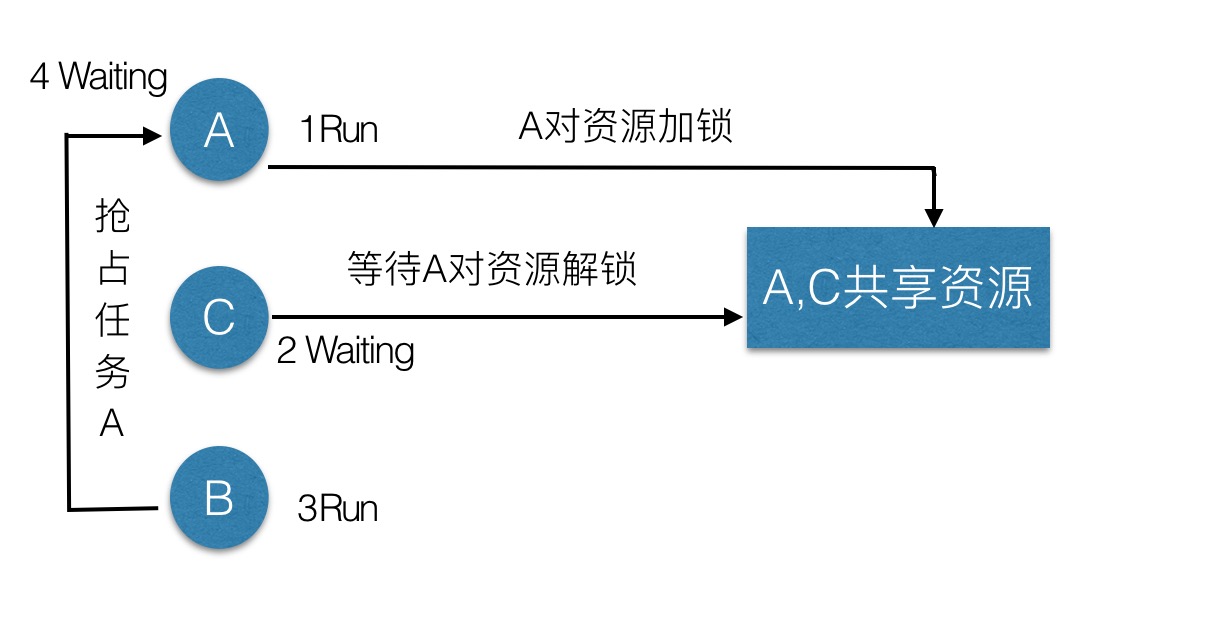

Priority inversion and deadlock

2019 Tencent summer intern formal written examination

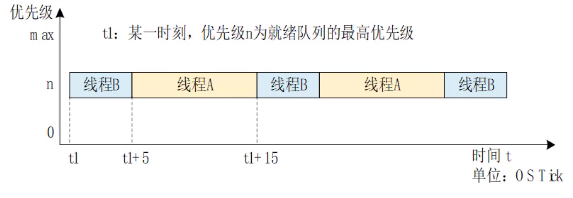

Time slice polling scheduling of RT thread threads

随机推荐

Stage 4 MySQL database

STM32型号与Contex m对应关系

RuntimeError: cuDNN error: CUDNN_STATUS_NOT_INITIALIZED

几个关于指针的声明【C语言】

Implementation scheme of distributed transaction

锂电池基础知识

Distribute wxWidgets application

[yarn] CDP cluster yarn configuration capacity scheduler batch allocation

SQL time injection

Vert. x: A simple TCP client and server demo

互联网协议详解

ESP8266使用arduino连接阿里云物联网

encoderMapReduce 随手记

Selective sorting and bubble sorting [C language]

RT-Thread 线程的时间片轮询调度

[template] KMP string matching

Linux Yum install MySQL

Redis面试题

AMBA、AHB、APB、AXI的理解

[mrctf2020] dolls