当前位置:网站首页>ICer知识点杂烩(后附大量题目,持续更新中)

ICer知识点杂烩(后附大量题目,持续更新中)

2022-07-07 15:46:00 【捌肆幺幺】

1.IC基础

1.1 锁存器触发器结构

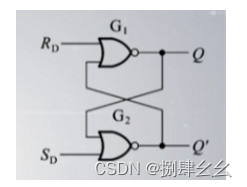

①锁存器

我们定义:

①Q = 1,且Q’ = 0 为锁存器的1状态

②Q = 0,且Q’ = 1 为锁存器的0状态

③Q为现在的状态,Q*为下一个状态,Q’为Q反

其真值表及功能如下:

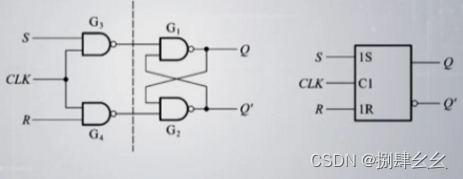

②触发器

触发器与锁存器的不同在于,它除了置1置0输人端以外,又加了一个触发信号输入,只有当触发信号到来时,触发器才能按照输人的置1、置0信号置成相应的状态,并保持下去,我们将这个触发信号称为时钟信号,记作CLK。

下面讲讲触发器的几种类型:

SR触发器:Q* = S + R’Q

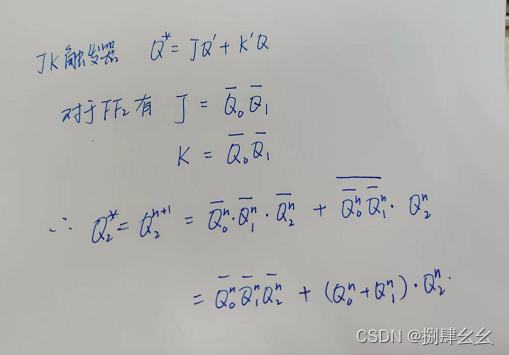

JK触发器:Q* = JQ’ + K’Q

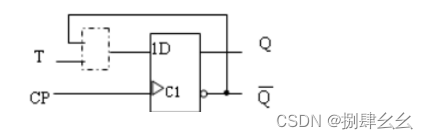

T触发器:Q* = TQ’ + T’Q

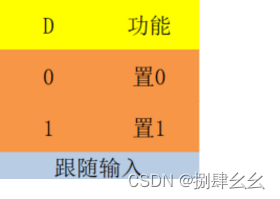

D触发器:Q* = D

1.2 建立保持时间

1.3 STA

1.4 CDC

1.5 亚稳态怎么解决

1.6 低功耗常见设计

1.7 竞争冒险

1.8 毛刺

1.9 IC设计流程

1.10 补码、原码、反码

1.11 格雷码、独热码

1.12 fifo深度

1.13 二进制小数转换

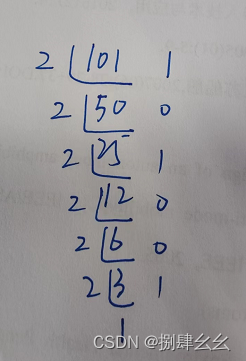

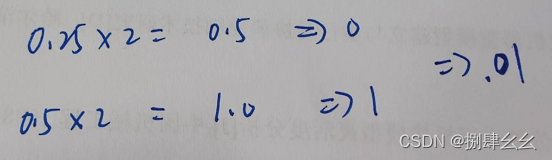

- 10进制数101.25,转换为2进制数为?

101转成二进制就不用多说了,短除法,度数从下往上读,看下图:非小数部分则为1100101

而小数部分则是 x2 取整处理,然后小数部分继续x2

因此答案是1100101.01

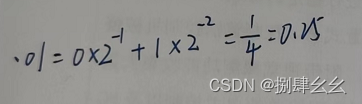

- 上面的题反过来呢?怎么用二进制小数化成10进制?

-1次方、-2次方的形式

如:

1.14 操作符优先级

2.手撕代码

2.1 异步fifo

2.2 同步fifo

2.3 除法器

2.4 乘法器

2.5 超前进位加法器

2.6 监沿器

2.7 输入消抖

2.8 去毛刺

2.9 计数器

2.10 无毛刺切换

2.11 移位寄存器

2.12 奇分频

2.13 偶分频

2.14 序列检查

设计一个序列检测器,将码流中的“10010”序列检测出来:

①三个输入,clk,rst_n,x,其中x是一位的输入,由x传输的多个数据构成码流

②输出z,在检测到完整的10010序列时,z拉高

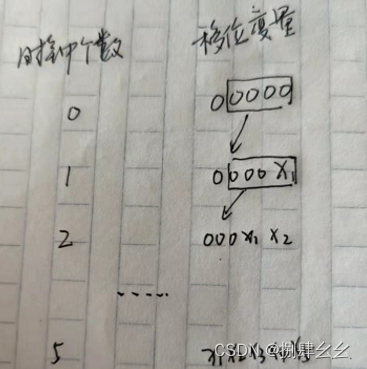

用移位寄存器的方法比状态机的方法代码要轻简很多,先说一下原理:

- 先定义一个5位的变量用来移位——shift = 5’b00000;

- 然后每输入一位x,移位放至shift中——shift <= {shift[3:0], x};

module check_num_shift

(

input clk,

input rst_n,

input x,

output wire z

);

reg [4:0] shift;

[email protected](posedge clk or negedge rst_n)begin

if(!rst_n)

shift <= 0;

else

shift <= {

shift[3:0],x};

end

assign z = (shift == 5'b10010)?1:0;

endmodule

2.15 脉冲展宽

对1bit的脉冲信号进行展宽,转为32bit位宽,并产生有效信号

- 首先题目什么意思呢?就是说给你1T周期宽度的脉冲信号,要你做成32T的宽度,并带上有效信号输出

- 思路:监沿器鉴定脉冲下降沿,输出有效信号;用计数器将1T延迟到32T

- 代码:

module 1_to_32(

input clk,

input rst_n,

input pulse_in,

output reg pulse_out,

output wire flag

);

//-------------------------------------------------------

reg pulse_in_ff0,pulse_in_ff1;

reg [4:0] cnt;

//-------------------------------------------------------

//监沿(下降沿)

always @(posedge clk or negedge rst_n)begin

if(!rst_n) begin

pulse_in_ff0<=1'b0;

pulse_in_ff1<=1'b0;

end

else begin

pulse_in_ff0 <= pulse_in;

pulse_in_ff1 <= pulse_in_ff0;

end

end

//前一拍为0,现在为1,则为上升沿

assign flag=(~pulse_in_ff1)&pulse_in_ff0;

//-------------------------------------------------------

//计数延长32个时钟

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

pulse_out<=1'b0;

else if(flag)

pulse_out<=1'b1;

else if(cnt==5'd31)

pulse_out<=1'b0;

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt<=5'b0;

else if(pulse_out==1'b1)begin

if(cnt==5'd31)

cnt<=5'd0;

else

cnt<=cnt+1'b1;

end

end

//-------------------------------------------------------

endmodule

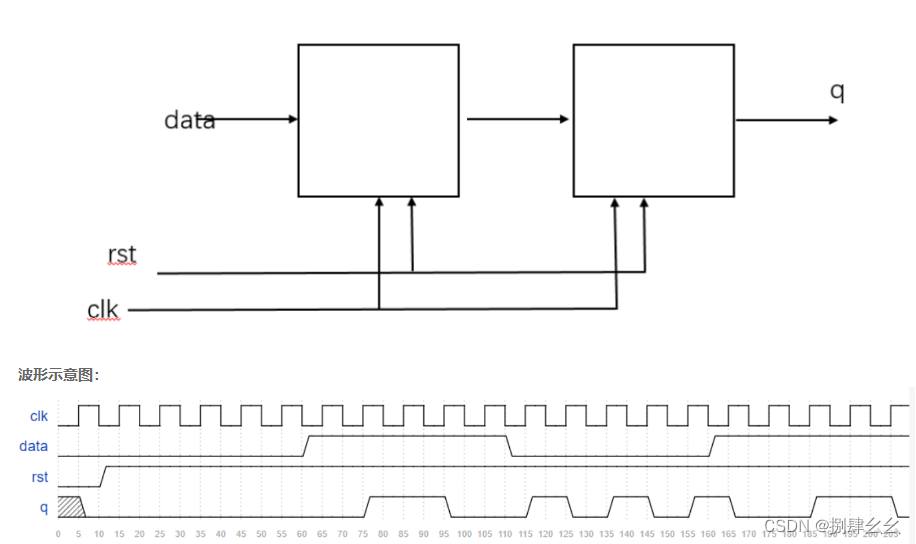

2.16 两个串联的异步复位的T触发器

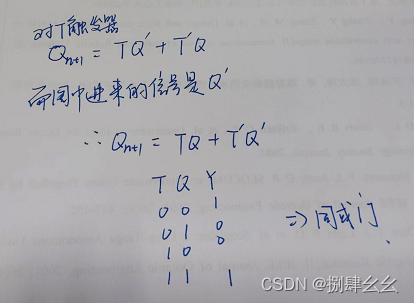

- T触发器的公式是Q* = TQ’ + T’Q ,相当于一个异或运算

- 所以采用两级tff即可

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output wire q

);

//*************code***********//

reg data_tff0;

reg data_tff1;

[email protected](posedge clk or negedge rst)begin

if(!rst)begin

data_tff0 <= 0;

data_tff1 <= 0;

end

else begin

data_tff0 <= data^data_tff0;

data_tff1 <= data_tff0^data_tff1;

end

end

assign q = data_tff1;

//*************code***********//

endmodule

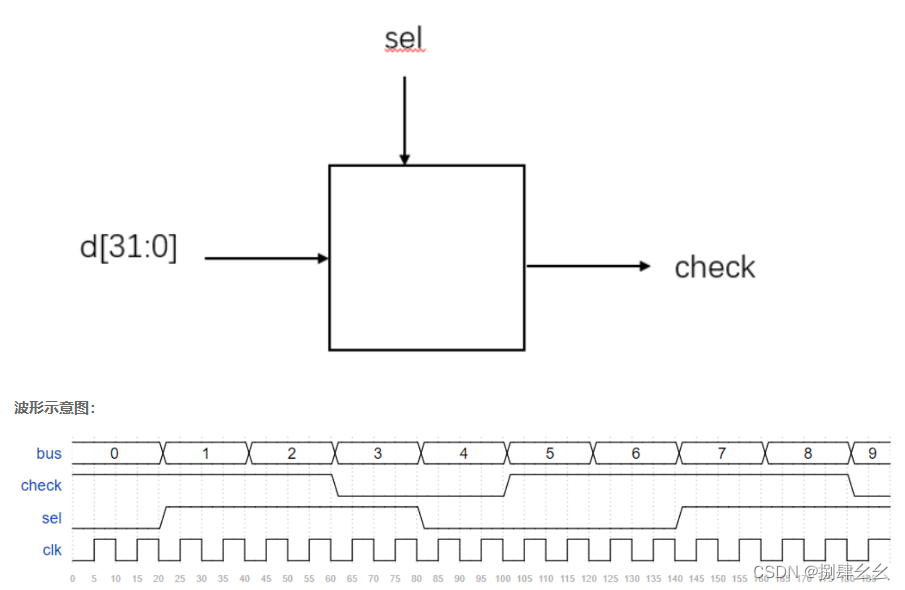

2.17 对输入的32位数据进行奇偶校验,根据sel输出校验结果(0输出奇校验,1输出偶校验)

- 首先你要明白奇偶校验的原理:通过在编码中增加一位校验位来使编码中1的个数为奇数或者偶数

- 那么我们怎么求奇偶校验位呢? 答案是异或

举个栗子,码流101 ,奇校验位是1,偶校验位是0 ,数据直接异或的结果是0,刚好是偶校验,那么这时奇校验取反就行 - 代码如下:

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

wire ji;

wire ou;

wire check;

assign ou = ^bus;

assign ji = ~ou;

assign check = (sel) ? ou :ji;

//*************code***********//

endmodule

3.电路知识

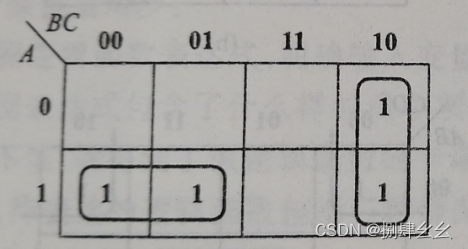

3.1 最小最大项及卡诺图

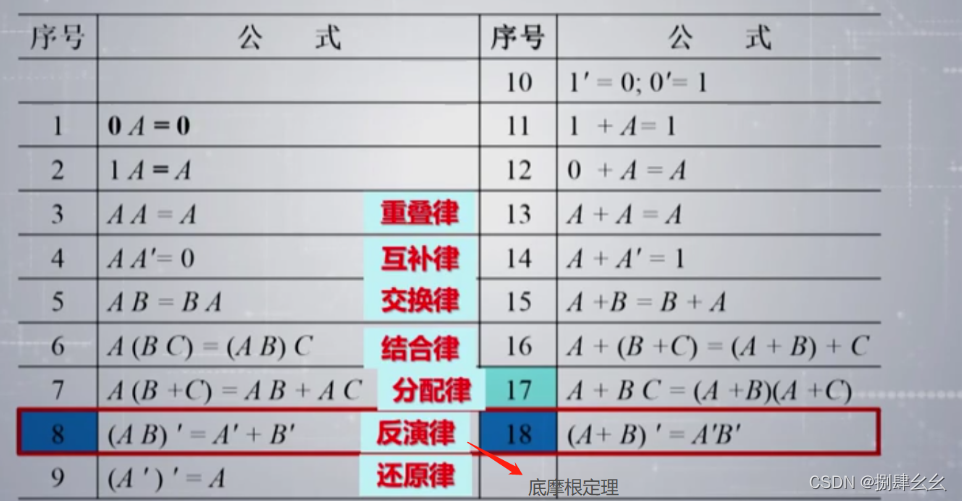

N个乘积项的表达(与项),如两变量AB的最小项为A’B’、A’B,、AB’、AB

最小项的性质: ①在输入变量任一取值下,有且仅有一个最小项的值为1; ②全体最小项之和为1 ; ③任何两个最小项之积为0 ; ④两个相邻的最小项之和可以合并,消去一对因子,只留下公共因子;(卡诺图重要原理) 相邻:仅一个因子不同的最小项,如:A'BC'与A'BC;N个项和的表达(或项),如两变量AB的最大项为A’+B’、A’+B,、A+B’、A+B

最大项的性质: ①在输入变量任一取值下,有且仅有一个最大项的值为0 ; ②全体最大项之积为0 ; ③任何两个最大项之和为1 ; ④两个相邻的最大项之积可以合并,消去一对因子,只留下公共因子。 相邻:仅一个因子不同的最大项,如:A'+B+C和A'+B+C卡诺图:用来进行化简

①将函数化为最小项之和的形式 ②画出卡诺图(00、01、11、10 格雷码),在最小项位置填1 ③把一圈起来! 圈1原则: 覆盖所有的1 圈圈数目做到最少 圈圈里面1尽量多

如上图,找公用的项

横着的圈是 AB’

竖着的圈是BC’

结果就是AB’ + BC’

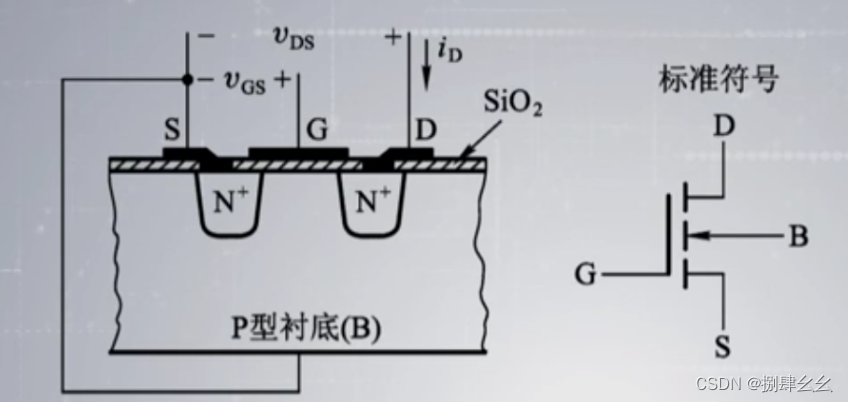

3.2 MOS管原理

总的就是说:在DS两极加电压,DS不导通;在GS加电压,DS间形成沟道使得DS导通

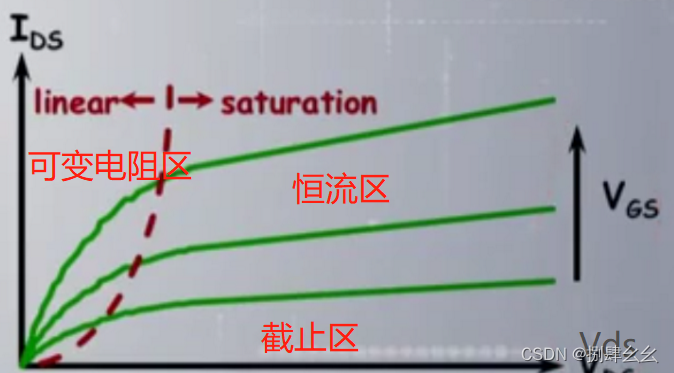

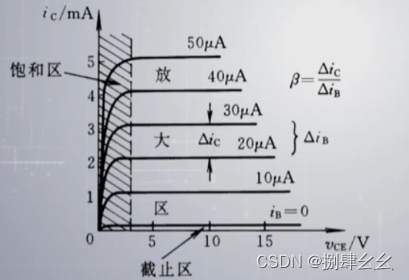

其也可以分为三个区:

①当Vgs < Vgs(th) 时,也就是小于启动电压时,这部分区域成为截至区

②当Vgs > Vgs(th) 时,如上图所示,虚线左边成为可变电阻区,其等效电阻的大小与Vgs有关

③虚线右边是恒流区,此时电流基本上由Vgs决定

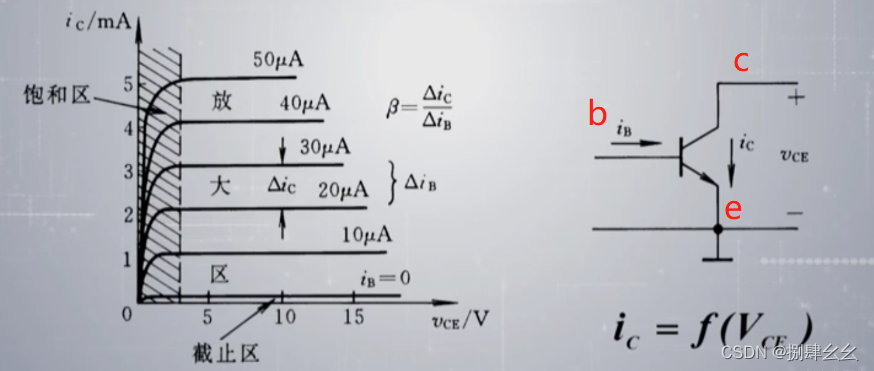

3.3 TTL管原理

①截止区:条件Vbe= 0, ib = 0, ic = 0, c一e间“断开”

②放大区 :条件Vce> 0.7, ib>0, ic 随ib成正比变化, △ic=β△ib

③饱和区 :条件Vce< 0.7, ib >0, Vce 很低,△ic随△ib增加变缓,趋于“饱和”

3.4 触发器种类

前面1.1已经说过了,这里不在阐述

3.5 多谐振荡电路

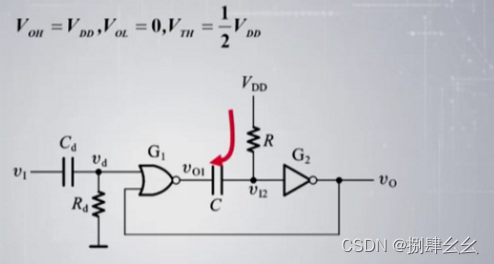

- 多谐振荡电路是一种自激振荡电路

- 在接通电源以后,不需要外加触发信号,便能自动地产生矩形脉冲

- 由于矩形波中含有丰富的高次谐波分量,习惯上又将矩形波振荡电路称为多谐振荡电路

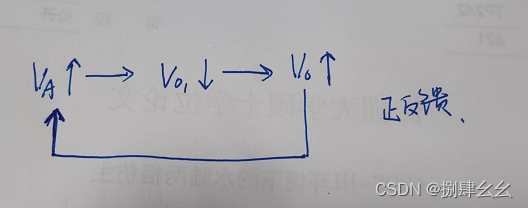

①对称式多谐振荡器:两个反相器与两个电容耦合起来的正反馈振荡电路。

②非对称式多谐振荡器:在对称式的基础上简化。

③施密特多谐振荡器:用施密特触发电路的反相输出经RC积分接回输入。

④环形振荡器:利用延迟负反馈产生振荡。

⑤石英晶体多谐振荡器:石英晶体 + 对称式(接入石英晶体稳频)

3.6 单稳态电路

单稳态电路中的工作特性具有下的显著特点:

- 第一,它有稳态和暂稳态两个不同的工作状态

- 第二,在外界触发脉冲作用下,能从稳态翻转到暂稳态,在暂稳态维持一段时间以后,再自动返回稳态

- 第三,暂稳态维持时间的长短取决于电路本身的参数,与触发脉冲的宽幅度无关

例子: 声控灯,灭的时候是稳态、而亮则是暂稳态

原理:

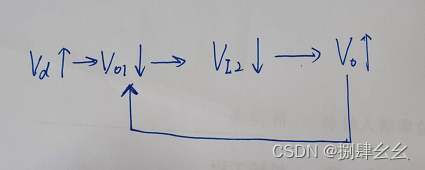

①当vi = 0,vi2 = vdd,所以vo = 0

②当vi接脉冲时,在cd和rd之间会产生窄脉冲vd,当vd = vth后,发生如下正反馈

③迅速使得vo1 = vi2 = 0

④由于电容电压不会发生迅速的跳变,因此进入暂稳态

⑤当vdd给电容充电完毕后,又进入稳态

- 单稳态有两种类型的电路:

①微分型:可以用窄脉冲触发、输出脉冲下降沿较差

②积分型:抗干扰能力强、输出边沿比较差

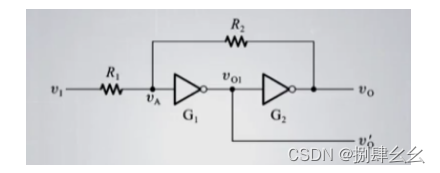

3.7 施密特触发电路

①输入信号在上升和下降过程中,电路状态转换的输入电平不同

②电路状态转换时有正反馈过程,使输出波形边沿变陡

③用于波形的变换

④用于监幅

⑤用于脉冲整形

原理:

①当vi = 0 ,vo = vol = 0 ,这是va也是0

②而vi从0升到vth,CMOS管G1导通,引起如下正反馈

③此时vo迅速上高到vdd,而此时vi的值就是我们所说的vt+

④同理vi从vdd下降到vt-,vo从voh变成vol,也是正反馈过程

3.8 逻辑计算

一张表足矣

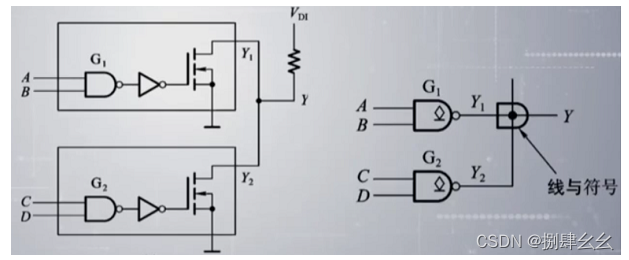

3.9 线与

- 线与说白了就是物理上连接、电器上选择连接

- 线与在ttl管中是通过两个OC与非门(集电极开路门)来实现的

- 线与在mos管中是通过两个OD与非门(漏级开路门)来实现的

- 他们大致的图都如下所示,只有当Y1Y2都是1,Y才输出1

那么为什么需要用OD/OC门来做线与呢?可以看看OD门的特点:

①可以利用外部电路的驱动能力,减少IC内部的驱动,或者驱动比芯片电源电压高的负载

②可以将多个开漏输出的Pin,连接到一条线上,这也就是一些总线的占用原理

③可以利用改变上拉电源的电压,改变传输电平;如加上上拉电阻就可以提供TTL/CMOS电平输出

④正常的CMOS输出级是上、下两个管子,把上面的管子去掉就是OPEN-DRAIN(OD)

⑤缺点:OD门提供了灵活的输出方式,但也带来了上升沿的延时

4.刷刷刷刷

1晶体管用于放大作用,工作在什么区?

放大区(也叫线性区) :条件Vce> 0.7, ib>0, ic 随ib成正比变化, △ic=β△ib

0.7的Von是硅三极管,锗三极管是0.3

2CMOS管用于开关作用,工作在什么区?

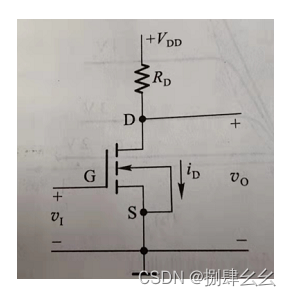

单个MOS管时,看下图;

输入为低电平时,MOS管处于截止区,输出高电平1;

输入为高电平时,MOS管导通(个人觉得时工作在可变电阻区),输出低电平0

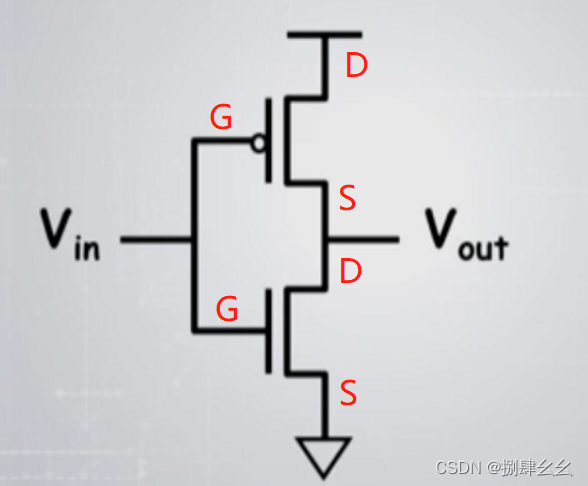

当为CMOS管时,看下图;

无论输入是高电平还是低电平,两个MOS管总是一个截至一个导通,即为所谓的互补关系;

而CMOS中的C就是互补的意思;

3设计一个序列发生器,以CLK为控制信号,输出序列为0010110111

module check_num_shift

(

input clk,

input x,

output wire is_it

);

reg [9:0] shift;

[email protected](posedge clk)begin

shift <= {

shift[8:0],x};

end

assign is_it= (shift == 10'b0010110111)?1:0;

endmodule

4共阳数码管(如图示)的显示译码器,当输入A3A2A1A0为0101时,输出为多少

输入为0101即要显示数字5,因此afgcd亮灯,置0,其他置1 ,所以输出是0100100

5.5个具有计数功能的T触发器链接,输入脉冲频率为256KHZ, 则此计数器最高位触发器的输出脉冲频率为多少

每输入一个时钟脉冲,触发器状态便翻转一次,实现一次分频,因此5个就是除以 2^5,最后为8KHZ

6什么是BCD码计数器?在4个触发器构成的 8421BCD码计数器中,具有几个无关状态?

BCD码就是用4位二进制数来表示1位十进制数中的0~9这10个数码,因此BCD码计数器就是0-9的计数器,4位触发器共有16种状态,所以多出了6种无关状态

7若传感器的输出分辨率为1mV,ADC的电源为5V,基准电压为2.5V,为保证ADC的采样精度,ADC的位数至少为多少?

传感器的输出电压为模拟信号,它作为ADC的输入信号,其分辨率为1mV,为保证ADC采样精度,n位ADC可以分辨的最小模拟电压就是1mV;分辨率的公式如下,Vref是基准电压2.5

所以算的n最小为12位

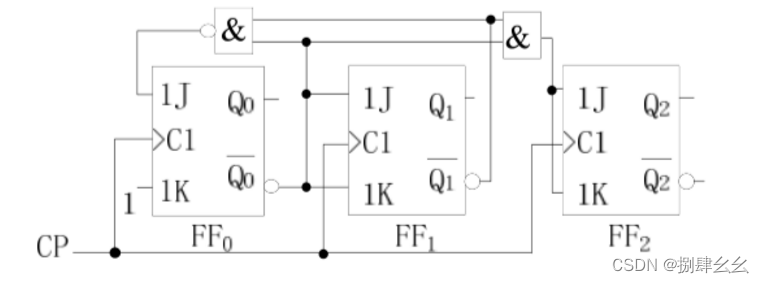

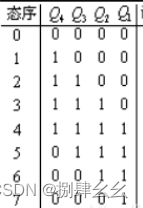

8分析下图所示电路,设各触发器初始状态为0,算出Q2n+1的方程

9测量高压电路电流时,应将电流表接到接近哪一端?

处于零电位一端,电流表上承受的共模电压小。

10对一个异步fifo,列出你能想到的所有测试点?

对着信号一个一个列出来感觉不会有什么问题

- 写端口时序行为与描述一致,检查数据在wr被采样时刻正确写入

- 读端口时序行为与描述一致,检查数据在rd被采样时刻正确读出

- 空信号能正确生成

- 满信号能正确生成

- 写满读空之后是否有做读写保护防止数据覆盖

- 写满读空之后是否有做读写保护防止空满信号错乱

- 是否能被正常复位,解复位后各输出信号初始状态(复位值)是否正常

- 格雷码转换逻辑的正确性

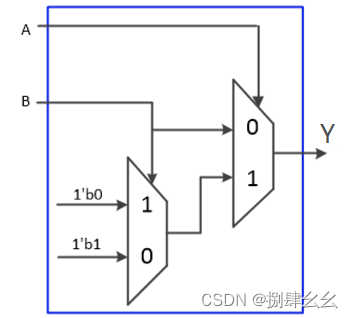

11只使用(2选1MUX)完成异或门逻辑,最少需要多少个MUX

Y = A’B +AB’,即:A=0时,Y = B;A=1时,F = Y’

12时序检查中对于异步复位电路的时序分析分别是?

- recovery time:恢复时间

撤销复位时,恢复到解复位状态的电平必须在时钟有效沿来临之前的一段时间到来,才能保证时钟能有效恢复到解复位状态,此段时间为recovery time。

- removal time :移除时间

复位时,在时钟有效沿来临之后复位信号还需要保持的时间为移除时间removal time

13关于于网表仿真描述正确的是?

A.网表仿真不能发现实现约束的问题

B.仿真速度比RTL仿真速度更快

C.网表仿真可以发现电路设计中的异步问题

D.为了保证芯片正常工作,即使在时间和资源紧张情况下,也需要将所有的RTL仿真用例都进行网表仿真并且确保通过

网表仿真通过网表反标sdf进行仿真,仿真速度较RTL仿真慢,由于sdf通过sdc约束和单元逻辑延时和线网延时而来,可以发现约束问题。设计大的话,网表仿真太耗时,常用采用形式验证手段来保证门级网表在功能上与RTL设计保持一致,配合静态时序分析工具保证门级网表的时序

14N位触发器构成的扭环形计数器,其无关状态数有几个?

扭环形计数器,亦称约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,可使用2n个状态,有2n-2n个状态未使用

Verilog代码:右移,[0]位取反补高位

module johnson_cnt(

input clk,

input rst_n,

output reg [3:0] out

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

out <= 4'b0;

end

else begin

out <= {

~out[0], out[3:1]} ;

end

end

endmodule

15什么结构化描述?行为描述?数据流描述?

数据流描述:采用assign 连续赋值语录。

行为描述:使用always 语句或initial 语句块中的过程赋值语录

结构化描述:实例化已有的功能模块或原语

16为实现D触发器转换成T触发器,图示的虚线框内应是什么电路?

17有一个FIFO设计,输入时钟100Mhz,输出时钟80Mhz,输入数据模式是固定的,其中1000个时钟中有800个时钟传输连续数据,另外200个空闲,请问为了避免FIFO下溢/上溢,最小深度是多少

边栏推荐

- What is agile testing

- 本周小贴士131:特殊成员函数和`= default`

- Dragging the custom style of Baidu map to the right makes the global map longitude 0 unable to be displayed normally

- Ansible learning summary (9) -- ansible loop, condition judgment, trigger, processing failure and other task control use summary

- Introduction to OTA technology of Internet of things

- Threshold segmentation based on RGB image and threshold adjustment by sliding

- 做软件测试 掌握哪些技术才能算作 “ 测试高手 ”?

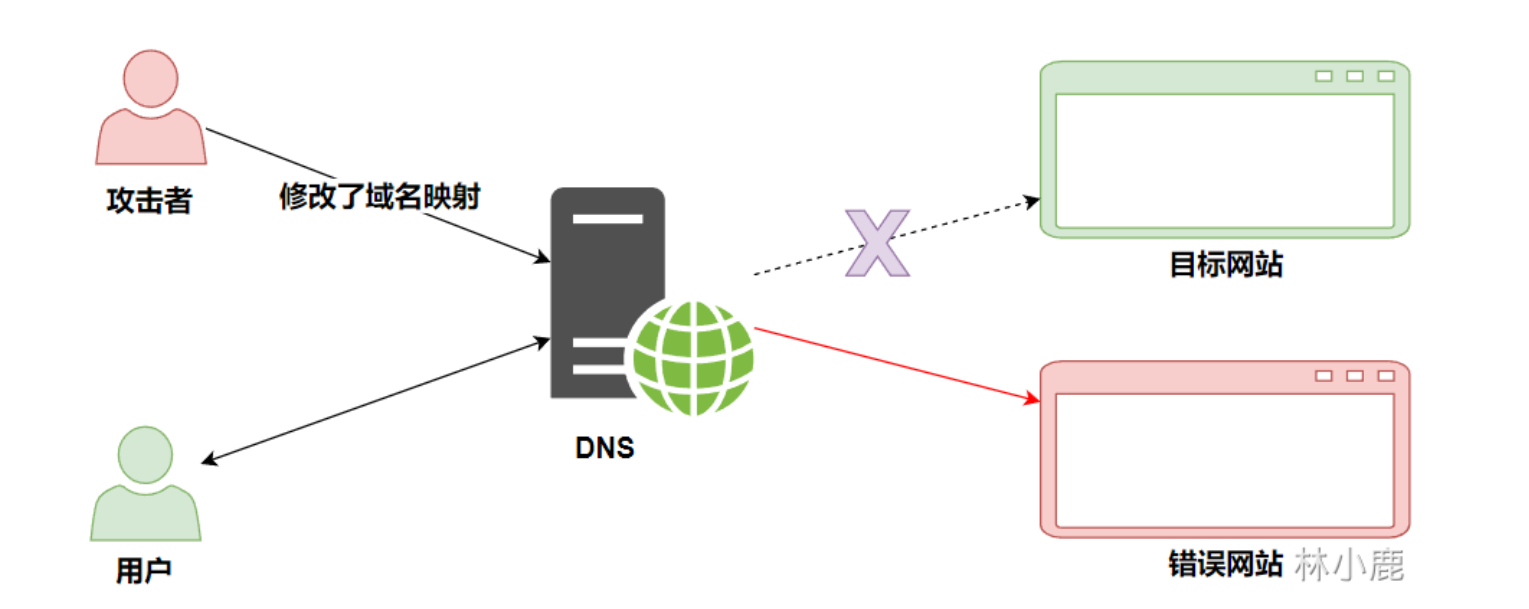

- 网络攻防复习篇

- 【深度学习】3分钟入门

- Mrs offline data analysis: process OBS data through Flink job

猜你喜欢

Deep learning - make your own dataset

![[answer] if the app is in the foreground, the activity will not be recycled?](/img/b7/a749d7220c22f92080b71fd3859b8d.png)

[answer] if the app is in the foreground, the activity will not be recycled?

![[deep learning] 3 minutes introduction](/img/d9/acaff84dbe6bc97885b41766aa841d.png)

[deep learning] 3 minutes introduction

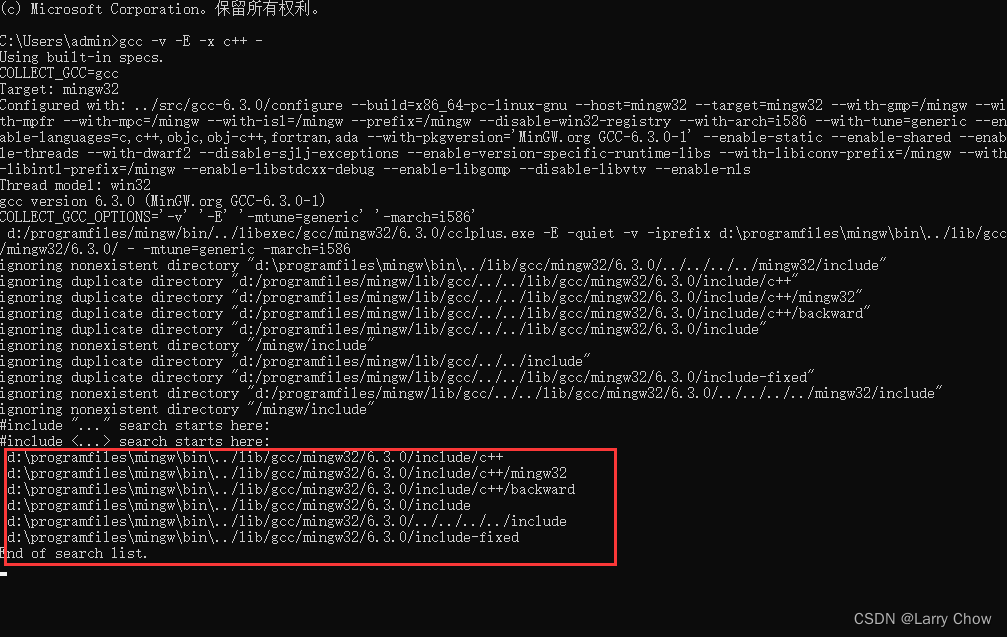

VSCode关于C语言的3个配置文件

zdog.js火箭转向动画js特效

漫画 | 宇宙第一 IDE 到底是谁?

【网络攻防原理与技术】第5章:拒绝服务攻击

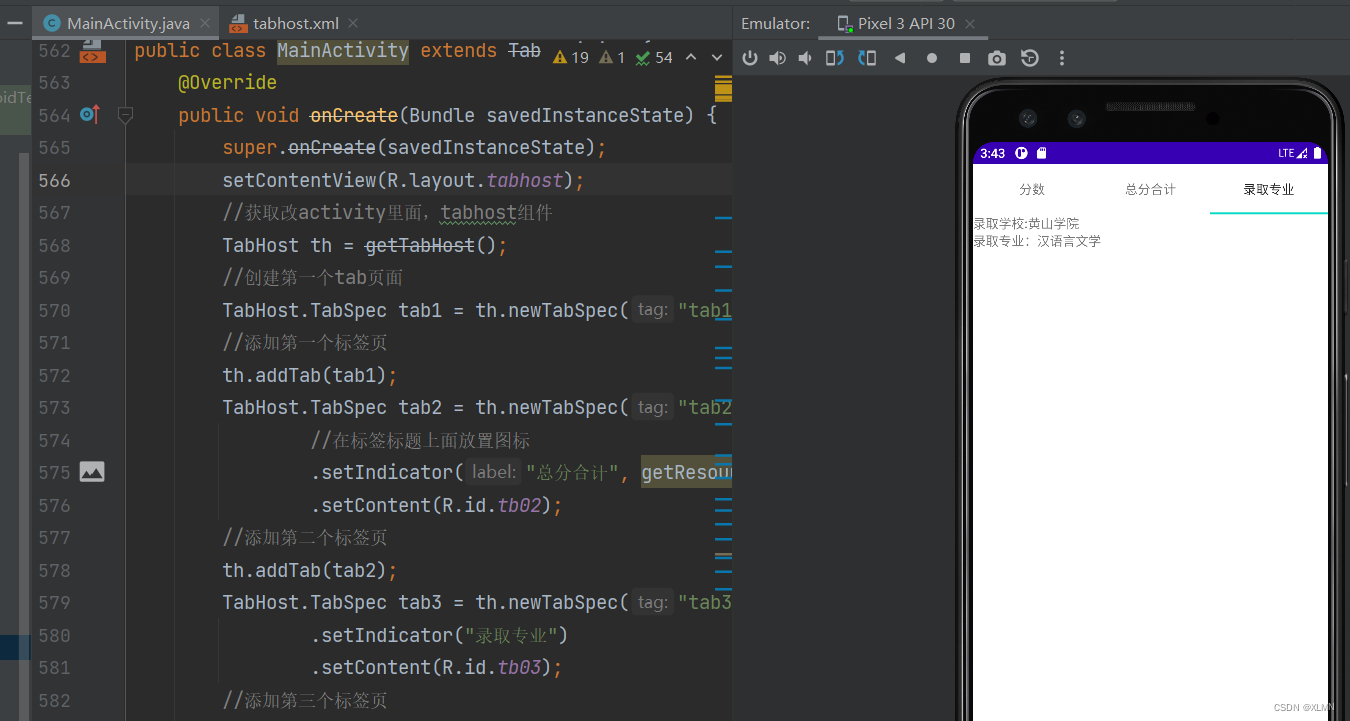

Functions and usage of tabhost tab

目标检测1——YOLO数据标注以及xml转为txt文件脚本实战

Use onedns to perfectly solve the optimization problem of office network

随机推荐

Robot engineering lifelong learning and work plan-2022-

百度地图自定义样式向右拖拽导致全球地图经度0度无法正常显示

第3章业务功能开发(用户访问项目)

MySQL index hit level analysis

深度学习-制作自己的数据集

zdog.js火箭转向动画js特效

Based on pytorch, we use CNN to classify our own data sets

calendarview日历视图组件的功能和用法

简单的loading动画

[distributed theory] (I) distributed transactions

Face recognition attendance system based on Baidu flying plasma platform (easydl)

USB通信协议深入理解

How to implement safety practice in software development stage

深入浅出图解CNN-卷积神经网络

【网络攻防原理与技术】第6章:特洛伊木马

datepicket和timepicket,日期、时间选择器的功能和用法

Easy to understand [linear regression of machine learning]

MRS离线数据分析:通过Flink作业处理OBS数据

深度学习机器学习各种数据集汇总地址

使用Stace排除故障的5种简单方法