当前位置:网站首页>[Digital IC manual tearing code] Verilog automatic beverage machine | topic | principle | design | simulation

[Digital IC manual tearing code] Verilog automatic beverage machine | topic | principle | design | simulation

2022-07-06 21:37:00 【myhhhhhhhh】

Preface

This series aims to provide 100% Accurate numbers IC Design / Verify the title of the hand tearing code link , principle ,RTL Design ,Testbench And reference simulation waveform , The content of each article is checked by simulation . The quick navigation links are as follows :

Odd frequency division

Even frequency division

Semi integer batch

decimal / Fractional frequency division

Sequence detector

Mode three detector

Beverage machine

Asynchronous reset , Simultaneous release

Edge detection ( Rising edge , Falling edge , On both sides )

Full adder , Half adder

Gray code to binary

single bit Cross clock domain ( Two beats , Edge synchronization , Pulse synchronization )

Sync FIFO

Ought to say , The hand tearing code link is in the interview process Both important and simple A part of , Compared with software jobs , Numbers IC Hand tear code Fixed topic , Limited number , It belongs to a link that must be scored in the whole interview , Outside this series , I also recommend numbers IC Job seekers use “HdlBits” Code Training

Links are as follows

HDLBits — Verilog Practice

Problem of automatic beverage machine

1. Use Verilog Design circuit , Complete the following functions : Each bottle of drink 1.5 element , You can only put in one coin at a time , Available input 0.5 And 1.0 Two kinds of coins , With change function .

Principle of automatic beverage selling machine

First , It is obvious that , This hand tearing code should be used State machine To complete

The distinction between States , We can classify according to the amount remaining in the beverage machine , Because there are only two kinds of coins ,0.5/1 element , therefore The state can be divided as follows

- IDLE: Reset state , Indicates that the balance in the beverage machine is 0 element

- s1: The balance of the beverage machine is 0.5 element

- s2: The balance in the beverage machine is 1 element

- s3: The balance in the beverage machine is 1.5 element ( Export drinks , No change )

- s4: The balance in the beverage set is 2 element ( Export drinks , Give change )

So for the input and output of this state machine

Input : Two of you input Represents the coin put ,input[1] Pulling up means investing one yuan ,input[0] Higher means investment 0.5 element , By default, only one coin can be inserted at a time .

Output :drink Represents the output of drinks ,coin Represents the output of coins .

Veilog Design

module drink_machine( clk ,rst_n, money,drink,coin);

input clk;

input rst_n;

input [1:0] money;

output drink;

output coin;

parameter IDLE = 3'd0, s1=3'd1 ,s2=3'd2, s3=3'd3,s4=3'd4;

reg [2:0] state,nstate;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

state<=IDLE;

else

state<=nstate;

end

[email protected](*)

begin

case(state)

IDLE:nstate = money[1] ? s2 : (money[0] ? s1 :IDLE);

s1: nstate = money[1] ? s3 : (money[0] ? s2 : s1);

s2: nstate = money[1] ? s4 : (money[0] ? s3 : s2);

s3: nstate = money[1] ? s2 : (money[0] ? s1 :IDLE);

s4: nstate = money[1] ? s2 : (money[0] ? s1 :IDLE);

default nstate = IDLE;

endcase

end

assign drink = (state == s3 || state == s4)? 1:0;

assign coin = (state == s4)? 1:0;

endmodule

Testbench Design

module drink_machine_tb();

reg clk;

reg rst_n;

reg [1:0] money;

wire drink;

wire coin;

drink_machine u1 (.clk(clk),.rst_n(rst_n),.money(money),.drink(drink),.coin(coin));

always #5 clk = !clk;

always #10.001 money = {

$random} % 3;

initial

begin

clk = 0;

rst_n = 1;

#10

rst_n = 0;

#20

rst_n = 1;

#1000

$stop;

end

endmodule

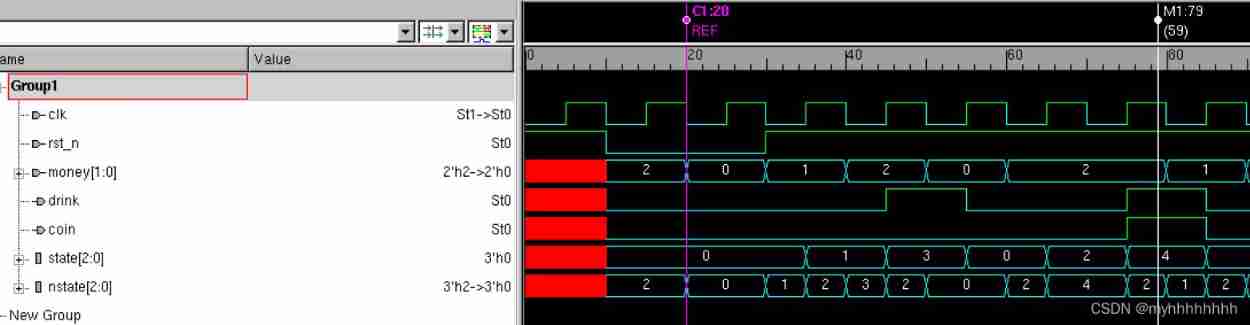

Simulation results

from 20ns To 80ns In the process of , Cast Five cents a piece , One by one ,drink Output is 1.

Then , Cast a piece , Throw another piece ,drink Output is 1 At the same time coin Also output as 1

Other state jumps also meet expectations , Design establishment .

边栏推荐

- 字符串的使用方法之startwith()-以XX开头、endsWith()-以XX结尾、trim()-删除两端空格

- What's the best way to get TFS to output each project to its own directory?

- C# 如何在dataGridView里设置两个列comboboxcolumn绑定级联事件的一个二级联动效果

- 967- letter combination of telephone number

- Vim 基本配置和经常使用的命令

- SDL2来源分析7:演出(SDL_RenderPresent())

- First batch selected! Tencent security tianyufeng control has obtained the business security capability certification of the ICT Institute

- How do I remove duplicates from the list- How to remove duplicates from a list?

- Why do job hopping take more than promotion?

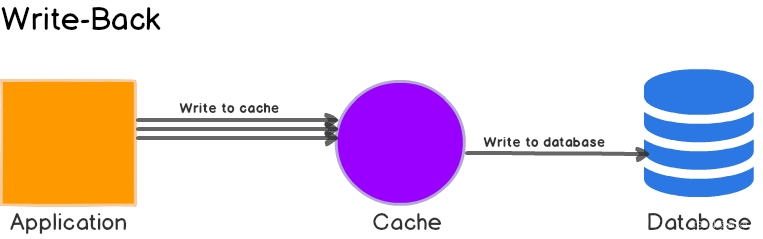

- 缓存更新策略概览(Caching Strategies Overview)

猜你喜欢

![[in depth learning] pytorch 1.12 was released, officially supporting Apple M1 chip GPU acceleration and repairing many bugs](/img/66/4d94ae24e99599891636013ed734c5.png)

[in depth learning] pytorch 1.12 was released, officially supporting Apple M1 chip GPU acceleration and repairing many bugs

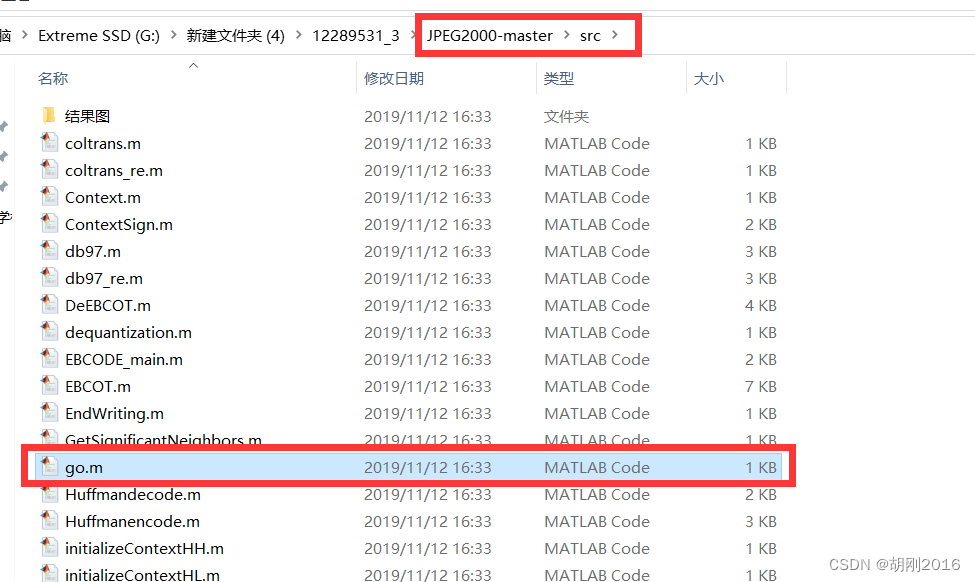

JPEG2000-Matlab源码实现

Dialogue with Jia Yangqing, vice president of Alibaba: pursuing a big model is not a bad thing

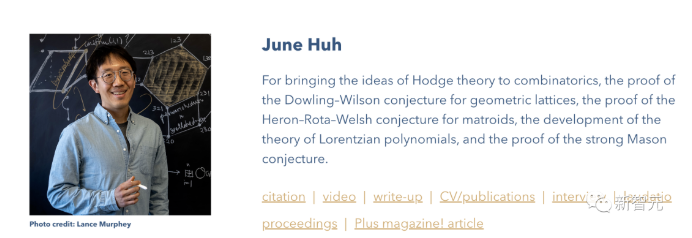

2022 fields Award Announced! The first Korean Xu Long'er was on the list, and four post-80s women won the prize. Ukrainian female mathematicians became the only two women to win the prize in history

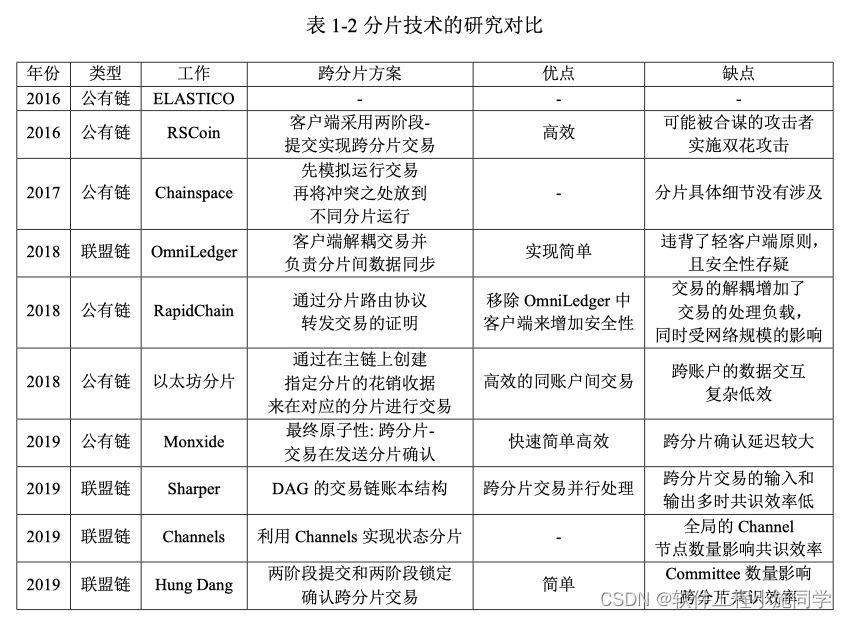

Summary of cross partition scheme

对话阿里巴巴副总裁贾扬清:追求大模型,并不是一件坏事

![[sliding window] group B of the 9th Landbridge cup provincial tournament: log statistics](/img/2d/9a7e88fb774984d061538e3ad4a96b.png)

[sliding window] group B of the 9th Landbridge cup provincial tournament: log statistics

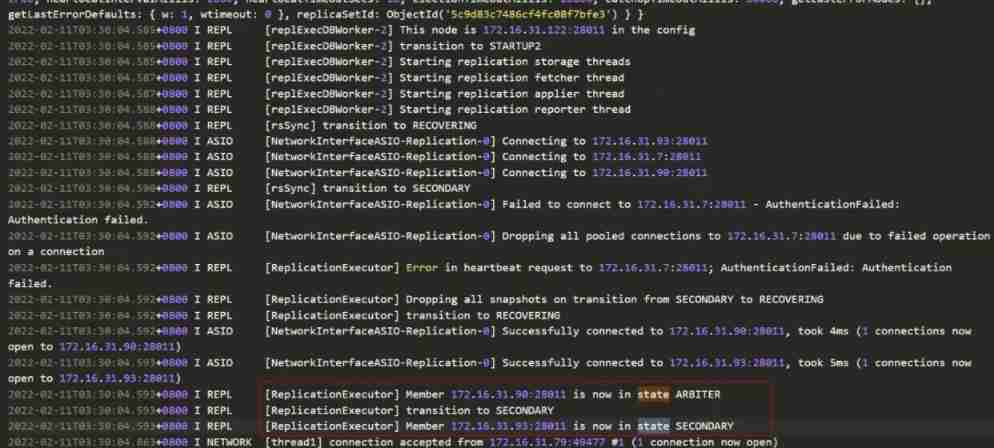

20220211 failure - maximum amount of data supported by mongodb

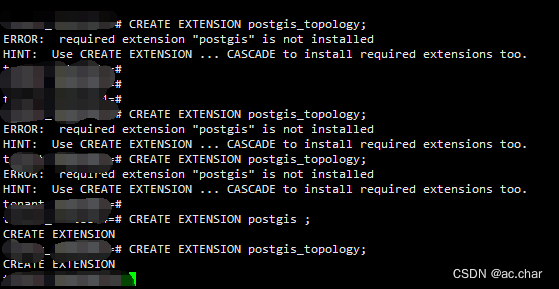

PostgreSQL 安装gis插件 CREATE EXTENSION postgis_topology

缓存更新策略概览(Caching Strategies Overview)

随机推荐

SQL:存储过程和触发器~笔记

[in depth learning] pytorch 1.12 was released, officially supporting Apple M1 chip GPU acceleration and repairing many bugs

3D face reconstruction: from basic knowledge to recognition / reconstruction methods!

Redistemplate common collection instructions opsforzset (VI)

jvm:大对象在老年代的分配

ViT论文详解

[redis design and implementation] part I: summary of redis data structure and objects

039. (2.8) thoughts in the ward

b站视频链接快速获取

Binary tree node at the longest distance

968 edit distance

Is this the feeling of being spoiled by bytes?

Hill | insert sort

愛可可AI前沿推介(7.6)

Word bag model and TF-IDF

语谱图怎么看

SDL2来源分析7:演出(SDL_RenderPresent())

Is it profitable to host an Olympic Games?

Seven original sins of embedded development

js中,字符串和数组互转(一)——字符串转为数组的方法