当前位置:网站首页>50Mhz产生时间

50Mhz产生时间

2022-07-07 23:12:00 【eachanm】

50Mhz 对应一个计数为0.02us,也就是20纳秒,计数到1us要50个计数,其他可自己算,下面是产生1us、1ms、1s的方法

module count_time

#(

parameter CNT_1US_MAX = 6'd49,

parameter CNT_1MS_MAX = 10'd999,

parameter CNT_1S_MAX = 10'd999

)

(

input wire sys_clk,

input wire sys_rst_n,

output reg led_out

);

//50Mhz为20ns

reg [9:0]cnt_1s; //让1ms计数到1000

reg [9:0]cnt_1ms; //让1us计数到1000

reg [5:0]cnt_1us; //计数到50

reg cnt_en;

//1us

[email protected] (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1us <= 6'd0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1us <= 6'd0;

else

cnt_1us <= cnt_1us +6'd1;

//1ms

[email protected] (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1ms <= 10'd0;

else if(cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_1ms <= 10'd0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1ms <= cnt_1ms +10'd1;

else

cnt_1ms <= cnt_1ms;

//1s

[email protected] (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_1s <= 10'd0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_1s <= 10'd0;

else if(cnt_1us == CNT_1US_MAX && cnt_1ms == CNT_1MS_MAX )

cnt_1s <= cnt_1s + 10'd1;

else

cnt_1s <= cnt_1s;

//控制状态

[email protected] (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_en <= 1'b0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX)

cnt_en <= ~cnt_en;

else

cnt_en <= cnt_en;

[email protected] (posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

led_out <= 1'b1;

else if((cnt_en == 1'b0) && (cnt_1ms <= cnt_1s)

|| (cnt_en == 1'b1) && (cnt_1ms >= cnt_1s))

led_out <= 1'b0;

else

led_out <= 1'b1;

endmodule

时钟频率对应的时钟周期

5MHz 200ns

10MHz 100ns

20MHz 50ns

25MHz 40ns

33MHz 30ns

40MHz 25ns

50MHz 20ns

66MHz 15ns

80MHz 12ns

100MHz 10ns

120MHz 8.3ns

133MHz 7.5ns

166MHz 6.0ns

200MHz 5.0ns

250MHz 4.0ns

300MHz 3.3ns

333MHz 3.0ns

400MHz 2.5ns

500MHz 2.0ns

800MHz 1.2ns

1GHz 1.0ns

4GHz 0.25ns

常用单位换算

1GHz=1000MHz,1MHz=1000kHz,1kHz=1000Hz

1s=1000ms,1 ms=1000μs,1μs=1000ns

s(秒)、ms(毫秒)、μs(微秒)、ns(纳秒)

边栏推荐

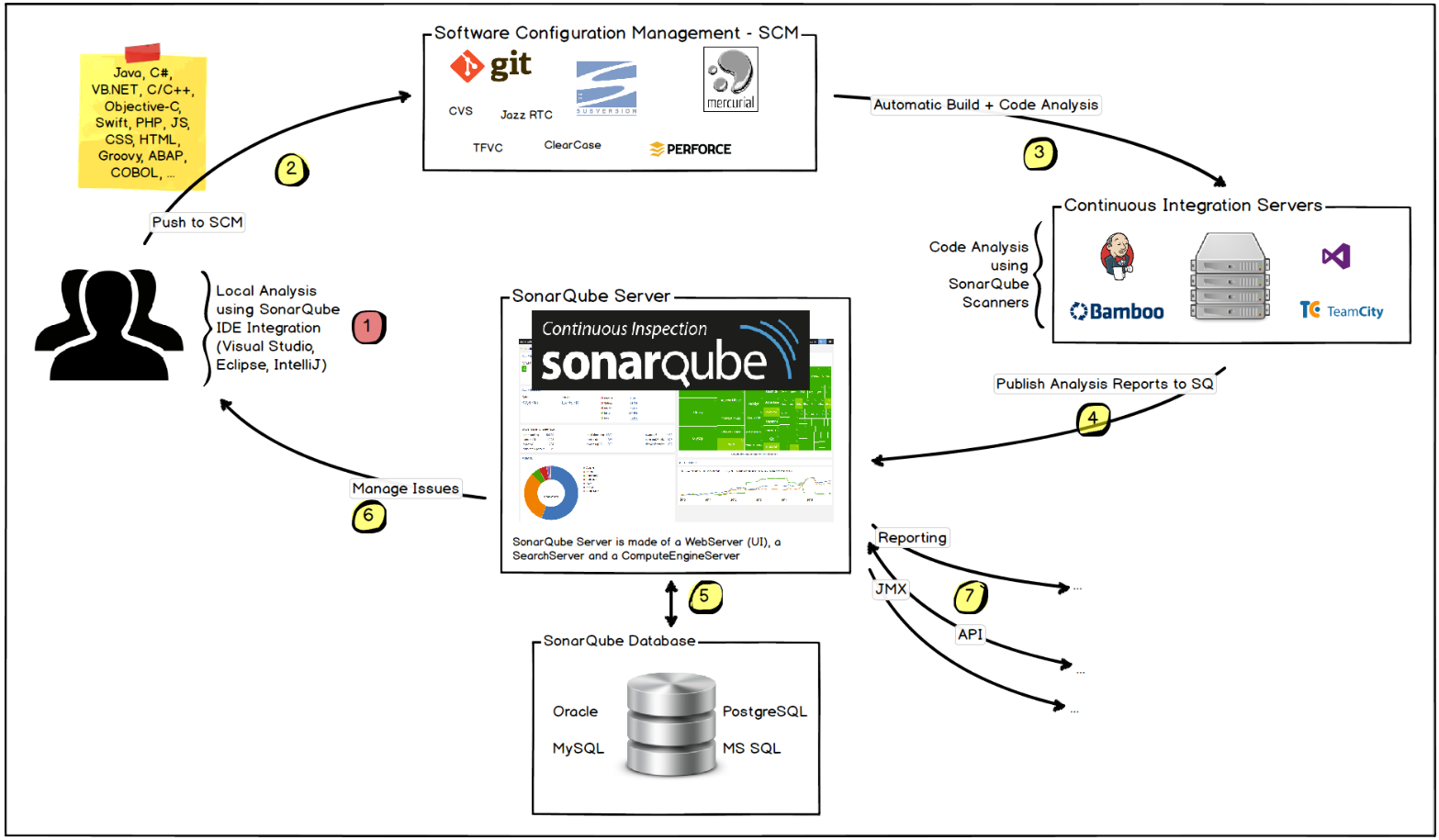

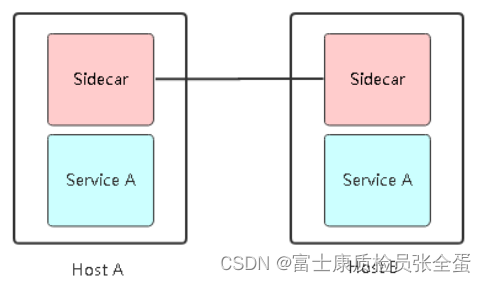

- Basic mode of service mesh

- 什么是负载均衡?DNS如何实现负载均衡?

- Implementation of adjacency table of SQLite database storage directory structure 2-construction of directory tree

- 新库上线 | 中国记者信息数据

- ReentrantLock 公平锁源码 第0篇

- 13. Model saving and loading

- Introduction to ML regression analysis of AI zhetianchuan

- 图像数据预处理

- Interface test advanced interface script use - apipost (pre / post execution script)

- What has happened from server to cloud hosting?

猜你喜欢

Jouer sonar

Service mesh introduction, istio overview

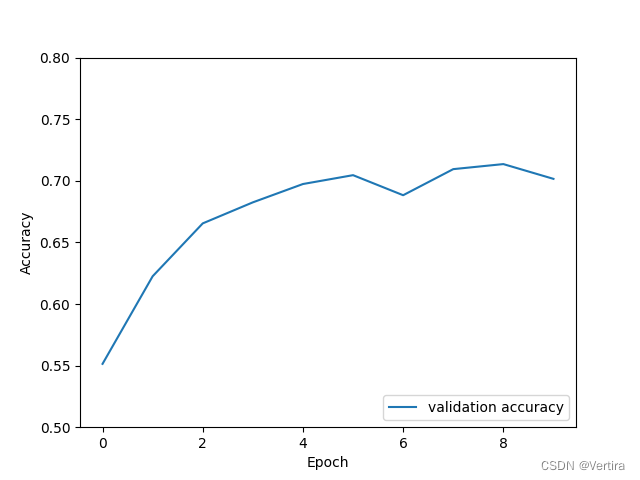

A network composed of three convolution layers completes the image classification task of cifar10 data set

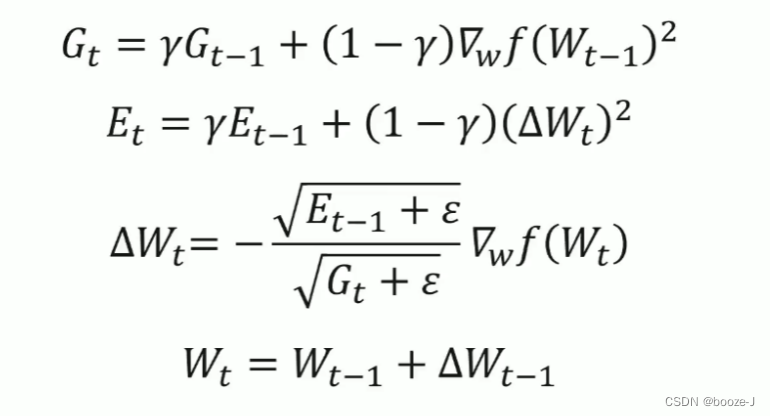

8.优化器

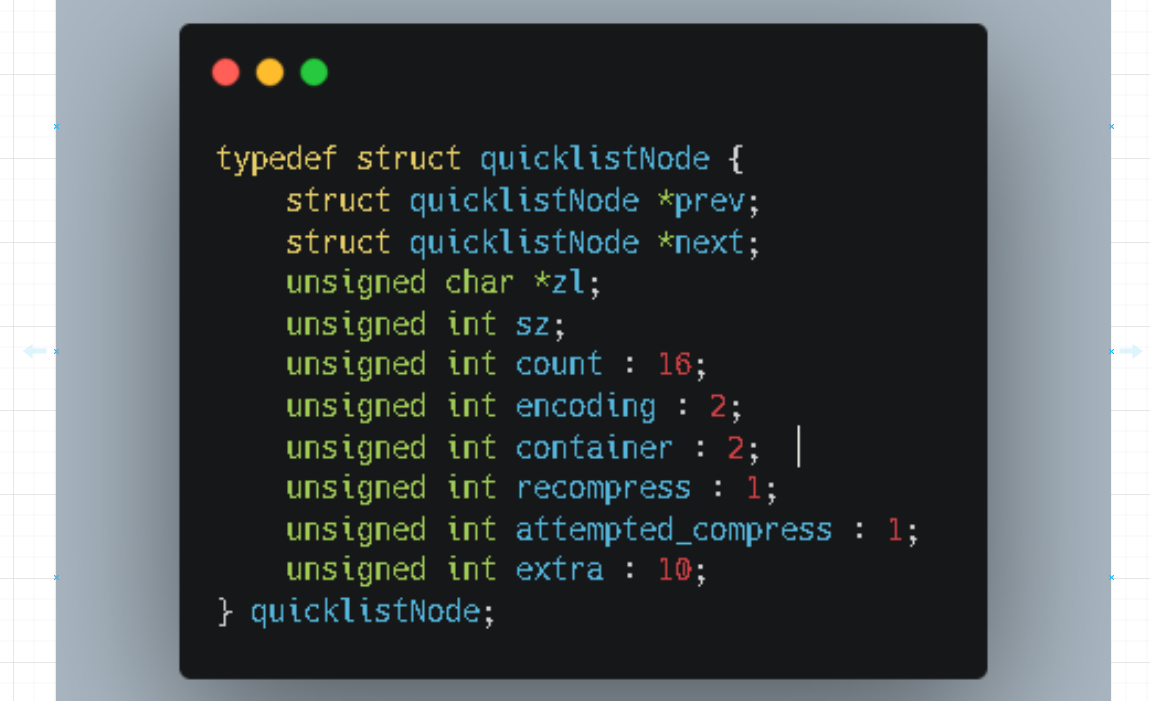

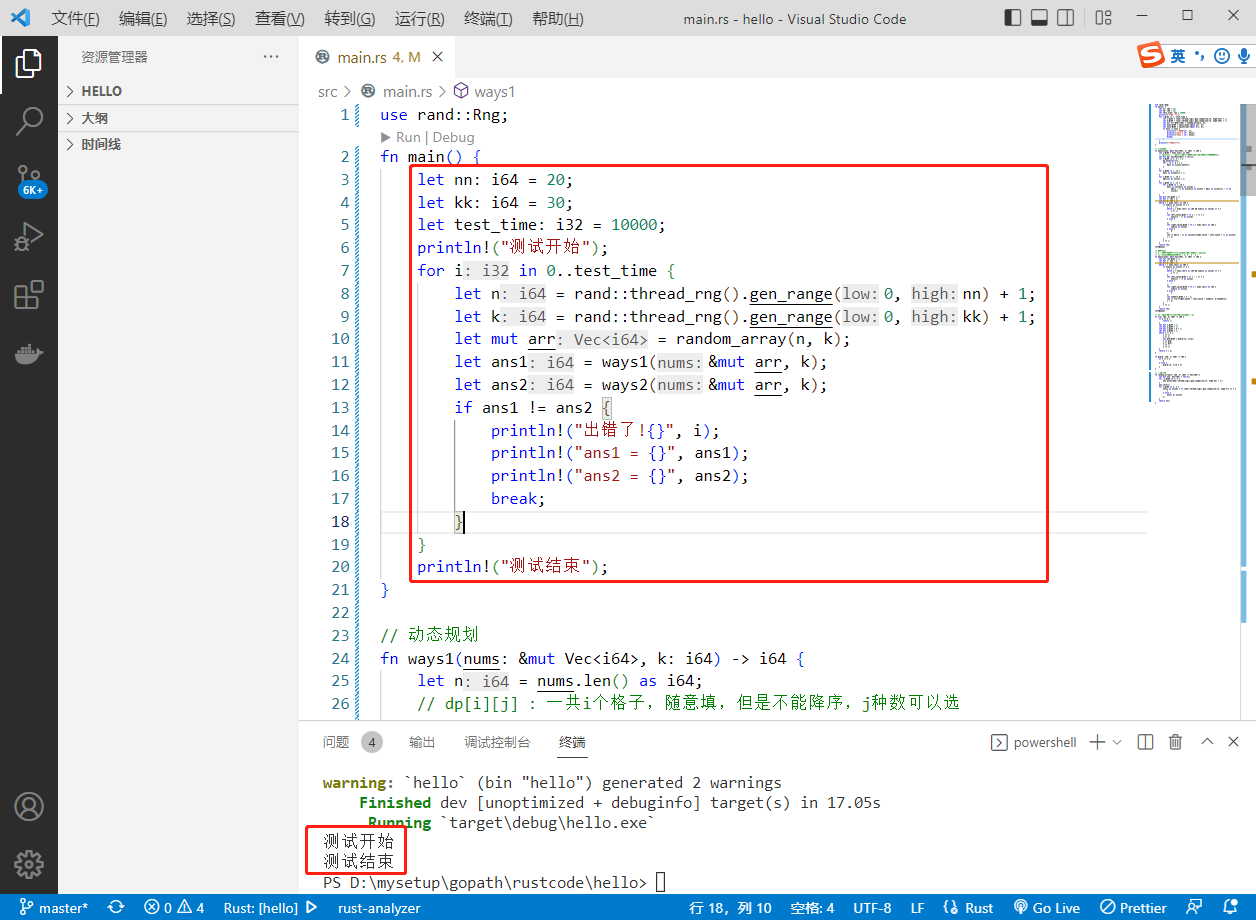

Redis, do you understand the list

51 communicates with the Bluetooth module, and 51 drives the Bluetooth app to light up

取消select的默认样式的向下箭头和设置select默认字样

第四期SFO销毁,Starfish OS如何对SFO价值赋能?

2022-07-07: the original array is a monotonic array with numbers greater than 0 and less than or equal to K. there may be equal numbers in it, and the overall trend is increasing. However, the number

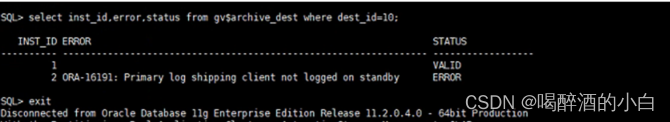

The standby database has been delayed. Check that the MRP is wait_ for_ Log, apply after restarting MRP_ Log but wait again later_ for_ log

随机推荐

Leetcode brush questions

My best game based on wechat applet development

图像数据预处理

【obs】Impossible to find entrance point CreateDirect3D11DeviceFromDXGIDevice

SDNU_ ACM_ ICPC_ 2022_ Summer_ Practice(1~2)

Redis, do you understand the list

STL--String类的常用功能复写

语义分割模型库segmentation_models_pytorch的详细使用介绍

基于卷积神经网络的恶意软件检测方法

取消select的默认样式的向下箭头和设置select默认字样

深潜Kotlin协程(二十二):Flow的处理

10.CNN应用于手写数字识别

大二级分类产品页权重低,不收录怎么办?

7.正则化应用

英雄联盟胜负预测--简易肯德基上校

13.模型的保存和载入

"An excellent programmer is worth five ordinary programmers", and the gap lies in these seven key points

5.过拟合,dropout,正则化

Image data preprocessing

Where is the big data open source project, one-stop fully automated full life cycle operation and maintenance steward Chengying (background)?