当前位置:网站首页>Control unit

Control unit

2022-07-05 05:34:00 【Li Junfeng】

Control Unit Control unit

In the control unit , By encoding instructions op 、func Field to perform logical operations , To output the corresponding control signal . This module still adopts gate level implementation , Although the code of gate level implementation is cumbersome and tedious , But it is more beneficial for us to understand the logic inside the circuit .

module CONUNIT(Z, Op, Func, Regrt, Se, Reg2reg, Pcsrc, Wmem, Aluc, Aluqb, Wreg);

input Z;

input [5:0] Op, Func;

output Regrt, Se, Wreg, Aluqb, Wmem, Reg2reg;

output [1:0] Pcsrc, Aluc;

wire R_type, I_add, I_sub, I_and, I_or, I_addi, I_andi, I_ori, I_lw, I_sw, I_beq, I_bne, I_J;

wire [5:0] Op_n,Func_n;

not (Op_n[0],Op[0]);

not (Op_n[1],Op[1]);

not (Op_n[2],Op[2]);

not (Op_n[3],Op[3]);

not (Op_n[4],Op[4]);

not (Op_n[5],Op[5]);

not (Func_n[0],Func[0]);

not (Func_n[1],Func[1]);

not (Func_n[2],Func[2]);

not (Func_n[3],Func[3]);

not (Func_n[4],Func[4]);

not (Func_n[5],Func[5]);

and (R_type, Op_n[5], Op_n[4], Op_n[3], Op_n[2], Op_n[1], Op_n[0]);

//R Type command ,op The fields are all 0

and (I_add, R_type, Func[5], Func_n[4], Func_n[3], Func_n[2], Func_n[1], Func_n[0]);

and (I_sub, R_type, Func[5], Func_n[4], Func_n[3], Func_n[2], Func[1], Func_n[0]);

and (I_and, R_type, Func[5], Func_n[4], Func_n[3], Func[2], Func_n[1], Func_n[0]);

and (I_or, R_type, Func[5], Func_n[4], Func_n[3], Func[2], Func_n[1], Func[0]);

and (I_addi, Op_n[5], Op_n[4], Op[3], Op_n[2], Op_n[1], Op_n[0]);

and (I_andi, Op_n[5], Op_n[4], Op[3], Op[2], Op_n[1], Op_n[0]);

and (I_ori, Op_n[5], Op_n[4], Op[3], Op[2], Op_n[1], Op[0]);

and (I_lw, Op[5], Op_n[4], Op_n[3], Op_n[2], Op[1], Op[0]);

and (I_sw, Op[5], Op_n[4], Op[3], Op_n[2], Op[1], Op[0]);

and (I_beq, Op_n[5], Op_n[4], Op_n[3], Op[2], Op_n[1], Op_n[0]);

and (I_bne, Op_n[5], Op_n[4], Op_n[3], Op[2], Op_n[1], Op[0]);

and (I_J, Op_n[5], Op_n[4], Op_n[3], Op_n[2], Op[1], Op_n[0]);

//j Type command , Jump

wire beq_Z, bne_Z_n, Z_n;

or (Regrt, I_addi, I_andi, I_ori, I_lw, I_sw, I_beq, I_bne, I_J);

// Determine the type of destination register according to the instruction type :R Type instruction destination register rd Store in [15:11],I Destination register of type instruction rt Store in [20:16],

// This signal is the control multiplexer mux1

or (Se, I_addi, I_lw, I_sw, I_beq, I_bne);

//16->32 Bit expansion , For instructions containing immediate numbers , control ext

or (Wreg, I_add, I_sub, I_and, I_or, I_addi, I_andi, I_ori, I_lw);

// Register heap enable signal , When instructions need to be written , The value is 1

or (Aluqb, I_add, I_sub, I_and, I_or, I_beq, I_bne, I_J);

// The multiplexer is controlled according to whether the instruction has an immediate number , about R Type command , The result is 1, Indicates the value output by the selection register , Otherwise 0, Means to select an immediate number

// control mux2

or (Aluc[1], I_and, I_or, I_andi, I_ori);//1 Represents a logical operation ,0 It means arithmetic operation

or (Aluc[0], I_sub, I_or, I_ori, I_beq, I_bne);

// control ALU The type of calculation , control alu

and (Wmem, I_sw, I_sw);

// Memory write enable signal ,1 It means that you can write

and (beq_Z, I_beq, Z);

not (Z_n, Z);

and (bne_Z_n, I_bne, Z_n);

or (Pcsrc[1], beq_Z, bne_Z_n, I_J);

and (Pcsrc[0], I_J, I_J);

// Branch jump signal , Control multiplexer mux4

or (Reg2reg, I_add, I_sub, I_and, I_or, I_addi, I_andi, I_ori, I_sw, I_beq, I_bne, I_J);

// Output signal control , Select from ALU Output or output from memory

endmodule

边栏推荐

- Double pointer Foundation

- Web APIs DOM node

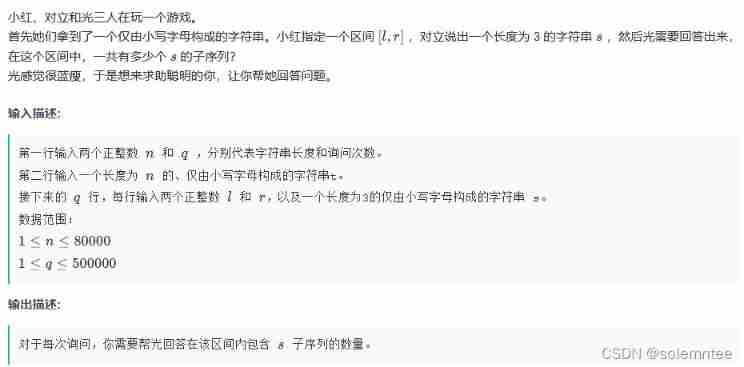

- Haut OJ 1352: string of choice

- [binary search] 34 Find the first and last positions of elements in a sorted array

- To the distance we have been looking for -- film review of "flying house journey"

- AtCoder Grand Contest 013 E - Placing Squares

- [allocation problem] 135 Distribute candy

- Codeforces Round #716 (Div. 2) D. Cut and Stick

- Sword finger offer 06 Print linked list from beginning to end

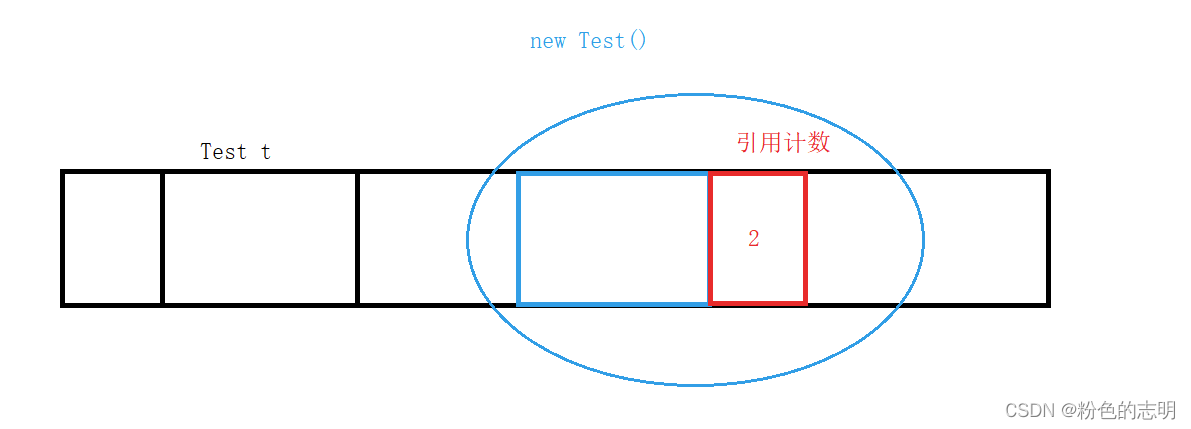

- 浅谈JVM(面试常考)

猜你喜欢

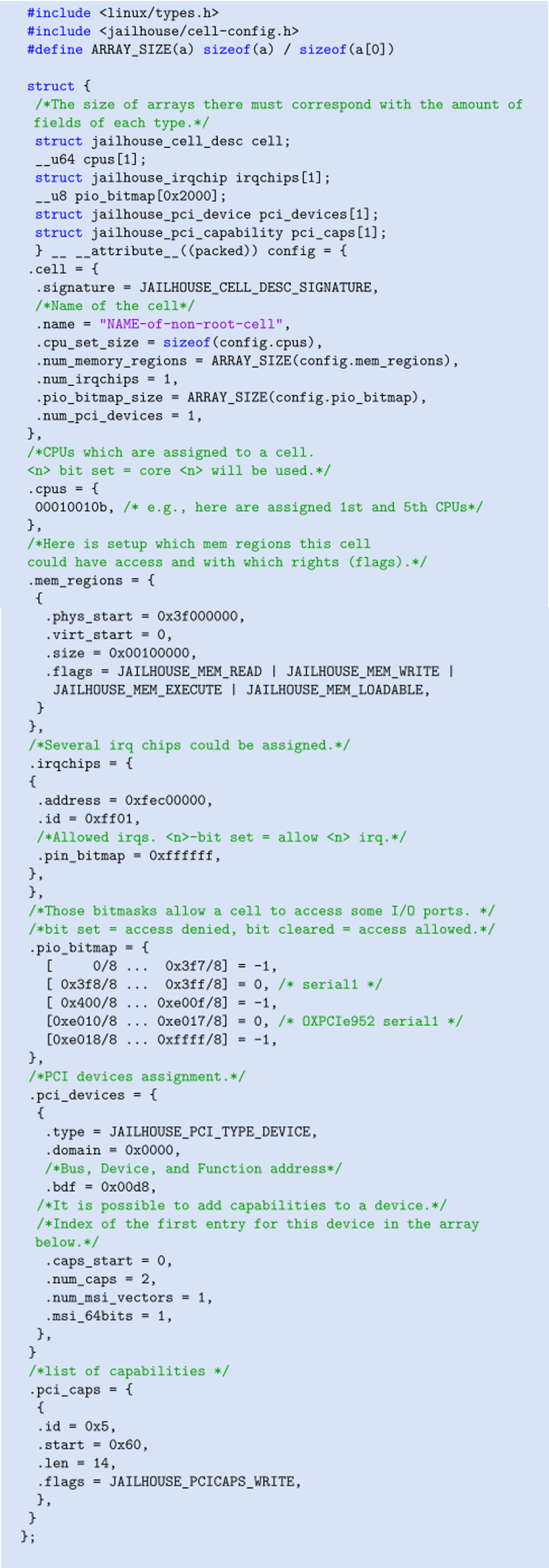

【Jailhouse 文章】Jailhouse Hypervisor

Web APIs DOM node

浅谈JVM(面试常考)

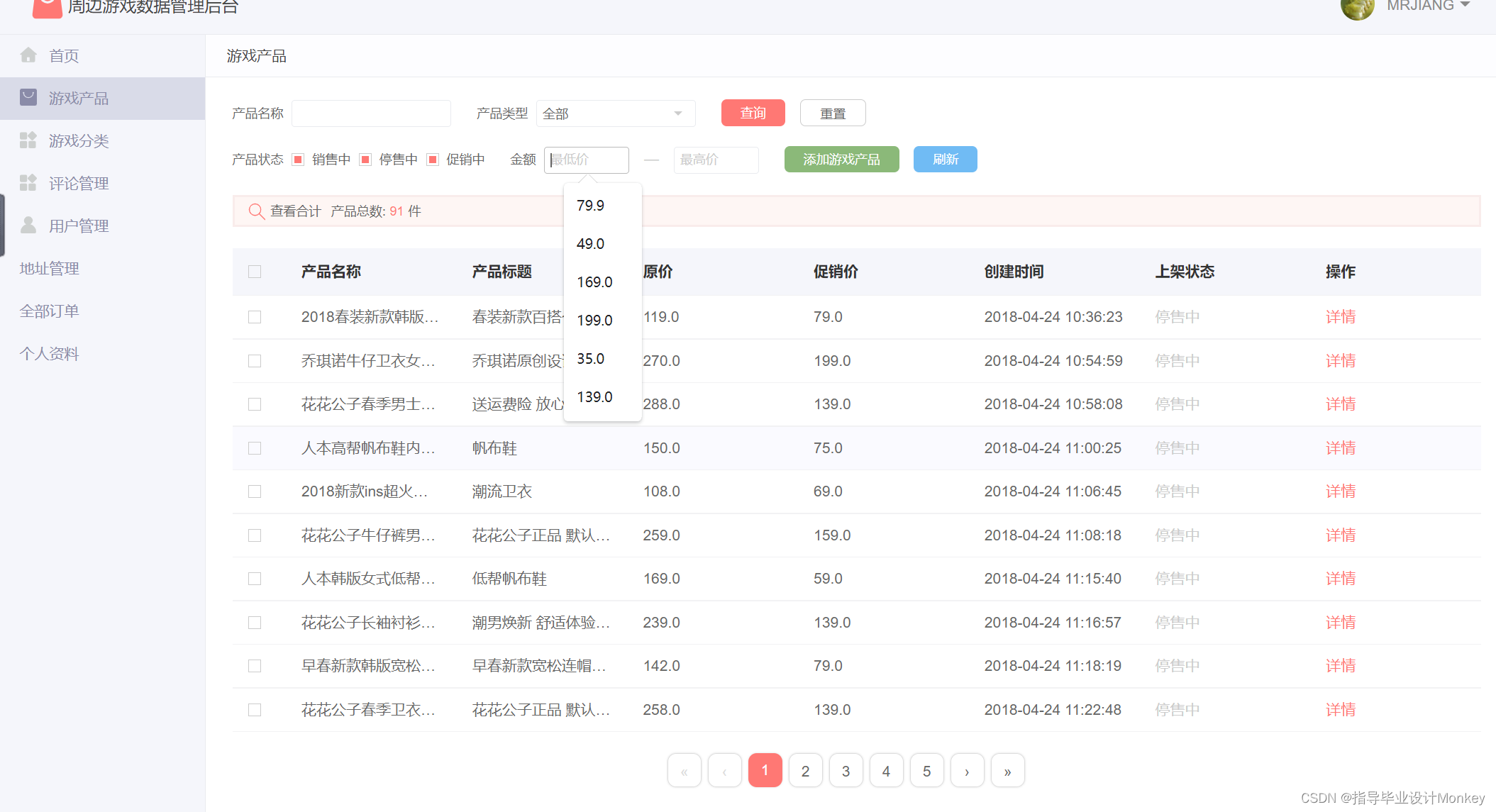

Graduation project of game mall

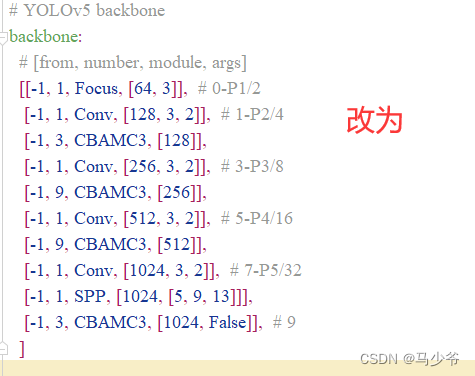

YOLOv5添加注意力机制

![[speed pointer] 142 circular linked list II](/img/f8/222a360c01d8ef120b61bdd2025044.jpg)

[speed pointer] 142 circular linked list II

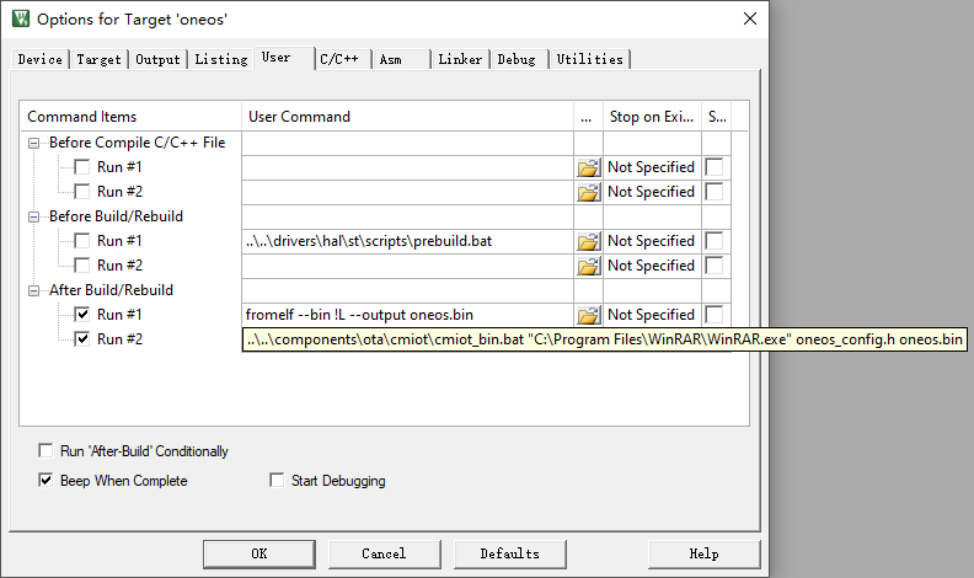

Remote upgrade afraid of cutting beard? Explain FOTA safety upgrade in detail

![[to be continued] [UE4 notes] L2 interface introduction](/img/0f/268c852b691bd7459785537f201a41.jpg)

[to be continued] [UE4 notes] L2 interface introduction

In this indifferent world, light crying

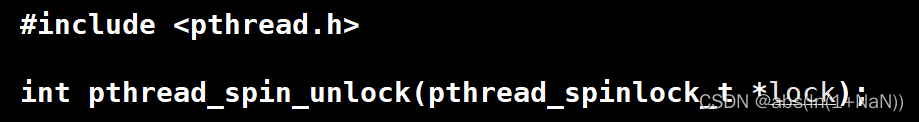

Hang wait lock vs spin lock (where both are used)

随机推荐

【ES实战】ES上的native realm安全方式使用

Animation scoring data analysis and visualization and it industry recruitment data analysis and visualization

2017 USP Try-outs C. Coprimes

[to be continued] I believe that everyone has the right to choose their own way of life - written in front of the art column

[to be continued] [depth first search] 547 Number of provinces

Annotation and reflection

智慧工地“水电能耗在线监测系统”

Double pointer Foundation

Reflection summary of Haut OJ freshmen on Wednesday

【Jailhouse 文章】Jailhouse Hypervisor

[binary search] 34 Find the first and last positions of elements in a sorted array

使用Electron开发桌面应用

YOLOv5-Shufflenetv2

【实战技能】如何做好技术培训?

PC寄存器

AtCoder Grand Contest 013 E - Placing Squares

Binary search basis

[speed pointer] 142 circular linked list II

Pointnet++ learning

CF1634E Fair Share