当前位置:网站首页>SD_ CMD_ RECEIVE_ SHIFT_ REGISTER

SD_ CMD_ RECEIVE_ SHIFT_ REGISTER

2022-07-05 07:07:00 【Eight four one one】

Catalog

1. Interface

- Normal clock reset soft reset

- Enter the current status of the entry in_current_state as well as sd Send the command line in_serial_cmd, Here's what's interesting , from sd The card was sent in_serial_cmd It is the single that makes up the response bit The signal

- Received bit Count in_has_receive_bit

- Response type in_long_response,1 Long 0 short

- Report crc Check for errors out_cmd_receive_crc_error

- Four response signals response[3:0]

input in_sd_clk ;

input hrst_n ;

input in_soft_reset ;

input [2:0] in_current_state ;

input in_serial_cmd ;

input [7:0] in_has_receive_bit ;

input in_long_response ;

output out_cmd_receive_crc_error ;

output response0 ;

output response1 ;

output response2 ;

output response3 ;

2. Response output generation

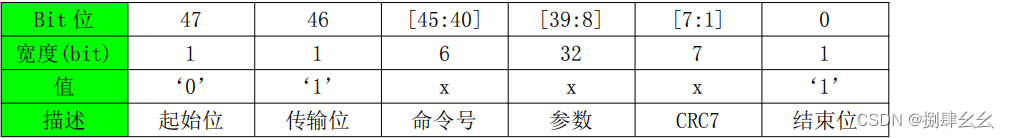

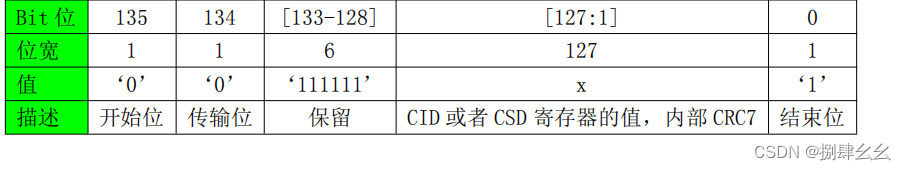

- The format of long response is shown in the following figure

- among start bit Not recorded , That is, from the transmission bit , We started from 8 Bit is also [7] Start shift deposit

- response3 The highest 8bit=0, be left over 24bit from in_serial_cmd Normal read

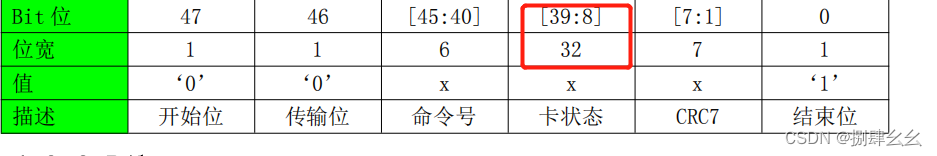

- Short response only response0 That's enough , The format is as follows :

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

begin

response0 <= 32'b0;

response1 <= 32'b0;

response2 <= 32'b0;

response3 <= 32'b0;

end

else if (!in_soft_reset)

begin

response0 <= 32'b0;

response1 <= 32'b0;

response2 <= 32'b0;

response3 <= 32'b0;

end

else if (in_current_state == `CMD_STATE_SEND)

begin

response0 <= 32'b0;

response1 <= 32'b0;

response2 <= 32'b0;

response3 <= 32'b0;

end

else if (in_current_state == `CMD_STATE_RECEIVE)

begin

if(in_long_response)

begin

if((in_has_receive_bit >= 7) && (in_has_receive_bit <=30))

response3 <= {

response3[30:0],in_serial_cmd};

else if((in_has_receive_bit >= 31) && (in_has_receive_bit <= 62))

response2 <= {

response2[30:0],in_serial_cmd};

else if((in_has_receive_bit >= 63) && (in_has_receive_bit <= 94))

response1 <= {

response1[30:0],in_serial_cmd};

else if((in_has_receive_bit >= 95) && (in_has_receive_bit <= 126))

response0 <= {

response0[30:0],in_serial_cmd};

end

else if((in_has_receive_bit >= 7) && (in_has_receive_bit <= 38))

response0 <= {

response0[30:0],in_serial_cmd};

end

end

3. Received by sd From card crc7 Check the signal

- First order crc yes 8 Bit

- Also by in_serial_cmd Single line transmission , Therefore, it is also necessary to move and deposit

- Appearance correspondence crc The position in the format is as follows :

- Short corresponding crc The position in the format is as follows :

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

receive_cec_reg <= 7'b0;

else if (!in_soft_reset)

receive_cec_reg <= 7'b0;

else if (in_current_state == `CMD_STATE_SEND)

receive_cec_reg <= 7'b0;

else if (in_current_state == `CMD_STATE_RECEIVE)

begin

if (in_long_response)

begin

if((in_has_receive_bit >= 127) && (in_has_receive_bit <= 133))

receive_cec_reg <= {

receive_cec_reg[5:0],in_serial_cmd};

end

else begin

if((in_has_receive_bit >= 39) && (in_has_receive_bit <= 45))

receive_cec_reg <= {

receive_cec_reg[5:0],in_serial_cmd};

end

end

end

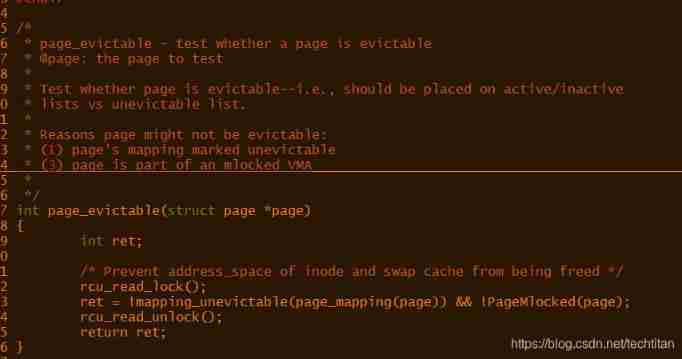

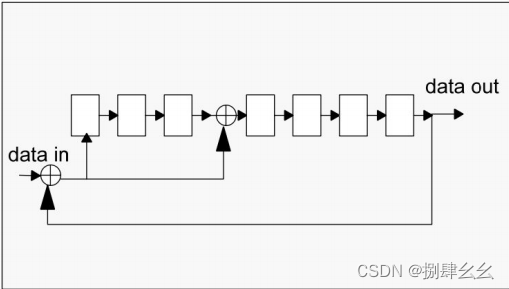

4. Calculate for yourself crc7 Value

- You need to calculate again crc The value of comes from sd Card received crc compare

- If the same , Then the command is ok , If it is not the same , Report an error out_cmd_receive_crc_error

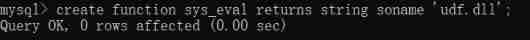

- Calculation crc7 Methods :[0] and [3] These two bits need to be XOR , Other shifts are ok , See the picture below

always @(posedge in_sd_clk or negedge hrst_n) begin

if(!hrst_n)

receive_cec_reg <= 7'b0;

else if (!in_soft_reset)

receive_crc_reg <= 7'b0;

else if(in_current_state == `CMD_STATE_SEND)

receive_crc_reg <= 7'b0;

else if (in_current_state == `CMD_STATE_RECEIVE)

begin

if(in_long_response)

begin

if((in_has_receive_bit >= 7) && (in_has_receive_bit <=126))

begin

generate_crc_reg[0] <= in_serial_cmd^generate_crc_reg[6];

generate_crc_reg[1] <= generate_crc_reg[0];

generate_crc_reg[2] <= generate_crc_reg[1];

generate_crc_reg[3] <= in_serial_cmd^generate_crc_reg[6]^generate_crc_reg[2];

generate_crc_reg[4] <= generate_crc_reg[3];

generate_crc_reg[5] <= generate_crc_reg[4];

generate_crc_reg[6] <= generate_crc_reg[5];

end

end

else

begin

if((in_has_receive_bit >= 0) && (in_has_receive_bit <=38))

begin

generate_crc_reg[0] <= in_serial_cmd^generate_crc_reg[6];

generate_crc_reg[1] <= generate_crc_reg[0];

generate_crc_reg[2] <= generate_crc_reg[1];

generate_crc_reg[3] <= in_serial_cmd^generate_crc_reg[6]^generate_crc_reg[2];

generate_crc_reg[4] <= generate_crc_reg[3];

generate_crc_reg[5] <= generate_crc_reg[4];

generate_crc_reg[6] <= generate_crc_reg[5];

end

end

end

end

5. contrast crc7 produce out_cmd_receive_crc_error

- We received receive_crc_reg

- Later we calculated generate_crc_reg

- After receiving, that is 135 perhaps 47bit You can make a comparison

always @(posedge in_sd_clk or negedge hrst_n) begin

if (!hrst_n)

out_cmd_receive_crc_error <= 1'b0;

else if (!in_soft_reset)

out_cmd_receive_crc_error <= 1'b0;

else if (in_current_state == `CMD_STATE_SEND)

out_cmd_receive_crc_error <= 1'b0;

else if (in_current_state == `CMD_STATE_RECEIVE)

begin

if (in_long_response)

begin

if(in_has_receive_bit == 134)

out_cmd_receive_crc_error <= !(generate_crc_reg == receive_crc_reg);

end

else if (in_has_receive_bit == 46)

out_cmd_receive_crc_error <= !(generate_crc_reg == receive_crc_reg);

end

end

边栏推荐

猜你喜欢

随机推荐

使用paping工具进行tcp端口连通性检测

[tf] Unknown: Failed to get convolution algorithm. This is probably because cuDNN failed to initial

2022.06.27_每日一题

基于FPGA的一维卷积神经网络CNN的实现(八)激活层实现

Inftnews | drink tea and send virtual stocks? Analysis of Naixue's tea "coin issuance"

Written examination notes

并发编程 — 如何中断/停止一个运行中的线程?

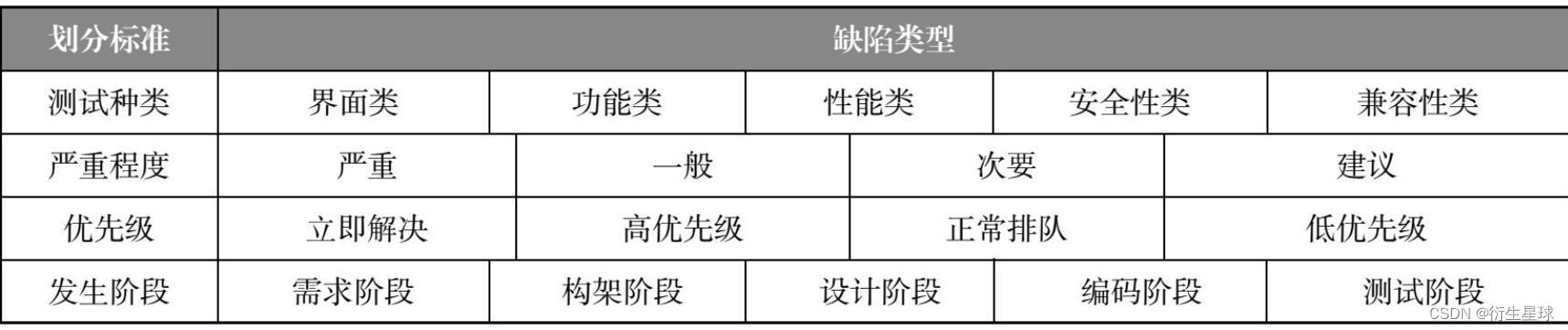

【软件测试】05 -- 软件测试的原则

An article was opened to test the real situation of outsourcing companies

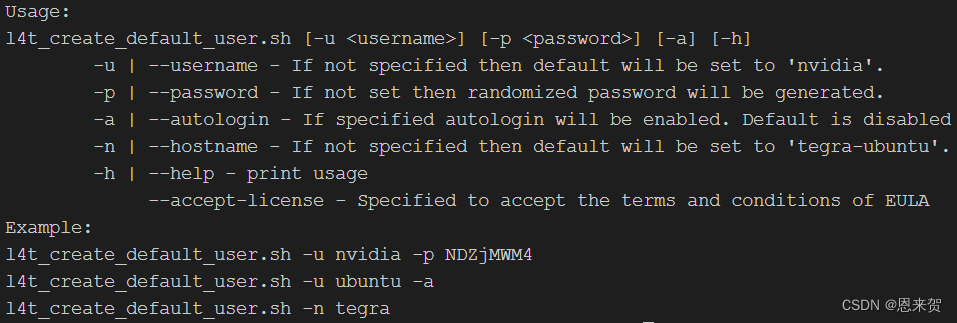

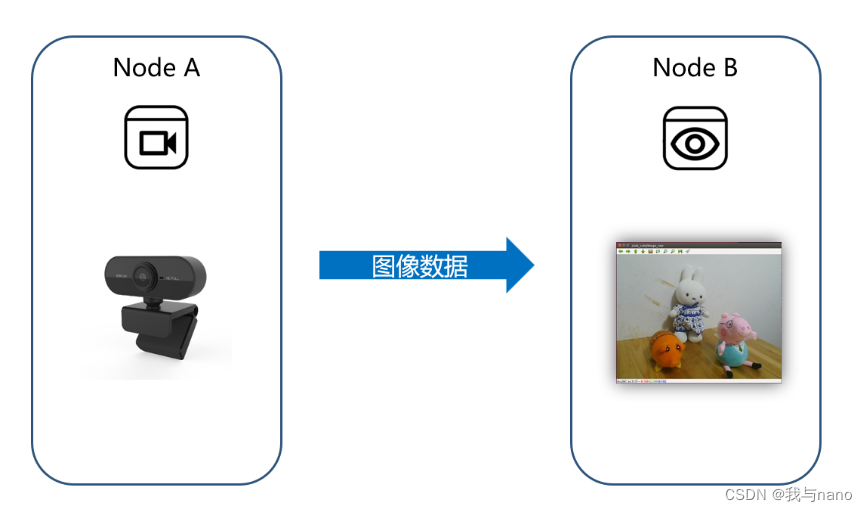

ROS2——安装ROS2(三)

6-4 search by serial number of linked list

Error: “MountVolume.SetUp failed for volume pvc 故障处理

[software testing] 05 -- principles of software testing

Get class files and attributes by reflection

PHY drive commissioning - phy controller drive (II)

Mutual transformation between two-dimensional array and sparse array (sparse matrix)

PowerManagerService(一)— 初始化

Volcano 资源预留特性

Preemption of CFS scheduling

Sre core system understanding

![[untitled]](/img/d5/2ac2b15818cf66c241e307c6723d50.jpg)