当前位置:网站首页>Su embedded training - Day7

Su embedded training - Day7

2022-07-08 00:58:00 【Light chasing rain】

List of articles

One Makefile brief introduction

1.1 What is? Makefile?

Makefile It is a tool for project management . Its essence is a document , This file stores the rules for compiling the code .Makefile According to the document " Time stamp " To decide whether the files in the project need to be compiled this time .

1.2 What is? make?

make It's an executable program , stay /usr/bin It is stored in the directory if /usr/bin This program cannot be found in the directory , Need to use sudo apt-get install make To install this program . When executing on the terminal make When , It will parse the current directory Makefile file . And according to Makefile Compile the current project according to the Compilation Rules in .

1.3 Why use ?

In the actual development process , Only use gcc Command is very inefficient when compiling programs , There are two main reasons :

(1) Programs are often composed of multiple source files , The more source files , that gcc The longer the command . Besides , Various Compilation Rules will also be increased gcc The complexity of the command line , So in the process of development and debugging , By input gcc It is troublesome to compile programs from the command line .

(2) In the whole process of program development , The workload of debugging accounts for 70% above . In the process of debugging the program , Generally, only part of the source files will be modified during each debugging . But in the use of gcc When compiling programs from the command line ,gcc Will compile those source files that have not been modified , This will affect the overall efficiency of compilation .

In order to improve the efficiency of compiler , Many are based on windows All development tools on the platform provide project managers . Users only need to click one “make” Button can start the project manager to automatically compile the whole program , There is no need for human intervention in the whole compilation process . This kind of project manager is vividly called automatic project manager .

GCC It provides a semi-automatic project manager Make. The so-called semi automation refers to the compilation rules that require manual programming before using the project manager , All Compilation Rules are saved in Makefile In file , The fully automated project manager will be automatically generated before compiling the program Makefile file .

1.4. Superiority

(1) Easy to use . Through the command ”make“ You can start it Make The project manager compiles the program , So it is no longer necessary to input every time gcc Command line .Make After startup, it will be based on Makefile The compilation rule command in the file automatically compiles and links the source file , Final generation of executable .

(2) High debugging efficiency . In order to improve the efficiency of compiler ,Make The modification time of each source file will be checked ( Time stamp ). Only the source files modified after the last compilation will be compiled and linked in the next compilation process , In this way, the redundant compilation workload can be avoided . To ensure that the source file has the correct timestamp , The correctness of the operating system time must be guaranteed ( Be careful VMWare The virtual machine CMOS Is the time right ).

Two .makefile

2.1 makfile Compilation Rules

Make The project manager is completely based on Makefile The compilation rule commands in the file work ,Makefile The document consists of the following three basic contents :

(1) The target file that needs to be generated (Target file)

(2) The dependent files needed to generate the target file (dependency)

(3) Generate the compilation rule command line of the target file (command)

These three contents are organized in the following format :

target file:dependency file

command

among ,makefile Rules are written command A key must be added before the command .

Makefile The project manager will check the timestamp of each dependent file when compiling the program , Once the timestamp of a dependent file is found to be newer than the target file , Will execute the rule command of the target file to regenerate the target file . This process is called dependency rule checking of the target file . When relying on rule checking Make One of the core tasks of the project manager . Here is the compiler test( from a.c b.c and b.h form ) As an example to describe Make Working process of .

//a.c

#include "b.h"

int main()

{

hello();

return 0;

}

//b.h

void hello();

//b.c

#include <stdio.h>

void hello()

{

printf("hello");

}

//makefile

test: a.o b.o

cc a.o b.o -o test // -o Specify output file name

a.o:a.c b.h

cc -c a.c //-c Just compile, not link , Generate target file

b.o:b.c

cc -c b.c

Make Project manager compilation Test The procedure is as follows :

(1) Make The project manager will first read in the current directory Makefile file

(2) lookup Makefile The first target file in the file ( In this case test), The document is also Make The final goal of this compilation task of the project manager .

(3) Put the target file test The dependent file of is regarded as the target file for dependency rule checking . This is a recursive checking process , In this case, we put a.o and b.o Check the respective dependency rules as the target file .Make It will be handled according to the following three situations .

① If there are no or missing dependent files in the current directory , Then execute its rule command to generate the dependent file ( If you lack a.o, Then execute the command ”cc -c a.c“ Generate a.o).

② If there are dependent files , Then take it as the target file to check the dependency rules ( If a.c Than a.o new , Then execute the command ”cc -c a.c“ to update a.o)

③ If the target file is newer than all dependent files , Do not deal with .

(4) After the third step of recursion , You will get the target file test All the latest dependent files , next Make It will be handled according to the following three situations :

① If the target file test non-existent ( For example, the first compilation ), Execute the rule command to generate test

② If the target file test There is , But there is more than test Want a new dependency file , Then execute the rule command update test.

③ Target file test There is , And newer than all dependent files , Do not deal with .

2.2 Makefile Feature introduction

The program with more source files , The more complex the Compilation Rules will be , Lead to Makefile The more complex the file is . In order to simplify the Makefile Compiling , Enrich the methods and means of compiling programs ,Makefile It provides many syntax mechanisms similar to high-level programming languages .

2.2.1 Variable

stay Makefile In file , There are a lot of file names , And these file names are repeated . So when there are many source files , It is easy to miss or write the wrong file name . And once the name of the source file changes , It is also easy to cause errors that are inconsistent with other file names . therefore ,Makefile Variable names are provided instead of file names . How to use variables :

$ ( Variable name ) or ${ Variable name }

for example :

obj = a.o b.o

test : $(obj)

cc -o test $(obj)

a.o:a.c b.h

cc -c a.c

b.o:b.c

cc -c b.c

The Makefile Variables used in obj Instead of ”a.o b.o“, When the source file name is changed or the source file is added or deleted , Just for variables obj The value of Jin watermelon can be modified accordingly , In this way, you can avoid inconsistent file names or missing errors .Makefile The names of variables in can use characters , Numbers and underscores , But note that variable names are case sensitive .

The way variables are defined :

( One ) adopt ”=“ To achieve . for example :

a1 = $(s2);

a2 = $(s3);

a3 = a.o

In this way, variables a1 The value of is a.o, That is to say, the preceding variables can be defined by the following variables . But when defining variables in this way , To prevent the occurrence of dead circulation .

( Two ) adopt ”:=“ To achieve . for example :

a1:= a.o

a2:= $(a1) b.o

In this way, variables a1 The value of is a.o, Variable a2 The value of is a.o b.o. for example :

a1:= $(a2) b.o

a2:= a.o

Variables in this way a1 The value of is b.o, instead of ”a.o b.o“, That is to say, the preceding variables cannot be defined by the following variables .

( 3、 ... and ) adopt ”+=“ To achieve . for example :

a1 = a.o;

a1 += b.o;

In this way, variables a1 The value of is ”a.o b.o“. in other words ”+=“ You can add values to variables . Equivalent to the following example :

a1 = a.o;

a1:=$(a1) b.o

It can be seen that ,Makefile Of ”+=“ and c In language "+=" It's very similar .

( Four ) adopt "?=" To achieve . for example :

a1 := a.o

a1 ?= b.o

In this way, variables a1 The value of is a.o, instead of b.o, in other words , If the variable a1 It has been defined above , Then the following definition is invalid .

2.2.2 Automatic derivation

To further simplify Makefile Writing ,Make The project manager provides automatic derivation . The automatic derivation function defaults that each target file has a corresponding dependent file . for example ,a.o The file has dependent files a.c With the corresponding , In this way Makefile There is no need to specify the dependent file name corresponding to the target file . Besides , The automatic derivation function can also deduce the basic compilation rule commands corresponding to the target file . for example ,a.o The rule command of the file is ”gcc -c -o a.c“

for example :

obj = a.o b.o

test:$(obj)

cc -o test $(obj)

The result is :

[email protected]:~/81-makefile/test$ make

cc -c -o a.o a.c

cc -c -o b.o b.c

cc -o test a.o b.o

You can see ,Makefile The object files are derived respectively a.o and b.o Rule commands ”cc -c -o a.o a.c“ And ”cc -c -o b.o b.c“.

Fake target : Pseudo target is not a real target file , It's just a symbol . In order not to be confused with the real object file , Best use ”.PHONY“ Identify the pseudo target . for example :

obj = a.o b.o

.PHONY: all

all: test $(obj)

test:$(obj)

cc -o test $(obj)

.PHONY:clean

clean:

rm -rf *.o test

test_dir = ~/81-makefile/t_d

.PHONY: install

install:

mkdir $(test_dir)

cp test $(test_dir)

.PHONY: uninstall

uninstall:

rm -rf $(test_dir)

(1) all. Run the command ”make all“ after ,Make Will be able to all As the ultimate goal . Because the pseudo target and the real target have dependent files , therefore Make Will update all The dependent files of test,a.o and b.o. As shown below :

[email protected]:~/81-makefile/test$ make all

cc -c -o a.o a.c

cc -c -o b.o b.c

cc -o test a.o b.o

(2) clean. Run the command ”make clean“ after ,Make Will execute the order :rm -rf *.o test,, So all of .o Document and test It's all deleted . As shown below :

[email protected]:~/81-makefile/test$ make clean

rm -rf *.o test

(3)install. Run the command ”make install“ after ,Make Will execute commands in sequence ”mkdir $(test_dir)“ and ”cp test $(test_dir)“, hold test File copy to test_dir Variable to the specified directory ( Here is just a simulation of the installation process , It is not a real installation method ), As shown below :

[email protected]:~/81-makefile/test$ make install

mkdir ~/81-makefile/t_d

cp test ~/81-makefile/t_d

(4)uninstall . Run the command ”make clean“ after ,Make Will execute the order ”rm -rf $(test_dir)“. In this way, you can put variables test_dir Delete the specified directory and all the files in it . As shown below .

[email protected]:~/81-makefile/test$ make uninstall

rm -rf ~/81-makefile/t_d

stay Makefile in , Pseudo targets are very useful . for example , In recursive compilation , In parallel compilation and other occasions , Using pseudo targets can easily control the compilation process .

2.3 File search

In order to facilitate management and organization , The source files of the program are placed in different subdirectories according to different functions . But after the source files are stored dispersedly ,Makefile How can I find these source files ?Makefile There are two ways .

(1)VPATH = Catalog : Catalog …

for example :

export VPATH= /a : /b

Make When the files cannot be found in the current path, they will be searched in order /a and /b Catalog

(2)vpath. and VPATH The difference is ,vpath It's not a variable , It's keywords , Its function and VPATH similar , But the way of use is more flexible .vpath The usage of is

vpath Pattern Catalog : Catalog …

for example :

vpath %.c /a : /b

Make When the file cannot be found in the current path , Find in order /a and /b All of the... In the catalog C file .vpath You can also use different search modes for different paths . for example :

vpath %.c /a : /b

make When the files cannot be found in the current path, they will be searched in order /a and /b All of the... In the catalog C file .vpath You can also use different search modes for different paths . for example :

vpath %.c /a

vpath %.h /b

Make When the source file cannot be found in the current path, you will first find /a In the catalog C file , Then look for /b The header file in the directory . for example , First, in the /home Create a new directory under the directory b, And then put b.c Put the file in the directory b in .

VPATH = /home/b

obj = a.o b.o

.PHONY : all

all:test $(obj)

test:$(obj)

cc -o test $(obj)

practice :

Compile multiple files Makefile Add variables

TARGET?=demo

OBJS:=main.o add.o sub.o

CC:=gcc

CFLAGS:= -c -o

CFLAGSs:=-o

$(TARGET):$(OBJS)

$(CC) $(OBJS) $(CFLAGSs) $(TARGET)

main.o:main.c

$(CC) main.c $(CFLAGS) main.o

add.o:add.c

$(CC) add.c $(CFLAGS) add.o

sub.o:sub.c

$(CC) sub.c $(CFLAGS) sub.o

clean:

rm $(OBJS) $(TARGET)

2.4 Makefile Wildcard in

Makefile Wildcard in :* and %

stay Makefile Using commands in , This * Is the wildcard of the command

% It is Makefile Wildcards unique to files

#aa=`ls *.c`

# Order replacement

aa=$(shell ls *.c)

# stay Makefile One of them shell, Put the order on shell In the implementation of ,

# Assign the result of execution to aa Variable

2.5Makefile Special characters in commands

[email protected]: The goal is

$<: The first to rely on

$^: All dependence

$*: The field after the suffix is removed from the target

practice :

1. Multi file compilation optimization version

TARGET?=demo

OBJS:=main.o add.o sub.o

CC:=gcc

CFLAGS:= -c -o

CFLAGSs:=-o

$(TARGET):$(OBJS)

$(CC) $(OBJS) $(CFLAGSs) $(TARGET)

%.o:%.c

$(CC) $< $(CFLAGS) [email protected]

clean:

rm $(OBJS) $(TARGET)

2.6 conditional

(1) and C Conditional compilation of language is similar ,make You can also judge conditions at runtime , Then enter the branch to continue compiling , The writing format of conditional judgment is :

Conditional expression

If the text segment is really executed

endif

perhaps

Conditional expression

If the text segment is really executed

else

If the false execution of the text segment

endif

(2) Four forms of conditional expressions

1> ifeq( Parameters 1, Parameters 2). effect : Compare parameters 1 And parameters 2 Whether the value of is the same , The same is true , Difference is false

2> ifneq( Parameters 1, Parameters 2). effect : Compare parameters 1 And parameters 2 Whether the value of is the same , Difference is true , Same as false

3> ifdef( Parameters ). effect : If the parameter is not empty, it is true , Empty is false .

4> ifndef( Parameters ). effect : Parameter null is true , Not empty but false .

for example :

a1 = a.o

a2 = b.o

ifeq ($(a1),$(a2))

a1 = x.o

else

a2 = y.o

Variable a1 The value of is a.o, Variable a2 The value of is y.o

Two 、 Sub documents

main.c

#include "func.h"

int main(int argc, const char *argv[])

{

func();

printf("a + b = %d\n",add(100,200));

return 0;

}

func.c

#include "func.h"

void func()

{

printf("hello world!\n");

}

int add(int x,int y)

{

return x + y;

}

func.h

```c

#ifndef _FUNC_H_

#define _FUNC_H_

#include <stdio.h>

void func();

int add(int x,int y);

#endif

3、 ... and 、gdb

gdb( Code debugging tools ) Use

compile :

gcc -g ***.c -o ***

-g : Add debugging information

function :

gdb ./ Executable file

After running :

(gdb) Input gdb command

Check the file source code (list Shorthand for l)

(gdb) l Show source code , Default backward 10 That's ok

(gdb) l num around num Show 10 That's ok

(gdb) l - Show forward num That's ok

(gdb) l start,end Show from start Start to end The ending line

To set breakpoints (break Shorthand for b)

(gdb) b Line number

(gdb) b Function name

disable + The number of the breakpoint Disable a breakpoint

enable + The number of the breakpoint Enable a breakpoint

delete + The number of the breakpoint Delete a breakpoint

View the setting information of the breakpoint (info)

(gdb) info b

Run code (run Shorthand for r)

(gdb) r

Look at the value of the variable (print Abbreviation p)

(gdb) p i

Resume the program (continue Shorthand for c)

(gdb) c

Step by step (next Shorthand for n)

(gdb) n Before single step , Must be executed first run

View help information (help Shorthand for h)

(gdb) h command

If in (gdb) Don't enter anything behind , Directly enter ,

Execute the last input instruction by default

Exit debugging state (quit Shorthand for q)

(gdb) q

Four 、 Mail list

1. adopt makefile Management code

2. Each sub function :

a: Add users ( Continuous addition )

b: To view the user ( Sort by initials )

c: Search users ( Two ways :id, user name )

d: Delete user information

e: Modify user information

3. Encapsulate the string processing function by yourself

- Acceptance after years

边栏推荐

- STL -- common function replication of string class

- Introduction to paddle - using lenet to realize image classification method II in MNIST

- Qt添加资源文件,为QAction添加图标,建立信号槽函数并实现

- 11.递归神经网络RNN

- Kubernetes static pod (static POD)

- Password recovery vulnerability of foreign public testing

- C# ?,?.,?? .....

- 大二级分类产品页权重低,不收录怎么办?

- German prime minister says Ukraine will not receive "NATO style" security guarantee

- 1293_ Implementation analysis of xtask resumeall() interface in FreeRTOS

猜你喜欢

Introduction to ML regression analysis of AI zhetianchuan

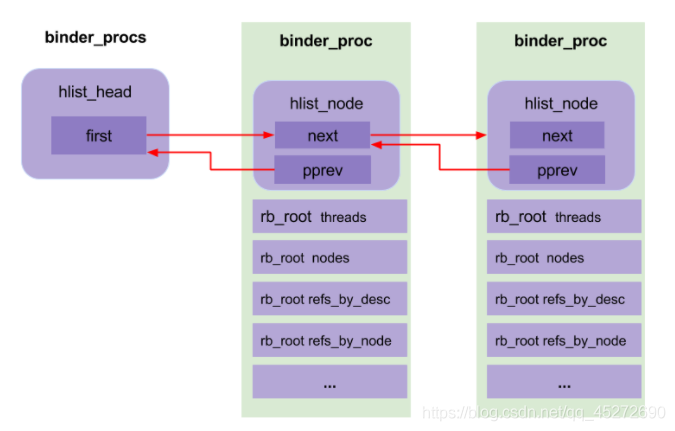

Binder core API

My best game based on wechat applet development

完整的模型训练套路

![[necessary for R & D personnel] how to make your own dataset and display it.](/img/50/3d826186b563069fd8d433e8feefc4.png)

[necessary for R & D personnel] how to make your own dataset and display it.

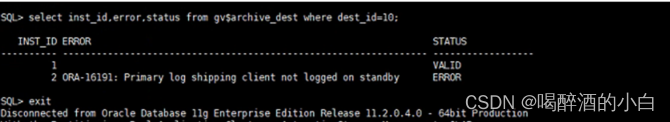

The standby database has been delayed. Check that the MRP is wait_ for_ Log, apply after restarting MRP_ Log but wait again later_ for_ log

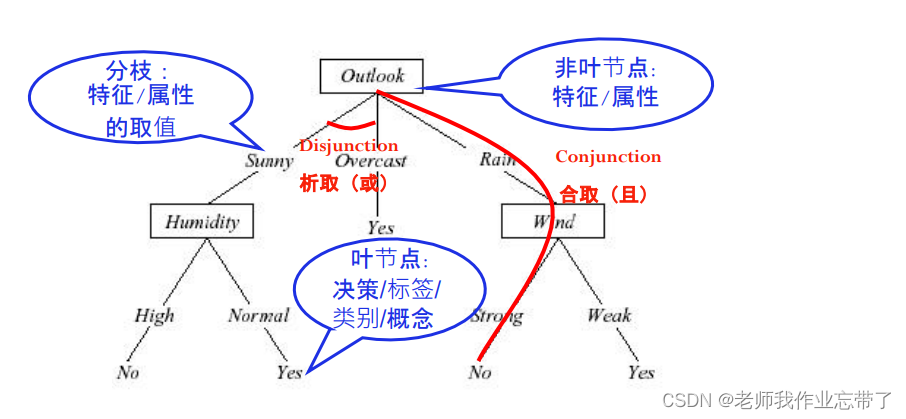

AI zhetianchuan ml novice decision tree

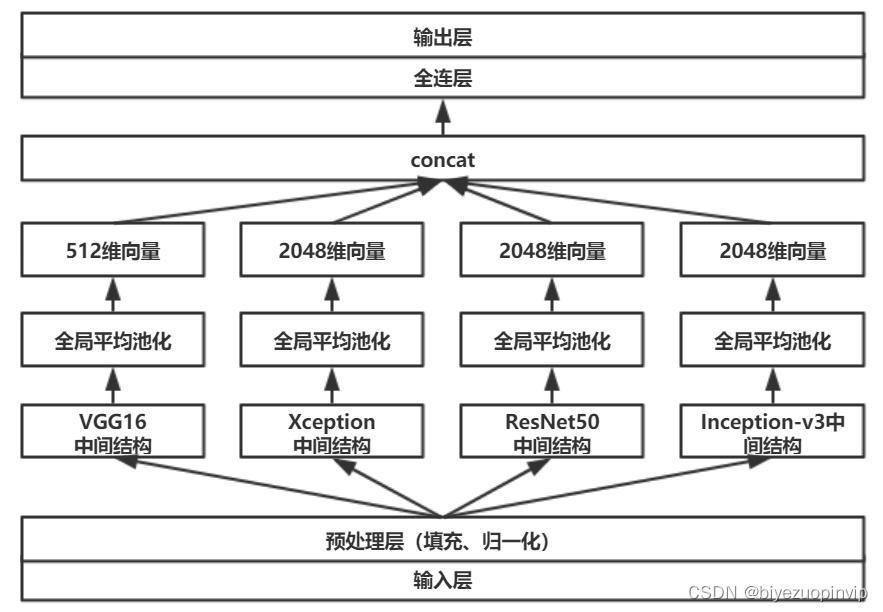

Malware detection method based on convolutional neural network

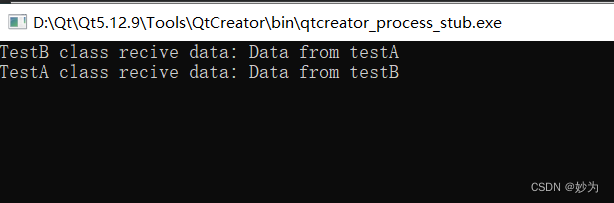

QT establish signal slots between different classes and transfer parameters

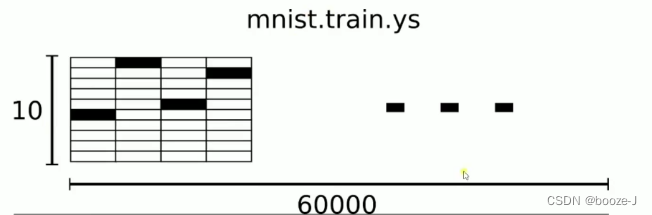

3.MNIST数据集分类

随机推荐

fabulous! How does idea open multiple projects in a single window?

How does starfish OS enable the value of SFO in the fourth phase of SFO destruction?

Binder core API

【愚公系列】2022年7月 Go教学课程 006-自动推导类型和输入输出

STL--String类的常用功能复写

Leetcode brush questions

10.CNN应用于手写数字识别

接口测试要测试什么?

Summary of weidongshan phase II course content

语义分割模型库segmentation_models_pytorch的详细使用介绍

Prediction of the victory or defeat of the League of heroes -- simple KFC Colonel

Application practice | the efficiency of the data warehouse system has been comprehensively improved! Data warehouse construction based on Apache Doris in Tongcheng digital Department

Deep dive kotlin synergy (XXII): flow treatment

Course of causality, taught by Jonas Peters, University of Copenhagen

Codeforces Round #804 (Div. 2)(A~D)

手写一个模拟的ReentrantLock

Cause analysis and solution of too laggy page of [test interview questions]

Interface test advanced interface script use - apipost (pre / post execution script)

完整的模型验证(测试,demo)套路

3.MNIST数据集分类