当前位置:网站首页>Learning record: use stm32f1 watchdog

Learning record: use stm32f1 watchdog

2022-07-06 15:33:00 【Bitter tea seeds】

Catalog

1.3、 Register access protection

1.4、 To configure an independent watchdog

2.3、 Configuration steps of window watchdog

( Reference resources STM32 Chinese Reference Manual )

Preface

In the microcomputer system composed of single chip microcomputer , Because the work of single chip microcomputer is often affected by External electromagnetic field Interference of , Cause the program to run and fly , And fall into a dead circle , The normal operation of the program is interrupted , The system controlled by single chip microcomputer cannot continue to work , It will bring the whole system to a standstill , Unforeseen consequences , Therefore, for the consideration of real-time monitoring the running state of single chip microcomputer , A module or chip specially used to monitor the running state of single chip microcomputer program , Be commonly called “ watchdog ”(watchdog) .

STM32F10xxx Built in two watchdog , Provides a higher level of security 、 Accuracy of time and flexibility of use . Two watchdog devices ( Independent watchdog and window watchdog ) It can be used to detect and solve faults caused by software errors ; When the counter reaches the given timeout value , Trigger an interrupt ( Only applicable to window watchdog ) Or generate system reset .

One 、 Independent watchdog

Independent watchdog (IWDG) By dedicated 40Khz Low speed clock (LSI) drive ,LSI It's a RC The clock . Even if the master clock fails, it still works . Window guard Dog from APB1 The clock driver obtained after clock frequency division , Detect abnormal application lateness through configurable time window Or premature operation .

IWDG( Independent watchdog ) Most suitable for those who need a watchdog as an outside of the main program , Able to work completely independently , And be careful about time Occasions with low requirements .WWDG( Window watchdog ) Best for applications that require a watchdog to work in a precise timing window .

1.1、 IWDG Main performance

1. Free running decrement counter ;2. The clock consists of independent RC oscillator Provide ( It can work in stop and standby modes ) ;3. When the watchdog is activated , be The counter counts to 0x000 A reset occurs when the system is running .

1.2、IWDG Function description

stay Key register (IWDG_KR) writes 0xCCCC, Start using the independent watchdog ; At this point, the counter begins to reset from its value 0xFFF Decrement count . When the counter counts to the end 0x000 when , It will generate a reset signal (IWDG_RESET). No matter when , Just in the key register IWDG_KR writes 0xAAAA, IWDG_RLR The value in is reloaded into the counter , So as to avoid the reset of watchdog .

The watchdog function is in VDD Power supply area , That is, it can still work normally in shutdown and standby mode

1.3、 Register access protection

IWDG_PR and IWDG_RLR Register has write protection function . To modify the values of these two registers , You have to go to IWDG_KR Write in the register 0x5555. Writing to this register with different values will disrupt the order of operations , Registers will be protected again . Reload operation ( Write now 0xAAAA) It will also activate the write protection function .

The status register indicates whether the prescaled value and the decrement counter are being updated .

Prescaler register (IWDG_PR), This register is used to set the frequency division coefficient of the watchdog clock , The lowest is 4, highest 256, The register is a 32 Bit register , But we only used the lowest 3 position , Others are reserved bits .

Reload register . This register is used to save reload to count The value in the filter . This register is also a 32 Bit register , But only low 12 Bit is valid .

1.4、 To configure an independent watchdog

Just configure the three registers accordingly , We can start it STM32F1x The independent watchdog of .

The time in the figure below is according to 40kHz The clock gives . actually ,MCU Inside RC The frequency will be 30kHz To 60kHz Change between . Besides , Even if RC The frequency of the oscillator is accurate , The exact timing still depends on APB Interface clock and RC Phase difference between oscillator clocks , So there will always be a complete RC The period is uncertain .

Overflow time calculation :

Tout=((4×2^prer) ×rlr) /40 (M3)

step

1. Cancel register write protection :

IWDG_WriteAccessCmd();2. Set the prescaled coefficient of the independent watchdog , Determine clock :

IWDG_SetPrescaler();3. Set the watchdog reload value , Determine the overflow time :

IWDG_SetReload();4. To enable a watchdog

IWDG_Enable();5. The app feeds the dog :

IWDG_ReloadCounter();iwdg.c The procedure is as follows :

#include "wdg.h"

/* Initialize the independent watchdog

prer: Frequency division number :0~7( Only low 3 Bit effective !)

Division factor =4*2^prer. But the maximum can only be 256!

rlr: Reload register values : low 11 Bit effective .

Time calculation ( Probably ):Tout=((4*2^prer)*rlr)/40 (ms).*/

void IWDG_Init(u8 prer,u16 rlr)

{

IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable); // Enable on register IWDG_PR and IWDG_RLR Write operations for

IWDG_SetPrescaler(prer); // Set up IWDG Prescaled value : Set up IWDG The prescaled value is 64

IWDG_SetReload(rlr); // Set up IWDG Reload value

IWDG_ReloadCounter(); // according to IWDG Reload the value of the load register IWDG Counter

IWDG_Enable(); // Can make IWDG

}

// Hello, the independent watchdog

void IWDG_Feed(void)

{

IWDG_ReloadCounter();//reload

}

iwdg.h The procedure is as follows :

#ifndef __WDG_H

#define __WDG_H

#include "sys.h"

void IWDG_Init(u8 prer,u16 rlr);

void IWDG_Feed(void);

#endifmain.c The procedure is as follows :

#include "led.h"

#include "delay.h"

#include "key.h"

#include "sys.h"

#include "usart.h"

#include "wdg.h"

int main(void)

{

delay_init(); // Delay function initialization

LED_Init(); // Initialization and LED Connected hardware interface

KEY_Init(); // Key initialization

delay_ms(500); // Let people see

IWDG_Init(4,625); // And the frequency division number is 64, The overload value is 625, The overflow time is 1s

LED0=0; // Lighten up LED0

while(1)

{

if(KEY_Scan(0)==WKUP_PRES)

{

IWDG_Feed();// If WK_UP Press down , Then feed the dog

}

delay_ms(10);

};

}Two 、 Window watchdog

For the general watchdog , The program can refresh the watchdog at any time before it reset , But there is a hidden danger , It's possible that the program ran out of order and went back to the normal place , Or run disorderly program just executed refresh watchdog operation , In this case, the general watchdog can not detect it ;

If you use a window watchdog , The programmer can refresh a time window of the watchdog according to the normal execution time of the program , Make sure you don't refresh the watchdog ahead of time or behind , In this way, it can be detected that the program is not running in accordance with the normal path, and some program segments are skipped abnormally .

Window watchdog is usually used to monitor , Software failure caused by application deviating from normal operation sequence caused by external interference or unforeseen logic conditions . Unless the value of the down counter is in T6 A into 0(WWDG->CR No. 6 of ) Previously refreshed , When the watchdog circuit reaches the preset time cycle , Will produce a MCU Reset . The decrement counter reaches the window register (WWDG->CFR) Before the number , If 7 Bit down counter value ( In the control register ) Has been refreshed , Then there will also be a MCU Reset . This indicates that the down counter needs to be refreshed in a limited time window .

T[6:0] Namely WWDG_CR The lower seven of ,W[6:0] That is WWDG->CFR The lower seven of .T[6:0] It's the watchdog counter , and W[6:0] It's the upper window of the watchdog , The lower window value is fixed (0X40).

When the watchdog's counter is refreshed outside the upper window value , Or lower than the value of the lower window will cause a reset . Upper window value (W[6:0]) It's set by the user himself , Design window values according to actual requirements , But make sure that the window value is greater than 0X40, Otherwise the window doesn't exist .

2.1、WWDG The main features

Programmable free running decrement counter

Condition reset

─ When the value of the down counter is less than 0x40,( If the watchdog is activated ) Reset is generated .

─ When the decrement counter is reloaded outside the window ,( If the watchdog is activated ) Reset is generated .

If the watchdog is activated and interrupt is allowed , When the decrement counter equals 0x40 An early wake-up interrupt is generated (EWI), It can To be used to reload the counter to avoid WWDG Reset .

2.2、WWDG Function description

If the watchdog is activated (WWDG_CR In register WDGA The bit is set ’1’), And when the 7 position (T[6:0]) Decrement counter from 0x40 Flip to 0x3F(T6 A reset ) when , A reset is generated . If the counter value of the software is greater than the number in the window register Reload counter when value , A reset will be generated .

Applications must be written regularly during normal operation WWDG_CR Register to prevent MCU Reset occurs . Only when the counter value is less than the value of the window register , To write . Stored in the WWDG_CR The value in the register must be 0xFF and 0xC0 Between :

● Start the watchdog After the system is reset , The watchdog is always closed , Set up WWDG_CR The register of WDGA Bit can be turned on to see Door dog , Then it can no longer be closed , Unless reset occurs .

● Control the decrement counter. The decrement counter is in a free running state , Even if the watchdog is forbidden , The decrement counter continues to decrement the count . When the watchdog is enabled ,T6 Bit must be set , To prevent an immediate reset .

T[5:0] Bit contains the number of times before the watchdog reset ; The delay time before reset is at a minimum and a maximum Changes between large values , This is because writing WWDG_CR When the register , The prescaled value is unknown .

Configuration register (WWDG_CFR) Contains the upper limit of the window : To avoid reset , The decrement counter must be at its value Less than the value of the window register and greater than 0x3F Reloaded on , Describes the working process of the window register .

Another way to reload counters is to use early wake-up interrupts (EWI). Set up WWDG_CFR In register WEI Bit turns on the interrupt .

When the decrement counter reaches 0x40 when , This interrupt is generated , The corresponding interrupt service program (ISR) Can be used to load counters to prevent WWDG Reset . stay WWDG_SR Write... In the register ’0’ This interrupt can be cleared .

2.3、 Configuration steps of window watchdog

1. Upper window value W[6:0] Must be greater than the lower window value 0x40. Otherwise there will be no window .

2. Window watchdog clock source PCLK1(APB1 Bus clock ) After frequency division .

step

Enable the watchdog clock :

RCC_APB1PeriphClockCmd();Set the frequency division coefficient :

WWDG_SetPrescaler();Set the upper window value :

WWDG_SetWindowValue();Turn on the early wake-up interrupt and group ( Optional ):

WWDG_EnableIT();

NVIC_Init();To enable a watchdog :

WWDG_Enable();feed a dog :

WWDG_SetCounter();Write interrupt service function

WWDG_IRQHandler();wwdg.c The procedure is as follows :

#include "wdg.h"

#include "led.h"

// preservation WWDG Setting value of counter , Default to maximum .

u8 WWDG_CNT=0x7f;

/* Initialize the window watchdog

tr :T[6:0], Counter value

wr :W[6:0], Window value

fprer: Division coefficient (WDGTB), Only the lowest 2 Bit effective

Fwwdg=PCLK1/(4096*2^fprer). */

void WWDG_Init(u8 tr,u8 wr,u32 fprer)

{

RCC_APB1PeriphClockCmd(RCC_APB1Periph_WWDG, ENABLE); // WWDG Clock enable

WWDG_CNT=tr&WWDG_CNT; // initialization WWDG_CNT.

WWDG_SetPrescaler(fprer); Set up IWDG Prescaled value

WWDG_SetWindowValue(wr);// Set window values

WWDG_Enable(WWDG_CNT); // To enable a watchdog , Set up counter .

WWDG_ClearFlag();// Clear the early wake-up interrupt flag bit

WWDG_NVIC_Init();// Initialize the window watchdog NVIC

WWDG_EnableIT(); // Open window watchdog interrupt

}

// Heavy set WWDG The value of the counter

void WWDG_Set_Counter(u8 cnt)

{

WWDG_Enable(cnt);// To enable a watchdog , Set up counter .

}

// Window watchdog interrupt service program

void WWDG_NVIC_Init()

{

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_InitStructure.NVIC_IRQChannel = WWDG_IRQn; //WWDG interrupt

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 2; // preemption 2, Sub priority 3, Group 2

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 3; // preemption 2, Sub priority 3, Group 2

NVIC_InitStructure.NVIC_IRQChannelCmd=ENABLE;

NVIC_Init(&NVIC_InitStructure);//NVIC initialization

}

void WWDG_IRQHandler(void)

{

WWDG_SetCounter(WWDG_CNT); // When this sentence is forbidden , The window watchdog will generate a reset

WWDG_ClearFlag(); // Clear the early wake-up interrupt flag bit

LED1=!LED1; //LED State flip

}

wwdg.h The procedure is as follows :

#ifndef __WDG_H

#define __WDG_H

#include "sys.h"

void WWDG_Init(u8 tr,u8 wr,u32 fprer);// initialization WWDG

void WWDG_Set_Counter(u8 cnt); // Set up WWDG The counter of

void WWDG_NVIC_Init(void);

#endifmain.c The procedure is as follows :

#include "led.h"

#include "delay.h"

#include "key.h"

#include "sys.h"

#include "usart.h"

#include "wdg.h"

int main(void)

{

delay_init(); // Delay function initialization

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);// Set interrupt priority group to group 2:2 Bit preemption priority ,2 Bit response priority

LED_Init();

KEY_Init(); // Key initialization

LED0=0;

delay_ms(300);

WWDG_Init(0X7F,0X5F,WWDG_Prescaler_8);// The counter value is 7f, The window register is 5f, The frequency division number is 8

while(1)

{

LED0=1;

}

}

边栏推荐

- 学习记录:USART—串口通讯

- LeetCode#412. Fizz Buzz

- ucorelab3

- A method and implementation of using VSTO to prohibit excel cell editing

- UCORE lab7 synchronous mutual exclusion experiment report

- ucore lab 2

- What are the commonly used SQL statements in software testing?

- Threads et pools de threads

- JS --- detailed explanation of JS DOM (IV)

- What is "test paper test" in software testing requirements analysis

猜你喜欢

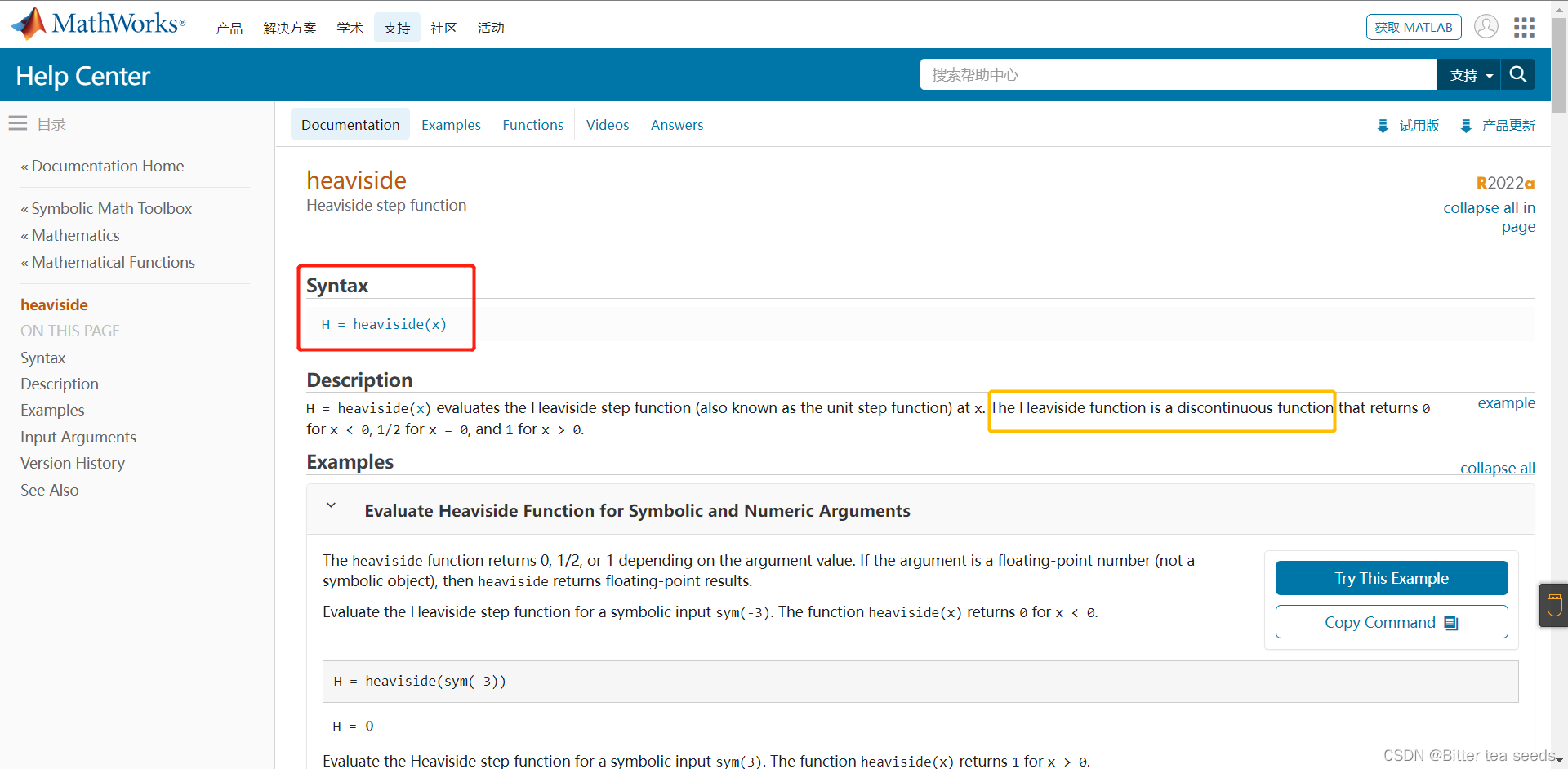

MATLAB实例:阶跃函数的两种表达方式

UCORE lab7 synchronous mutual exclusion experiment report

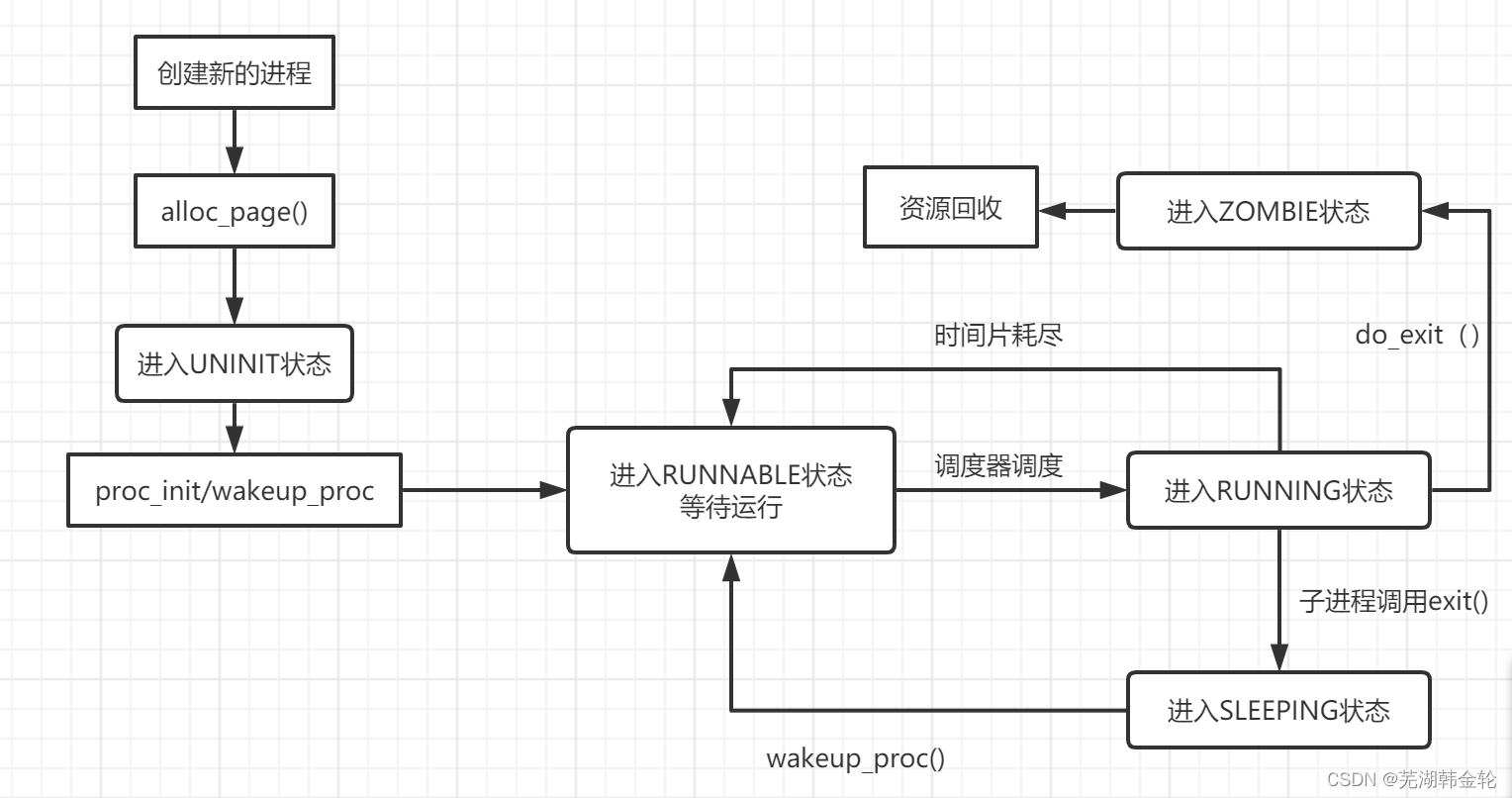

UCORE lab5 user process management experiment report

软件测试行业的未来趋势及规划

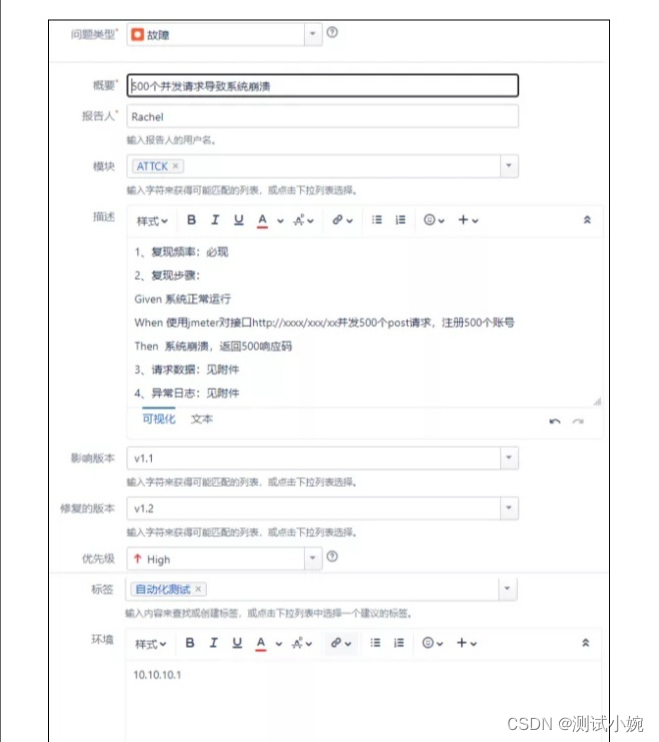

软件测试Bug报告怎么写?

LeetCode#62. Different paths

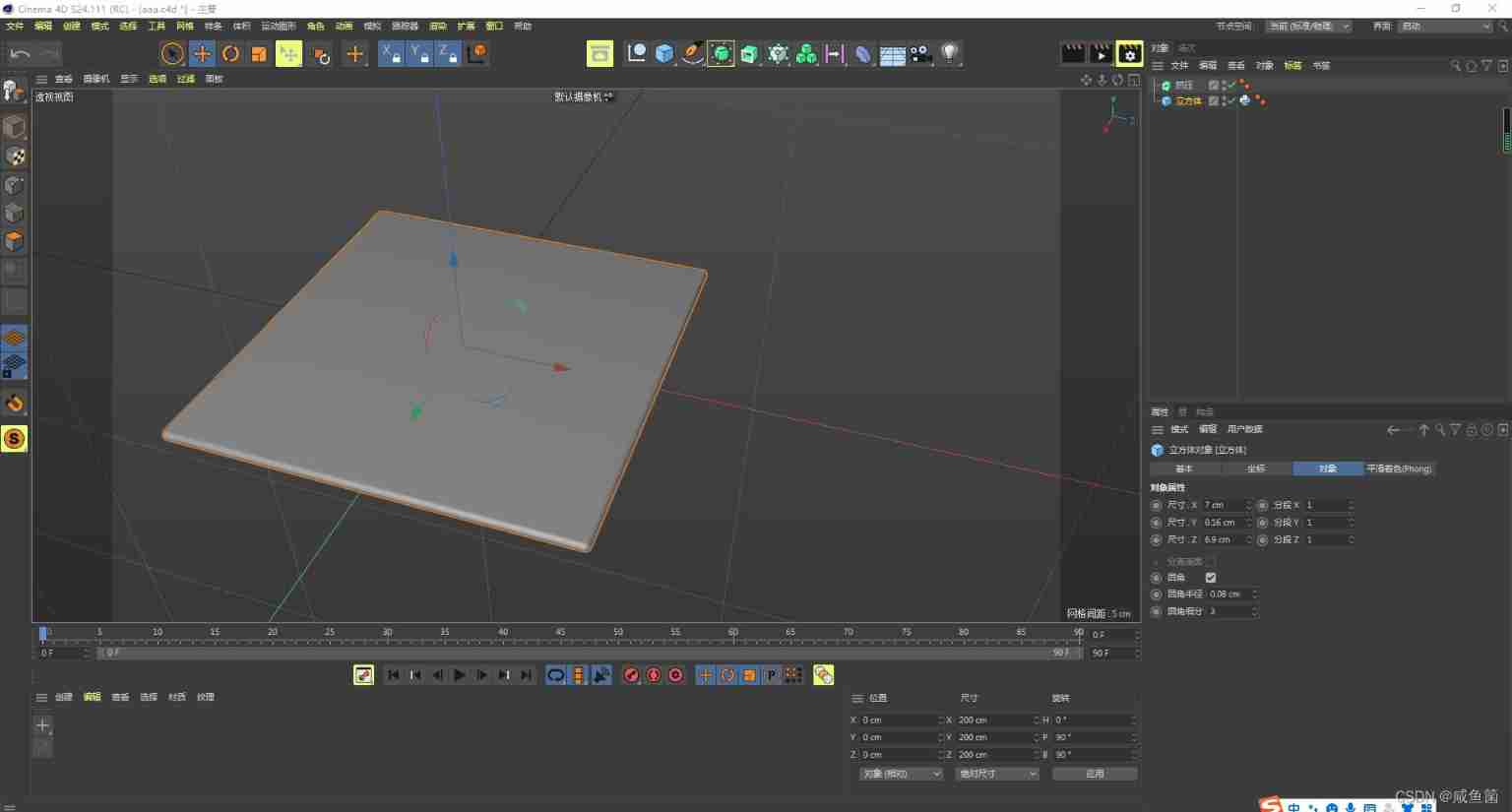

C4D quick start tutorial - Introduction to software interface

Do you know the advantages and disadvantages of several open source automated testing frameworks?

What is "test paper test" in software testing requirements analysis

ucorelab4

随机推荐

学习记录:STM32F103 时钟系统概述工作原理

JS --- detailed explanation of JS facing objects (VI)

JS --- all knowledge of JS objects and built-in objects (III)

UCORE lab2 physical memory management experiment report

Currently, mysql5.6 is used. Which version would you like to upgrade to?

ArrayList set

Preface to the foundations of Hilbert geometry

Crawler series (9): item+pipeline data storage

转行软件测试必需要知道的知识

Research Report on market supply and demand and strategy of Chinese hospital cleaning chemicals industry

Sorting odd and even subscripts respectively for leetcode simple problem

Interface test interview questions and reference answers, easy to grasp the interviewer

Do you know the advantages and disadvantages of several open source automated testing frameworks?

What to do when programmers don't modify bugs? I teach you

How to write the bug report of software test?

学习记录:如何进行PWM 输出

Lab 8 文件系统

全网最详细的postman接口测试教程,一篇文章满足你

MATLAB实例:阶跃函数的两种表达方式

The latest query tracks the express logistics and analyzes the method of delivery timeliness