当前位置:网站首页>“人生若只如初见”——RISC-V

“人生若只如初见”——RISC-V

2022-07-06 09:24:00 【Lntan0】

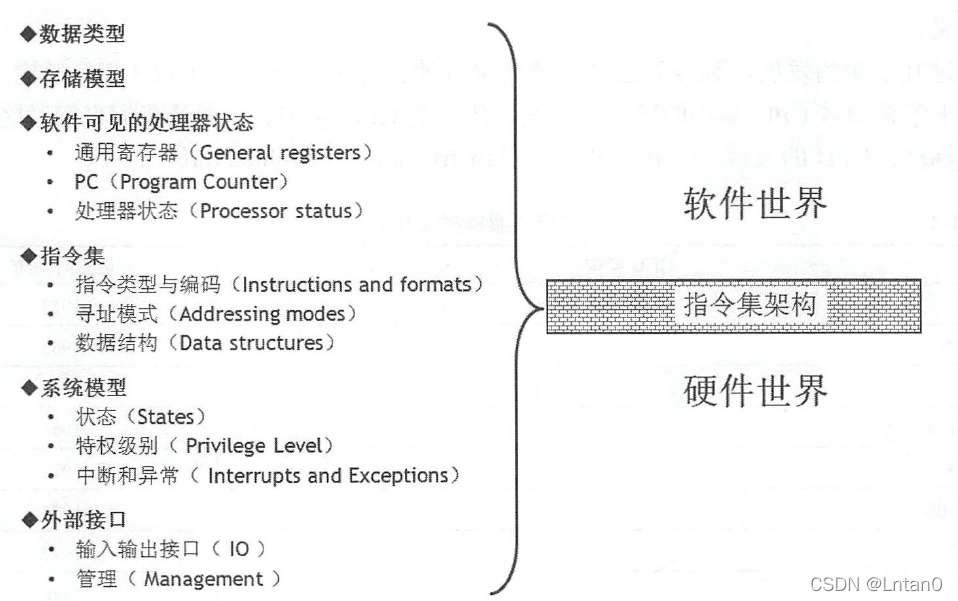

提起RISC-V,我们不得不提的一个词便是指令集架构(ISA)。

那么,何谓“ISA”,ISA可以称得上是CPU的灵魂,有时简称为“架构”或者称为“处理器架构”。

上图对ISA做了一个详细的描述,这里便不再赘述。

有了指令集架构,便可以使用不同的处理器硬件实现方案来设计不同性能的处理器。处理器的具体硬件实现方案称为微架构(Microarchitecture)。

RISC-V(英文读作“risk-five”),是一种全新的指令集架构。RISC-V架构主要由美国加州大学伯克利分校的几名教授于2010年发明。伯克利的开发人员之所以发明一套新的指令集架构,而不是使用成熟的X86或者arm架构,是因为这些架构经过多年的发展,变得极为复杂和冗杂,并且存在高昂的专利和架构授权问题。因此,RISC-V架构是一种全新的,简单且开放免费的指令集架构。

简单介绍一些CPU原理:

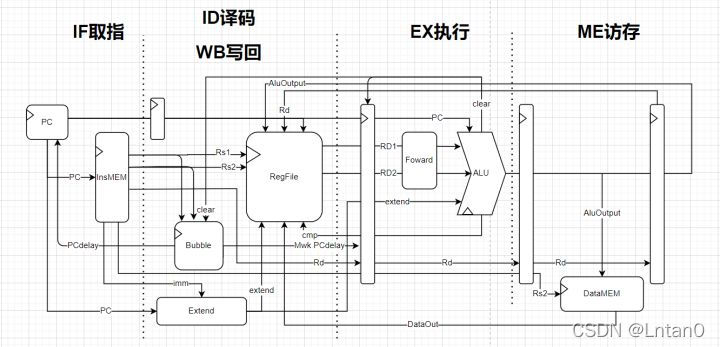

1.经典的五级流水线

一条指令的流程:取指>译码>执行>访存>写回

简单提及一个概念:流水线深度

越来越深的流水线:追求高性能

越来越浅的流水线:追求低功耗

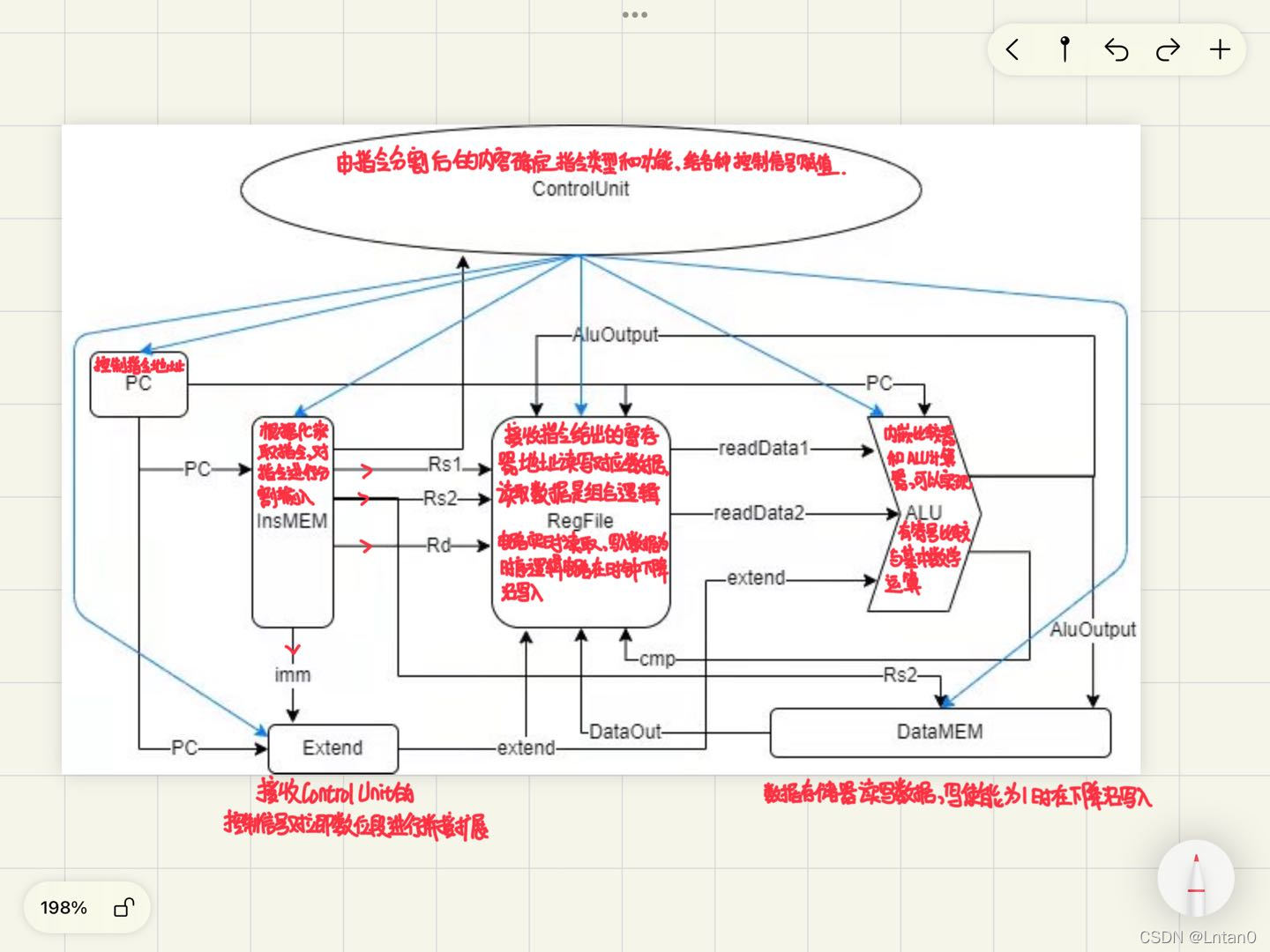

2.CPU数据通路

关于比赛

赛题:基于蜂鸟E203 RISC-V内核的智能识别SoC设计与应用系统开发

内容:基于芯来科技的开源蜂鸟E203 Demo SoC(e203_hbirdv2)进行扩展, 在限定的可编程逻辑平台上构建面向智能识别应用领域的SoC,进而完成实际的应用系统开发。要求在所搭建的SoC中实现专门的硬件加速器以提高系统整体性能,所实现的应用系统具有创新性、实用性以及市场应用前景。

吐槽一下:借不到&买不起板子也太劝退了

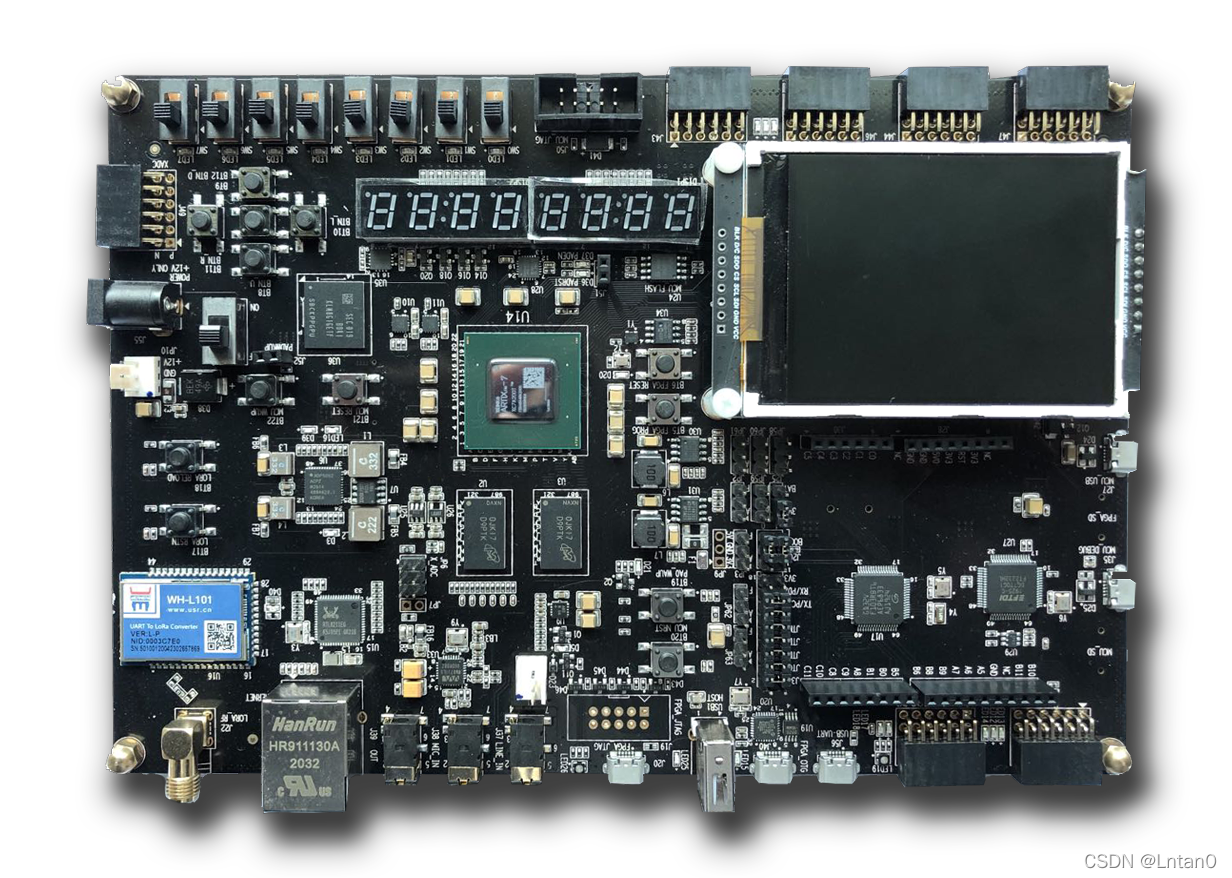

(Nuclei MCU200T,售价2499)

(Nuclei DDR200T,售价4999)

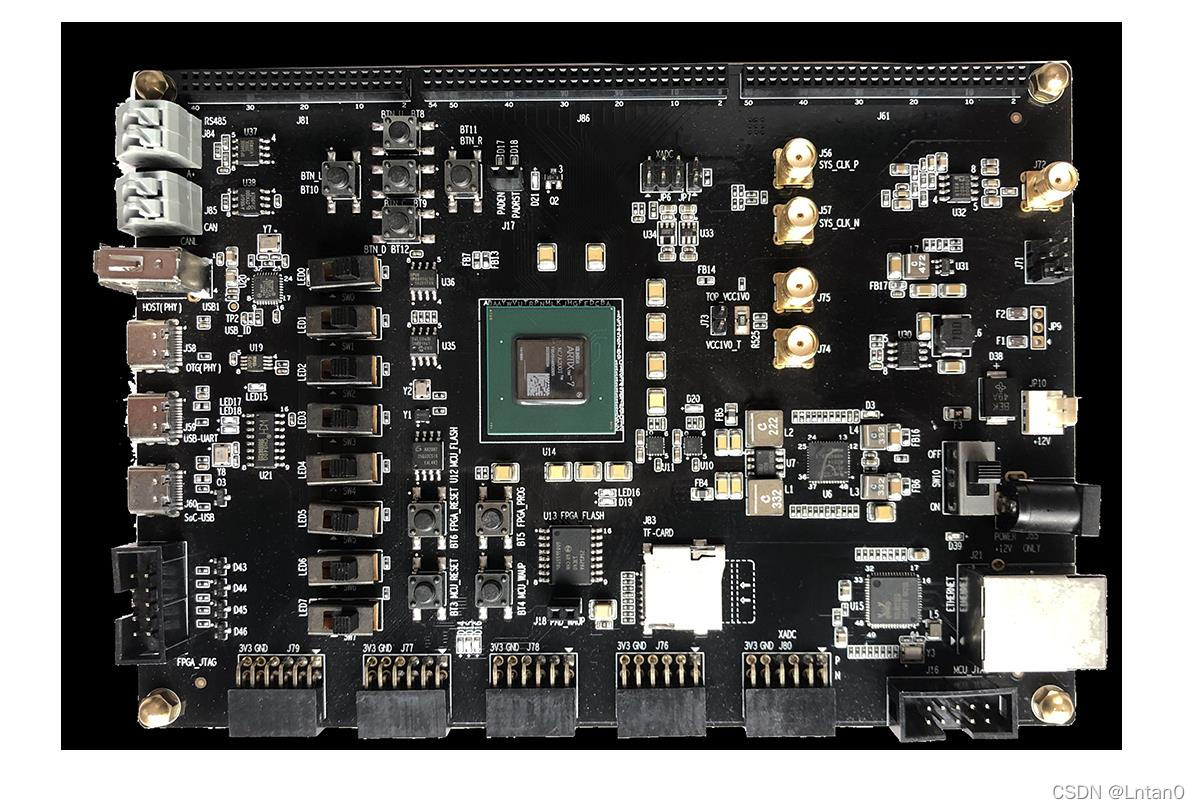

最后在实验室王学长的支持下,买到了一款开发板

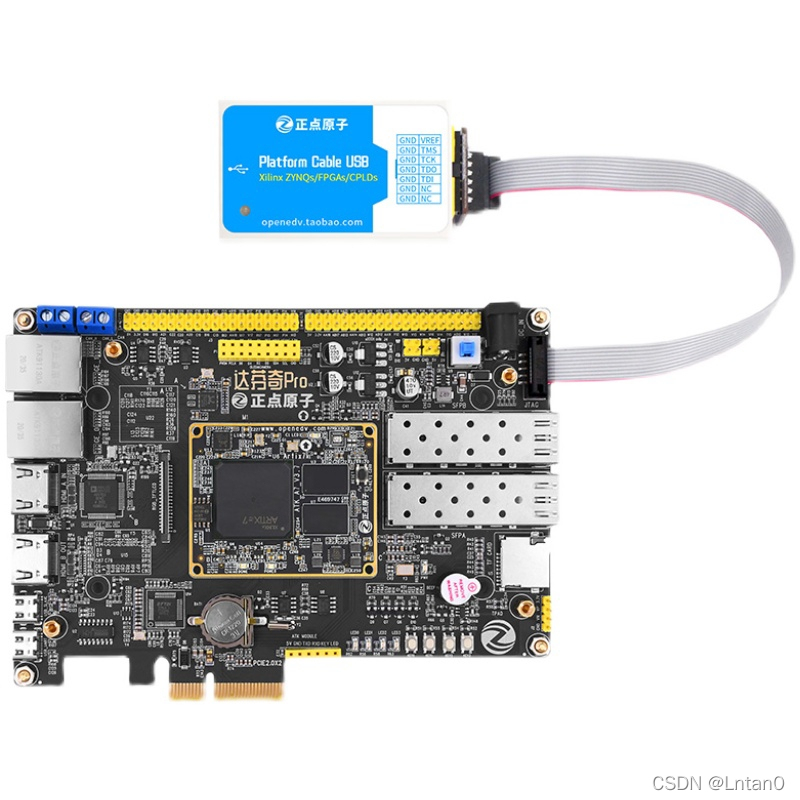

(达芬奇pro 35T,售价1526)

熟悉板子,最头疼的还是将E203 soc内核移植到板子里(网上教程几乎为0)

移植教程会在后续发出

分享只为学习交流,还望大佬们不吝赐教🥰

边栏推荐

- Network technology related topics

- C language file operation

- Applet Web Capture -fiddler

- 关于超星脚本出现乱码问题

- Statistics 8th Edition Jia Junping Chapter 14 summary of index knowledge points and answers to exercises after class

- "Gold, silver and four" job hopping needs to be cautious. Can an article solve the interview?

- msf生成payload大全

- 攻防世界MISC练习区(SimpleRAR、base64stego、功夫再高也怕菜刀)

- . Net6: develop modern 3D industrial software based on WPF (2)

- captcha-killer验证码识别插件

猜你喜欢

servlet中 servlet context与 session与 request三个对象的常用方法和存放数据的作用域。

Hackmyvm target series (3) -visions

Solutions to common problems in database development such as MySQL

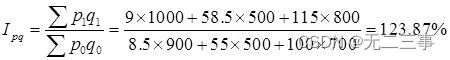

《统计学》第八版贾俊平第十四章指数知识点总结及课后习题答案

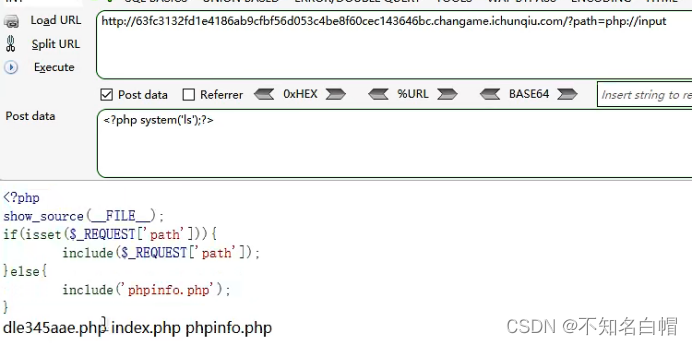

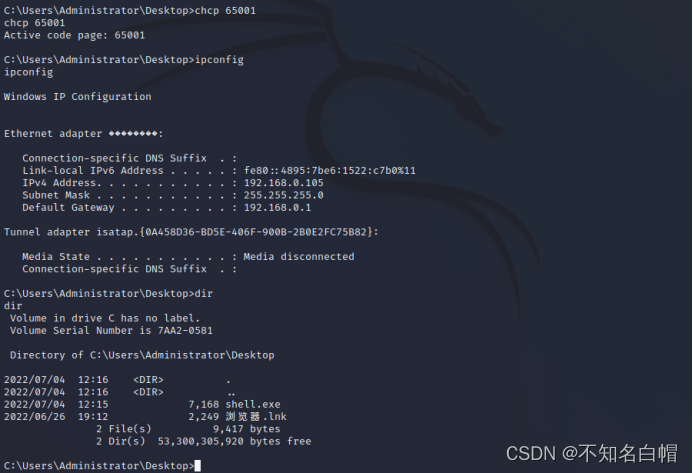

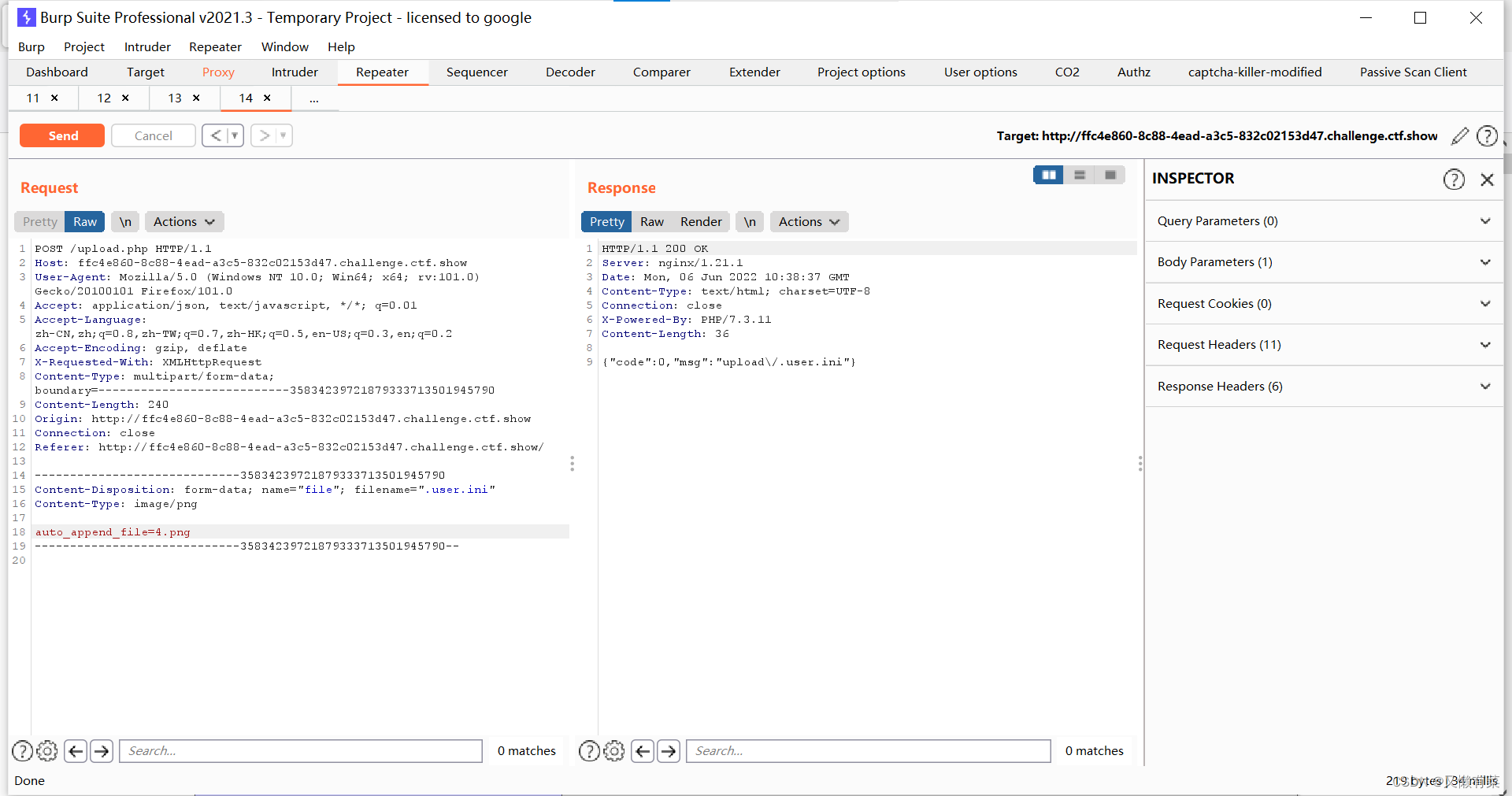

WEB漏洞-文件操作之文件包含漏洞

内网渗透之内网信息收集(一)

Markdown font color editing teaching

中间件漏洞复现—apache

Intranet information collection of Intranet penetration (2)

网络基础之路由详解

随机推荐

2022华中杯数学建模思路

Intel oneapi - opening a new era of heterogeneity

Intranet information collection of Intranet penetration (2)

浙大版《C语言程序设计实验与习题指导(第3版)》题目集

网络基础详解

An unhandled exception occurred when C connected to SQL Server: system Argumentexception: "keyword not supported:" integrated

How to test whether an object is a proxy- How to test if an object is a Proxy?

7-14 error ticket (PTA program design)

Experiment 7 use of common classes (correction post)

[paper reproduction] cyclegan (based on pytorch framework) {unfinished}

《统计学》第八版贾俊平第二章课后习题及答案总结

MySQL interview questions (4)

Interpretation of iterator related "itertools" module usage

MSF generate payload Encyclopedia

JDBC事务、批处理以及连接池(超详细)

Attack and defense world misc practice area (simplerar, base64stego, no matter how high your Kung Fu is, you are afraid of kitchen knives)

This article explains in detail how mockmvc is used in practical work

《英特尔 oneAPI—打开异构新纪元》

How does SQLite count the data that meets another condition under the data that has been classified once

Realize applet payment function with applet cloud development (including source code)