当前位置:网站首页>【ESP32学习-2】esp32地址映射

【ESP32学习-2】esp32地址映射

2022-07-06 09:16:00 【csdndulala】

本文始于esp32技术参考手册中的一段描述

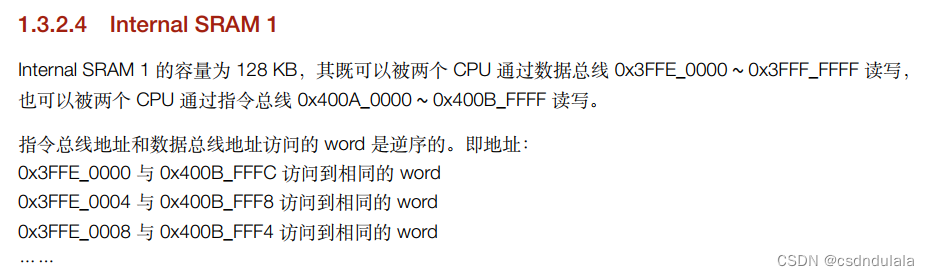

1.3.2.4 Internal SRAM 1

Internal SRAM 1 的容量为 128 KB,其既可以被两个 CPU 通过数据总线 0x3FFE_0000 ~ 0x3FFF_FFFF 读写,

也可以被两个 CPU 通过指令总线 0x400A_0000 ~ 0x400B_FFFF 读写。

指令总线地址和数据总线地址访问的 word 是逆序的。即地址:

0x3FFE_0000 与 0x400B_FFFC 访问到相同的 word

0x3FFE_0004 与 0x400B_FFF8 访问到相同的 word

0x3FFE_0008 与 0x400B_FFF4 访问到相同的 word迷惑的是为什么inter SRAM 1 通过数据和指令总线访问不同地址,得到的是相同的内容?为什么这样设计?有什么好处?

遍寻资料,终于找到了准确的解答:可以定制化调整IRAM和DRAM的大小。(同时也解答了,esp32内部ram是怎么划分使用的)ROM0为何需要Remap:

1.3.2.1 Internal ROM 0

Internal ROM 0 的容量为 384 KB,可以被两个 CPU 通过指令总线 0x4000_0000 ~ 0x4005_FFFF 读取。

访问 ROM 0 的头 32 KB 的地址(0x4000_0000 ~ 0x4000_7FFF)可以被重新映射 到 Internal SRAM 1 中的一部

分,这部分原本被地址 0x400B_0000 ~ 0x400B_7FFF 访问。重映射时,这 32 KB SRAM 不能再被地址

0x400B_0000 ~ 0x400B_7FFF 访问,但是可以被数据总线 (0x3FFE_8000 ~ 0x3FFE_FFFF)访问。实现方式是

分别为两个 CPU 配置一个寄存器,即为 PRO_CPU 置位 DPORT_PRO_BOOT_REMAP_CTRL_REG 寄存器的

bit 0 或者为 APP_CPU 置位 DPORT_APP_BOOT_REMAP_CTRL_REG 寄存器的 bit 0。网上没有找到解释,我的理解:

rom0作为指令空间一共有384KB(已经非常大了),所分配的地址空间不会全部使用,可以通过remap的方式,将rom的地址映射为ram的地址。这样可以加快一级引导程序的运行。

边栏推荐

- Password free login of distributed nodes

- 2020 WANGDING cup_ Rosefinch formation_ Web_ nmap

- Wangeditor rich text reference and table usage

- 2020网鼎杯_朱雀组_Web_nmap

- Detailed explanation of express framework

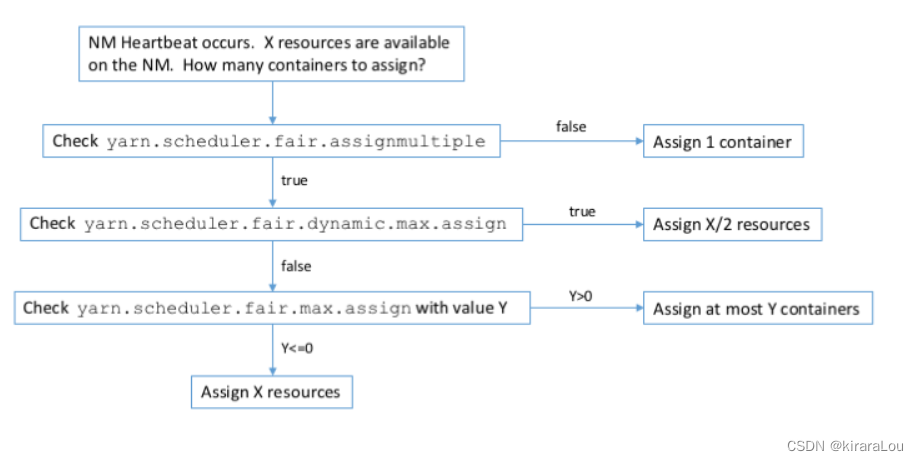

- [yarn] CDP cluster yarn configuration capacity scheduler batch allocation

- Detailed explanation of Union [C language]

- Priority inversion and deadlock

- Oppo vooc fast charging circuit and protocol

- 【flink】flink学习

猜你喜欢

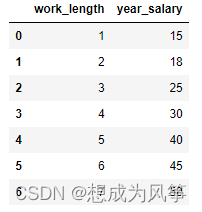

电商数据分析--薪资预测(线性回归)

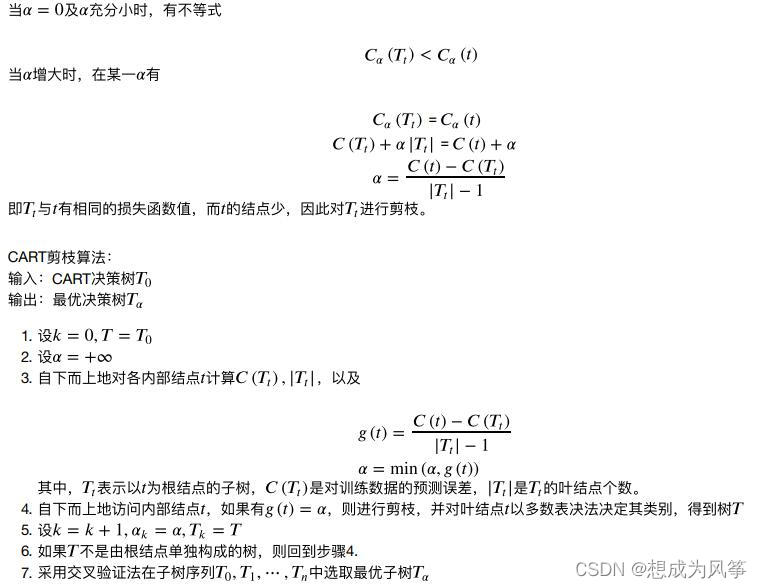

Machine learning -- decision tree (sklearn)

【CDH】CDH5.16 配置 yarn 任务集中分配设置不生效问题

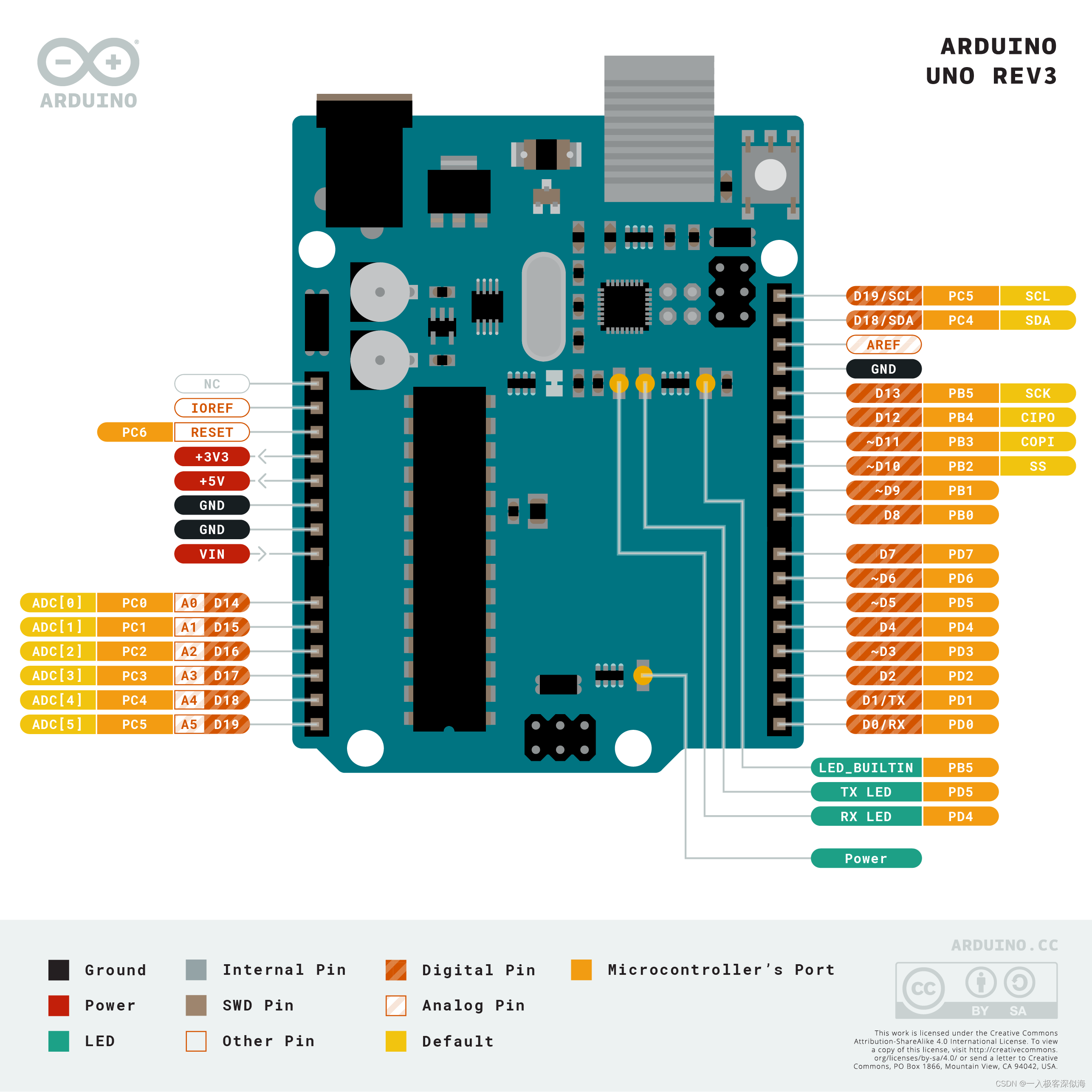

arduino UNO R3的寄存器写法(1)-----引脚电平状态变化

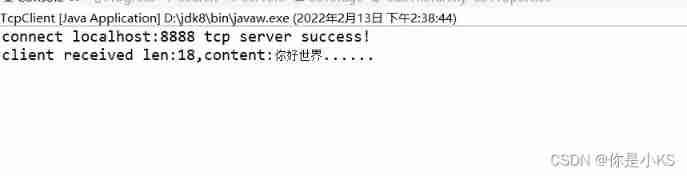

Vert. x: A simple TCP client and server demo

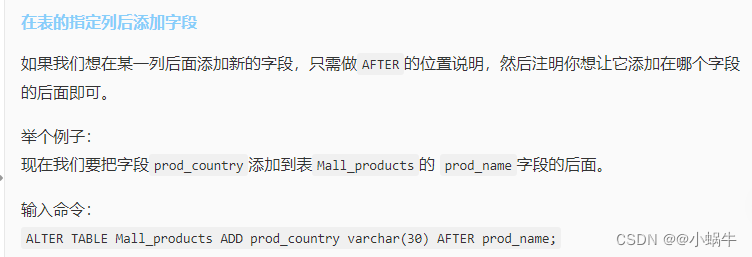

Stage 4 MySQL database

![[yarn] CDP cluster yarn configuration capacity scheduler batch allocation](/img/85/0121478f8fc427d1200c5f060d5255.png)

[yarn] CDP cluster yarn configuration capacity scheduler batch allocation

Apprentissage automatique - - régression linéaire (sklearn)

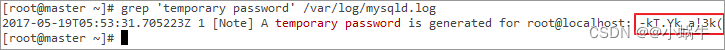

Linux yum安装MySQL

MySQL realizes read-write separation

随机推荐

Togglebutton realizes the effect of switching lights

XML文件详解:XML是什么、XML配置文件、XML数据文件、XML文件解析教程

Priority inversion and deadlock

RT-Thread的main线程“卡死”的一种可能原因及解决方案

Unit test - unittest framework

機器學習--線性回歸(sklearn)

Reno7 60W super flash charging architecture

Dead loop in FreeRTOS task function

4. Install and deploy spark (spark on Yan mode)

arduino JSON数据信息解析

Detailed explanation of nodejs

Kaggle竞赛-Two Sigma Connect: Rental Listing Inquiries(XGBoost)

OSPF message details - LSA overview

Funny cartoon: Programmer's logic

[CDH] cdh5.16 configuring the setting of yarn task centralized allocation does not take effect

R & D thinking 01 ----- classic of embedded intelligent product development process

2020网鼎杯_朱雀组_Web_nmap

[yarn] CDP cluster yarn configuration capacity scheduler batch allocation

Reno7 60W超级闪充充电架构

[yarn] yarn container log cleaning