当前位置:网站首页>[ram IP] introduction and experiment of ram IP core

[ram IP] introduction and experiment of ram IP core

2022-07-06 05:59:00 【Linest-5】

RAM brief introduction :

RAM(Random Access Memory), Random access memory . It is dual port , It can write data to any storage unit at any specified address at any time , You can also read data from any designated address at any time , Its reading and writing speed is determined by the clock frequency .RAM It is mainly used to store programs and intermediate data generated during program execution 、 Operation results, etc .

a slice RAM It is divided into many small cells , Each piece has a capacity of 36k, This area is determined according to the set bit width RAM It can be stored in several compartments , Bit width one ah cannot be set to 1、2、4、8、16、32 etc. , Every two adjacent pieces RAM Can be synthesized into one piece RAM, This piece of RAM It's also dual port , You can read and write independently , And the bit width can be configured in both reading and writing .

- Single port : There's only one port , Reading and writing data cannot be done at the same time , Shared data channel .

- Pseudo dual port : Has two data channels , One for writing and one for reading .

- True dual port : Has two data channels , Both channels can be used to read or write .

Building engineering :

1、 open vivado, choice add sources->add or creat a new sources The name is ip_ram->finish that will do .

2、 add to ram ip,ip catalog-> Search for ram choice block memory generate(bram), Double click to open the configuration interface , The configuration is as follows , Configured as a single port 、 The write bit width and read bit width are 8, Write depth and read depth will be automatically configured ,operating mode It can be set to write frist It's fine too no change, The effect of this setting item is the priority when reading and writing data .

3、 Adding a file , Used to describe the process of reading and writing , The file name is ram_rw, The code is as follows :

module ram_rw(

input clk,

input rst,

output reg ram_en,

output reg rw,

output reg [4:0] ram_addr,

output reg [7:0] ram_wr_data

);

reg [5:0] rw_cnt;

[email protected](posedge clk or negedge rst)begin

if(rst)

ram_en<=1'b0;

else

ram_en<=1'b1;

end

//rw_cnt

always @(posedge clk or posedge rst) begin

if (rst) begin

rw_cnt <= 6'd0;

end

else if (rw_cnt == 6'd63) begin

rw_cnt <= 6'd0;

end

else begin

rw_cnt <= rw_cnt + 6'd1;

end

end

//ram_wr_data

always @(posedge clk or posedge rst) begin

if (rst) begin

ram_wr_data <= 8'd0;

end

else if ((rw_cnt <= 6'd31) && ram_en == 1'b1) begin

ram_wr_data <= ram_wr_data + 8'd1;

end

else begin

ram_wr_data <= ram_wr_data;

end

end

//rw

always @(posedge clk or posedge rst) begin

if (rst) begin

rw <= 1'b1;

end

else if (rw_cnt <= 6'd31) begin

rw <= 1'b1;

end

else begin

rw <= 1'b0;

end

end

//ram_addr

always @(posedge clk or posedge rst) begin

if (rst) begin

ram_addr <= 5'd0;

end

else begin

ram_addr <= rw_cnt[4:0];

end

end

endmodule4、 edit ip_ram Code :

according to ip sources Medium ip Options instantiation template( Instantiation template ), choice veo file , Copy its instantiated template and paste it into ip_ram in , And manually instantiate ram_rw Code block in , And define the system clock and reset .

5、 add to ILA IP

add to ila ip Used to detect signals , The same operation is in ip catalog Mid search ila Double click to open the configuration interface , Because we need to detect five signals :ram Enable signal 、 Read / write operation signal 、ram Address signal 、ram Read and write data signals 、 The last output signal douta. therefore number of probes The number of probes is 5, Configure the corresponding data bit width in the bit width of each probe . The same in ip sources Medium veo A copy of a document ila An example template for , Paste to the top-level module ip_ram In the code of , The final code is as follows :

module ip_ram(

input sys_clk,

input sys_rst

);

wire ram_en;

wire rw;

wire [4:0] ram_addr;

wire [7:0] ram_wr_data;

wire [7:0] douta;

ram_rw ram_rw_u(

.clk (sys_clk),

.rst (sys_rst),

.ram_en (ram_en),

.rw (rw),

.ram_addr (ram_addr),

.ram_wr_data(ram_wr_data)

);

blk_mem_gen_0 blk_mem_gen_0_u (

.clka(sys_clk), // input wire clka

.ena(ram_en), // input wire ena

.wea(rw), // input wire [0 : 0] wea

.addra(ram_addr), // input wire [4 : 0] addra

.dina(ram_wr_data), // input wire [7 : 0] dina

.douta(douta) // output wire [7 : 0] douta

);

ila_0 your_instance_name (

.clk(sys_clk), // input wire clk

.probe0(ram_en), // input wire [0:0] probe0

.probe1(rw), // input wire [0:0] probe1

.probe2(ram_addr), // input wire [4:0] probe2

.probe3(ram_wr_data), // input wire [7:0] probe3

.probe4(douta) // input wire [7:0] probe4

);

endmodule

6、 Comprehensive document :

Click on run synthesis To synthesize , Click open synthesis design Check the corresponding frame diagram as follows :

7、 Bind pins and generate bitstream

This experiment only uses PL End resources , Therefore, the pins need to be bound , Only two pins need to be bound : Clock and reset , stay Layout Choose from i/o planing The pins can be configured , stay zedboard The schematic diagram can be consulted GCLK It can be seen that the pin of the clock is Y9, and PL The reset button on the end is integrated in BTNL in , Therefore, the pin is N15, The voltage of both pins is lvcmos3.3v,ctrl+s Save and name the constraint file ip_ram You can automatically generate constraint files . Last generate bitstream that will do .

8、 Connecting boards :

Connect the development board and power on , Click on open target->auto connect->program device Click start again to see the pass ila Detected signal , You can verify whether the design is correct by looking at the sequence diagram .

边栏推荐

- Yygh-11-timing statistics

- IDEA 新UI使用

- Station B Liu Erden - linear regression and gradient descent

- Request forwarding and redirection

- Arrays and collections

- 授予渔,从0开始搭建一个自己想要的网页

- Auto. JS learning notes 17: basic listening events and UI simple click event operations

- [email protected]树莓派

- [C language syntax] the difference between typedef struct and struct

- Clear floating mode

猜你喜欢

![[experience] install Visio on win11](/img/f5/42bd597340d0aed9bfd13620bb0885.png)

[experience] install Visio on win11

[SQL Server Express Way] - authentification et création et gestion de comptes utilisateurs

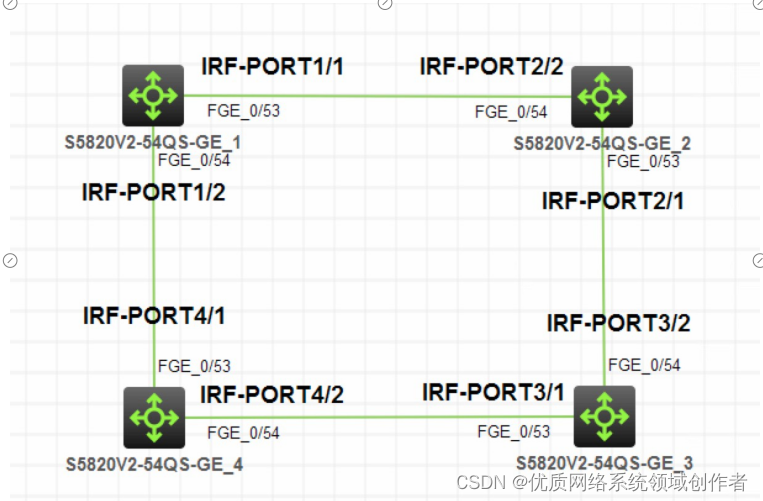

H3C V7版本交换机配置IRF

What preparations should be made for website server migration?

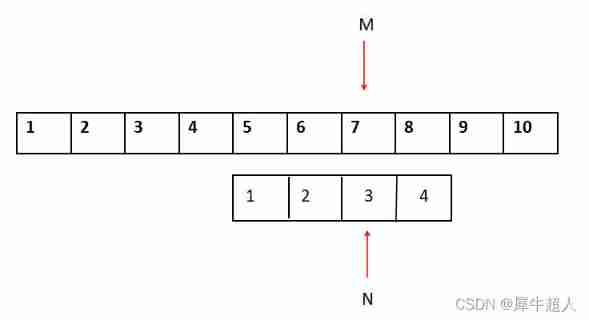

Detailed explanation of BF and KMP

![[Jiudu OJ 07] folding basket](/img/a7/e394f32cf7f02468988addad67674b.jpg)

[Jiudu OJ 07] folding basket

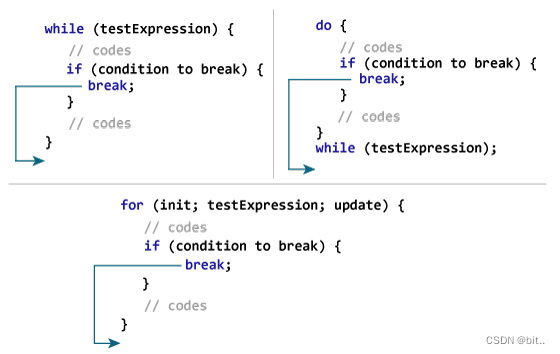

continue和break的区别与用法

Embedded interview questions (IV. common algorithms)

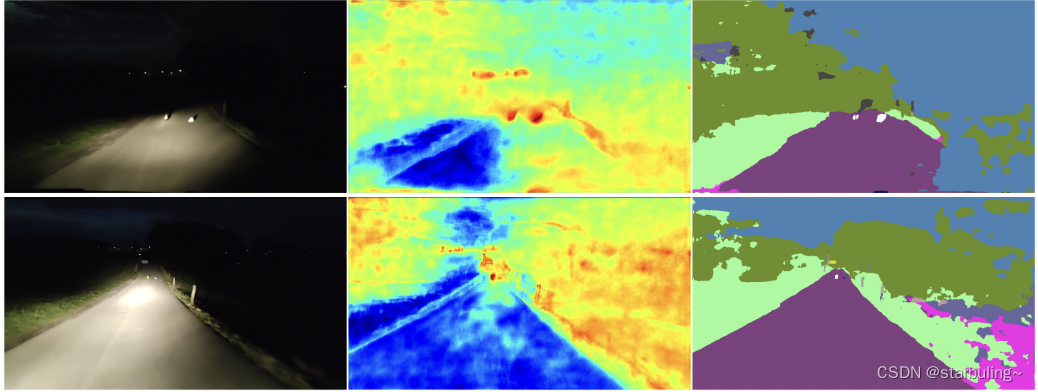

【论文阅读】NFlowJS:基于鲁棒学习的合成负数据密集异常检测

About PHP startup, mongodb cannot find the specified module

随机推荐

nodejs实现微博第三方登录

C language bubble sort

OSPF configuration command of Huawei equipment

Rustdesk builds its own remote desktop relay server

关于 PHP 启动 MongoDb 找不到指定模块问题

How to recover Huawei router's forgotten password

AUTOSAR from getting started to becoming proficient (10) - embedded S19 file analysis

Database: ODBC remote access SQL Server2008 in oracel

Is it difficult for an information system project manager?

H3C firewall rbm+vrrp networking configuration

【无标题】

Network protocol model

养了只小猫咪

华为BFD的配置规范

Leetcode 701 insertion operation in binary search tree -- recursive method and iterative method

LAN communication process in the same network segment

Pytorch代码注意的细节,容易敲错的地方

Migrate Infones to stm32

Cognitive introspection

H3C S5820V2_ Upgrade method after stacking IRF2 of 5830v2 switch

![[SQL Server Express Way] - authentification et création et gestion de comptes utilisateurs](/img/42/c1def031ec126a793195ebc881081e)