当前位置:网站首页>Always of SystemVerilog usage_ comb 、always_ iff

Always of SystemVerilog usage_ comb 、always_ iff

2022-07-06 14:21:00 【Then the dish】

always_comb

always_comb Each internal statement is a blocking assignment statement . Circuit statements... Cannot appear (assign)

always_comb It has the following properties :

Internal coverage

External atomicity

always_comb begin

a = 1'b1;

b = a;

a =1'b0;

c = a;

end

// Circuit input :1'b1;1'b0; // On the right (1'b1;1'b0; a) Remove the left side (a,b,c)

// Circuit output :(a,b,c)// On the left

// Running results a=1'b0, b=1'b1, c=1'b0,

assign a = b;

always_comb begin

b = 1'b1;

c = a;

b = 1'b0;

end

// First always_comb have to : c = a, b = 1'b0; Again assign have to :a = b = 1'b0; c = a = 1'b0

// therefore a=1'b0, b=1'b0, c=1'b0,

assign a = b;

always_comb begin

b = 1'b1;

c = b;

b = 1'b0;

end

// First always_comb have to : c = b = 1'b1; b = 1'b0 Again assign have to :a = b = 1'b0;

// therefore a=1'b0, b=1'b0, c=1'b1,

always_comb case

unique case

case There is no priority in the block , Parallel comparison .

// unique case

always_comb begin

b = 1'b0;

unique case (a[3:0])

4'd1: begin b = 1'b1; end

4'd0: begin b = 1'b0; end

default: begin end

endcase

end

priority case

case There is priority in the block , Serial comparison ( Compare in turn )

always_comb begin

priority case (1'b1)

a[3]: begin end

a[2]: begin end

default: begin end

endcase

end

// amount to :

/*

always_comb begin

if(a[3]) begin

end else if(a[2]) begin

end else if() begin end

end

*/

always_comb if and for

if

if and else Used for conditional judgment

always_comb begin

b = 1'b0;

if (a[3]) begin b = 1'b1; end

else if (a[2]) begin b = 1'b0; end

else begin end

end

for

for stay always_comb in , Will be interpreted as loop expansion .

logic [15:0]a;

logic [3:0] b;

always_comb begin

b = '0;

for (int i = 15; i >= 0; i--) begin

if (a[i]) begin

b = i[3:0];

break;

end

end

end

always_comb begin

for (int i = 0 ; i < 16; i ++) begin

if (i >= n) break;

end

end

always_comb begin

for (int i = 0; i < 16; i++) begin

a[i] = b[i] & (c[i] == d[i] | e[i]); // The compiler doesn't think i Is constant ,a[i:i+3] illegal

end

end

for (genvar i = 0; i < 16; i++) begin // genvar assign

assign a[i] = b[i] & (c[i] == d[i] | e[i]); // The compiler thinks i Is constant ,a[i:i+3] legal

always_comb begin

end

end

always_ff

always_ff Used to describe triggers .

always_ff @(posedge clk) begin

if (~resetn) begin

q <= '0; // Trigger non blocking assignment

end else if (en) begin

q <= d;

end

end

logic [3:0] a, a_nxt;

// always_ff Write only the trigger part Nonblocking assignment

always_ff @(posedge clk) begin

if (~resetn) begin

a <= '0;

end else if (en) begin

{a, b} <= {a_nxt, b_nxt};

end

end

always_comb begin

a_nxt = a;

// Logic that does not belong to a trigger , Written in always_comb Block assignment

unique case(a)

4'd3: begin

a_nxt = 4'd2;

end

default: begin

end

endcase

end

Thank you for sharing !!

(4 Bar message ) System Verilog grammar _ Record on pit -CSDN Blog

边栏推荐

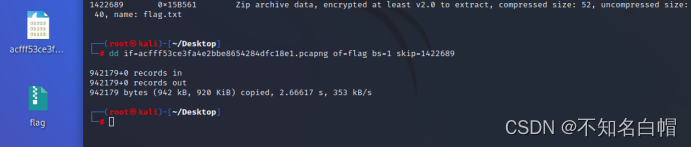

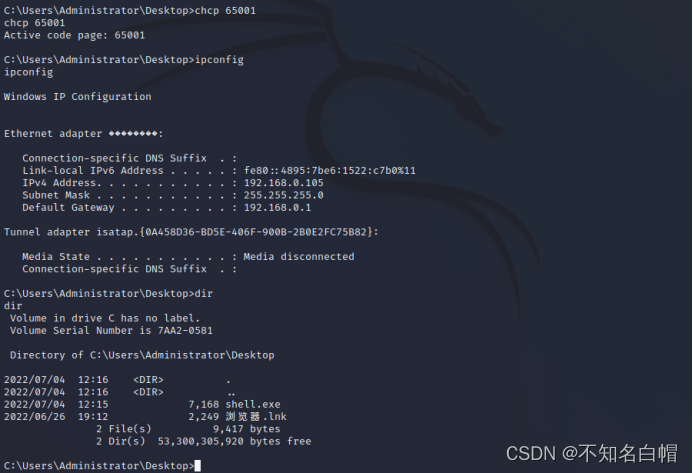

- Record a penetration of the cat shed from outside to inside. Library operation extraction flag

- Hackmyvm target series (6) -videoclub

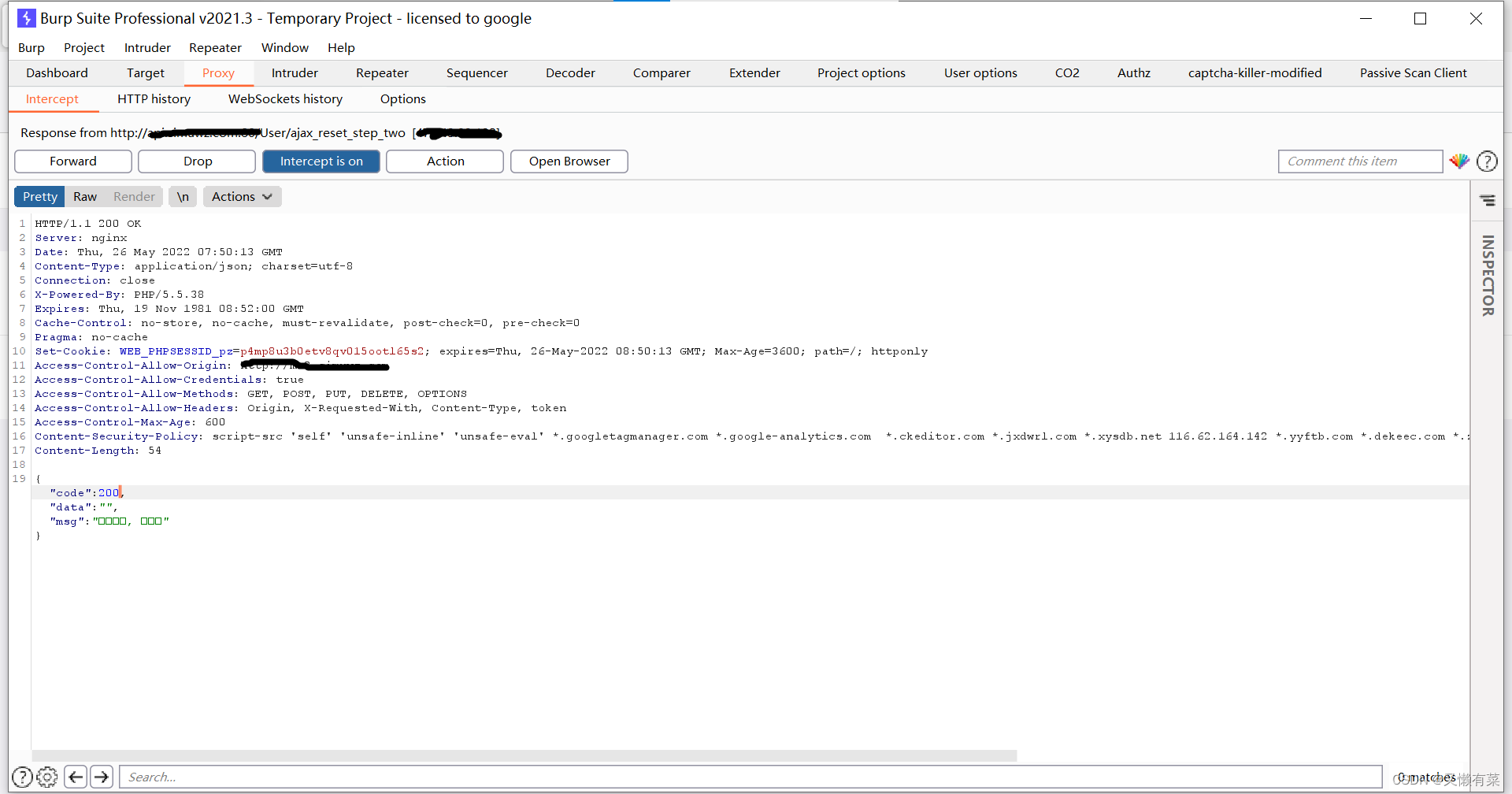

- Record once, modify password logic vulnerability actual combat

- 实验七 常用类的使用

- Chain team implementation (C language)

- 浅谈漏洞发现思路

- xray與burp聯動 挖掘

- Experiment 7 use of common classes

- 循环队列(C语言)

- Package bedding of components

猜你喜欢

攻防世界MISC练习区(SimpleRAR、base64stego、功夫再高也怕菜刀)

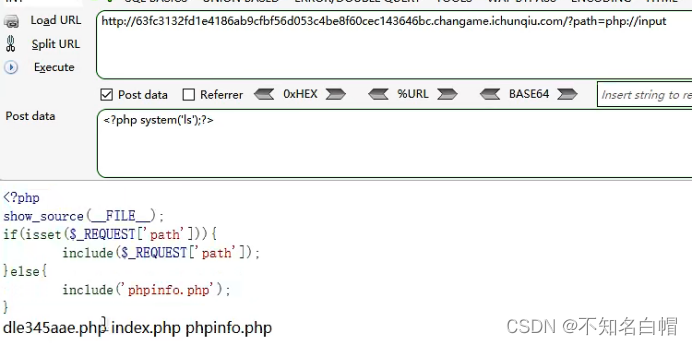

WEB漏洞-文件操作之文件包含漏洞

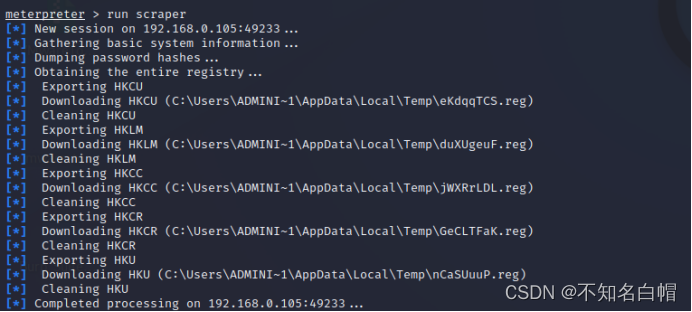

Intranet information collection of Intranet penetration (4)

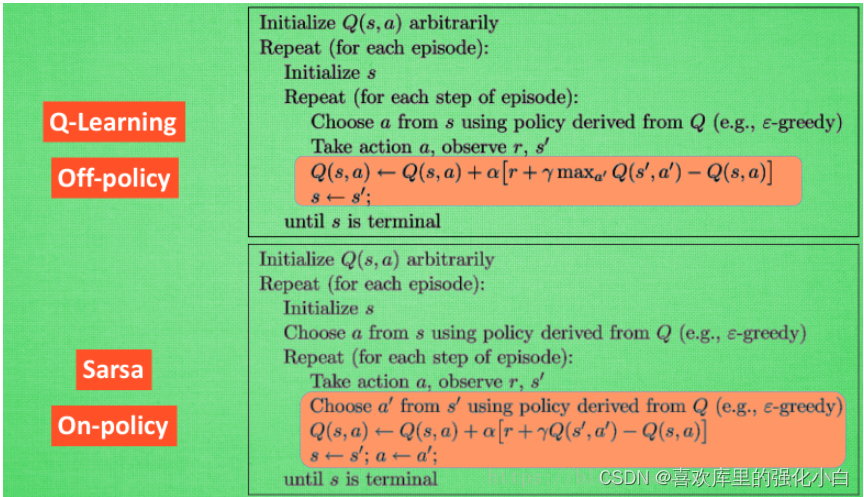

强化学习基础记录

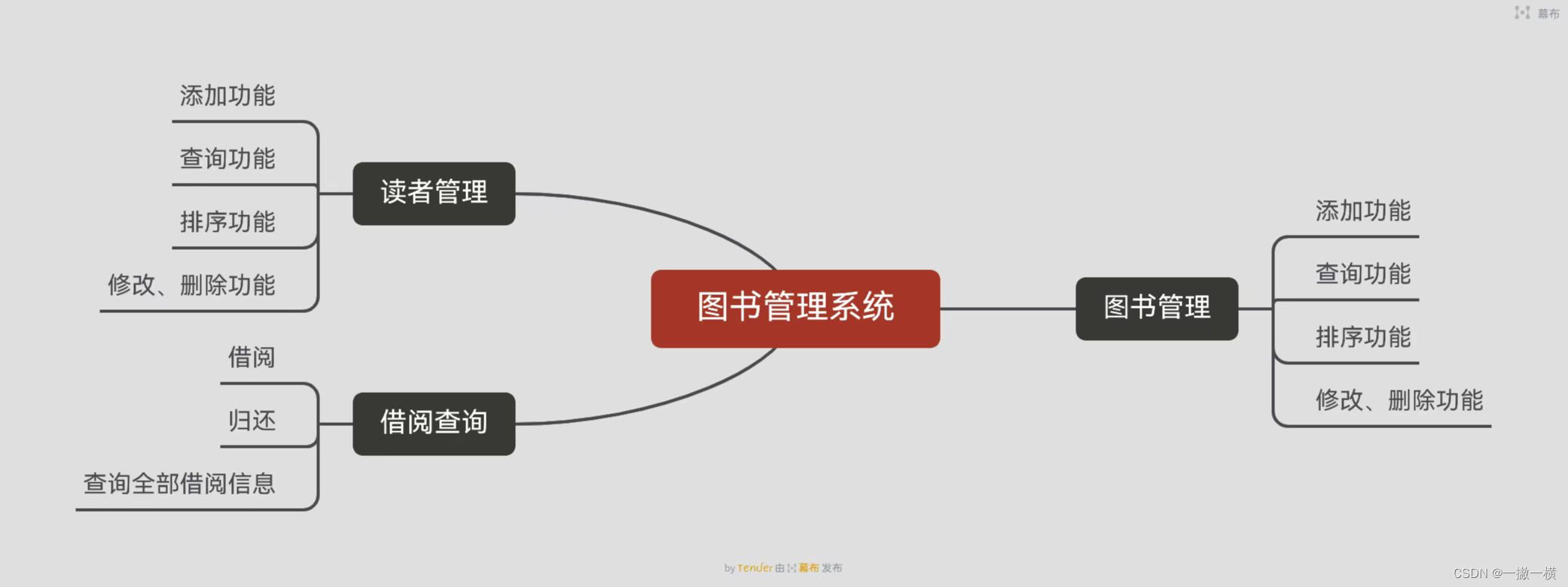

图书管理系统

Intranet information collection of Intranet penetration (I)

Mixlab unbounded community white paper officially released

Record once, modify password logic vulnerability actual combat

《英特尔 oneAPI—打开异构新纪元》

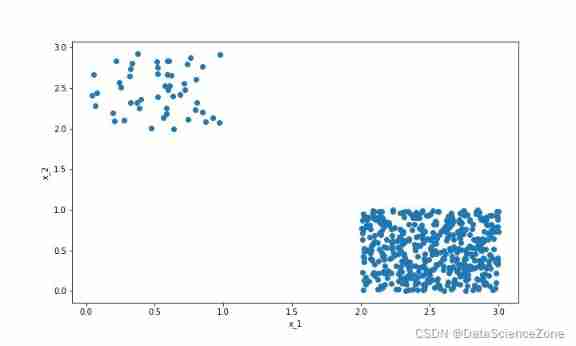

Data mining - a discussion on sample imbalance in classification problems

随机推荐

2022华中杯数学建模思路

Experiment five categories and objects

7-3 construction hash table (PTA program design)

中间件漏洞复现—apache

Brief introduction to XHR - basic use of XHR

实验七 常用类的使用(修正帖)

实验六 继承和多态

HackMyvm靶机系列(4)-vulny

强化学习基础记录

SRC mining ideas and methods

Low income from doing we media? 90% of people make mistakes in these three points

【VMware异常问题】问题分析&解决办法

内网渗透之内网信息收集(一)

sqqyw(淡然点图标系统)漏洞复现和74cms漏洞复现

Analysis of penetration test learning and actual combat stage

Library management system

Mixlab unbounded community white paper officially released

Ucos-iii learning records (11) - task management

7-5 staircase upgrade (PTA program design)

Intranet information collection of Intranet penetration (4)